# **SiC MOSFET Gate Drive Module**

## 碳化硅 MOSFET 门级驱动模块

### **AZ-SiC-EVB-GD**

### About this document

### Scope and purpose

This application note provides an overview of the evaluation board AZ-SiC-EVB-GD including its main features, key specification, pin assignments and mechanical dimensions.

AZ-SiC-EVB-GD is a complete SiC gate drive board including one optocoupler, one isolated power supply, one ultra-fast gate driver IC and EMI filter. In combination with control boards or equipment that are capable of output pulse width modulation (PWM) signal, the gate drive module features and demonstrates AZ Power's SiC MOSFETs for most power electronic applications.

The evaluation board AZ-SiC-EVB-GD was developed to support customers to speed up their product development during their initial hardware design with the isolated gate driving circuits of SiC power devices. The gate drive module is designed to support very high switching frequency operation of the SiC power device.

#### Intended audience

This application note is intended for power electronic engineers who wants to:

- 1, evaluate the performance of AZ Power's SiC power devices.

- 2, speed up product development during initial design with existing plug and play gate driving circuits.

## **Table of Contents**

| Ab | oout this document                                   | 1  |

|----|------------------------------------------------------|----|

| 1. | Safety Precautions                                   |    |

| 2. | Introduction                                         | 4  |

| 3. | Design features                                      | 5  |

| 2  | 3.1. Detailed Specifications of The Evaluation Board | 6  |

| 2  | 3.2. Functional Groups                               | 7  |

| 2  | 3.3. Interface Pin Assignment                        | 9  |

| 2  | 3.4. Schematic of The Gate Drive Board               | 10 |

| 3  | 3.5. PCB Layout of The Gate Drive Board              | 11 |

| 4. | Revision History                                     | 14 |

### 1. Safety Precautions

#### CAUTION: DURING THE OPERATION OF THE BOARD

DO NOT TOUCH THE EVALUATION BOARD WHEN IT IS POWERED BY ANY EXTERNAL POWER SOURCE. AND NEVER LEAVE THE EVALUATION BOARD UNATTENDED. THERE MAY HAVE VERY HIGH VOLTAGE PRESENTS ON THE EVALUATION BOARD.

#### CAUTION: BEFORE OPERATING THE BOARD

THE EVALUATION BOARD MAY PRESENTS HIGH VOLTAGE DURING OPERATION. THE BULKY CAPACITORS WILL BE CHARGED BY EXTERNAL POWER SUPPLIES. BEFORE OPERATING THE BOARD, WAIT FOR 10 SECONDS TO ALLOW THE POWER SUPPLIES TO FULLY CHARGE ALL THE CAPACITORS AND GET THE WHOLE SYSTEM READY FOR OPERATION.

#### CAUTION: AFTER POWERING DOWN THE BOARD

THE EVALUATION BOARD MAY PRESENTS HIGH VOLTAGE DURING OPERATION. THE BULKY CAPACITORS WILL BE CHARGED BY EXTERNAL POWER SUPPLIES. BEFORE WORKING ON THE EVALUATION BOARD, ALLOW THE BULKY CAPACITORS DISCHARGING FOR THREE MINUTES.

#### CAUTION: MEASUREMENT

WHEN MEASUREMENT EQUIPMENTS ARE ABOUT TO CONNECT TO THE EVALUATION BOARD, USE HIGH-VOLTAGE DIFFERENTIAL PROBES. IF PASSIVE PROBES ARE INTENDED TO BE USED FOR MEASUREMENT, CONSULT POWER ELECTRONICS PROFESSIONALS FIRST. DO NOT CONNECT THE PROBE WHEN THE EVALUATION BOARD IS POWERED BY POWER SOURCE.

#### CAUTION: CONSEQUENCES

PLEASE MAKE SURE THAT ALL MENTIONED SAFTY PROCEDURES ARE FOLLOWED WHEN USING THE EVALUATION BOARD. FAILED TO FOLLOW THE INSTRUCTIONS MAY LEAD TO:

- DEATH

- HEAT BURN

- SERIES INJURY

- ELECTROCUTION

- ELECTRICAL SHOCK

- ELECTRICAL BURN

#### 2. Introduction

The AZ-SiC-EVB-GD evaluation board is designed for general SiC power device driving purpose and evaluating the performance of AZ Power's SiC power devices.

The gate drive board is intended for use with any control boards or signal generators that are capable of outputting PWM signals. This evaluation board can be easily interfaced to appropriate mother board via interface pin connectors.

This evaluation board is designed as an easy-to-use plug & play module based on ultra-fast gate driver IC. The evaluation board includes a pin connector for connecting the 12V power supply and PWM signal input, a pin connector for connecting the gate & source of the MOSFET and an EMI filter.

The AZ-SiC-EVB-GD evaluation board is available via regular AZ Power distribution partners as well as on AZ Power's website. The features of this board are described in the design feature chapter of this document. The remaining paragraphs provide information enabling customers to copy, modify and qualify the design for production according to their own specific requirements.

Environmental conditions were considered in the design of the AZ-SiC-EVB-GD. The design was tested as described in this document, but not qualified in terms of safety requirements, manufacturing and operation over the entire operating temperature range or lifetime. The boards provided by AZ Power are subject to functional testing only.

Evaluation boards are not subject to the same procedures as regular products regarding returned material analysis, process change notification and product discontinuation. Evaluation boards are intended to be used under laboratory conditions and by trained specialists only.

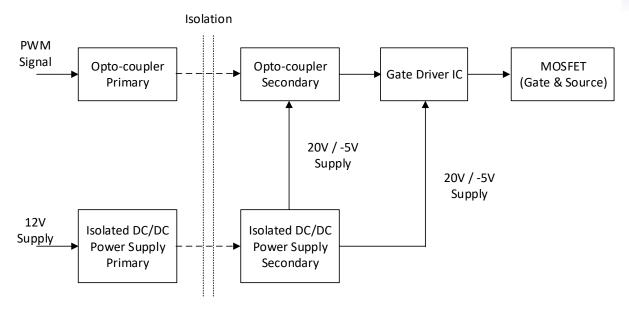

The block diagram of the AZ-SiC-EVB-GD is depicted in Figure 1. This evaluation board includes EMI filter, isolated DC/DC power supply, opto-coupler and ultra-fast gate driver IC. All the important control signals can be measured and observed via test points on the evaluation board. The hardware circuit relative to adjusting MOSFET turn-on/turn-off speed can be implemented through changing the resistance value of the gate resistors. The signal circuitry of the evaluation board is fully isolated from the power circuitry by using isolated power supply and optocoupler. The design can be easily upgraded to enhance the electrical insulation by replacing the present opto-coupler and the auxiliary power supply that meets the safety requirement.

Figure 1. The block diagram of the AZ-SiC-EVB-GD evaluation board

### 3. Design features

AZ-SiC-EVB-GD is a plug and play board for SiC MOSFET driving purpose, which is designed to evaluate the performance of AZ Power's SiC power devices. By connecting to an appropriate mother board that has compatible interface, it demonstrates AZ Power's silicon carbide power device technology.

The features of the evaluation board:

- Enhanced creepage between the primary side signal circuitry and the secondary side power circuitry on the printed circuit board (PCB)

- Insulation between power circuitry and signal circuitry

- Isolated DC/DC power supply with 5.2kV<sub>DC</sub> isolation rating

- Opto-coupler with 5kV<sub>RMS</sub> isolation rating

- Design based on ultra-fast gate driver IC

- Different resistance value for MOSFET turn-on and turn-off

- On-board EMI filter

- Measurement test points compatible with standard oscilloscope probes

- RoHS compliant

## 3.1. Detailed Specifications of The Evaluation Board

| Parameters                                   | Values                 | Comments                       |

|----------------------------------------------|------------------------|--------------------------------|

| Input                                        |                        |                                |

| Nominal Input Voltage                        | 12V                    |                                |

| Input Voltage Range                          | 10.8 VDC ~ 13.2<br>VDC |                                |

| Output                                       |                        |                                |

| Nominal Output DC Voltage                    | +20 VDC / -5 VDC       |                                |

| Peak Output Current – Source*                | 14 A                   | Ta=25°C                        |

| Peak Output Current – Sink*                  | 14 A                   | Ta=25°C                        |

| Output Power Per Gate (Average)              | 2 W                    |                                |

| Signals                                      |                        |                                |

| Recommended Input Logic Level - High         | 5 V ~ 12 V             |                                |

| Recommended Input Logic Level - Low          | 0 V                    |                                |

| Maximum Propagation Delay - Low to High      | 150 ns                 |                                |

| Maximum Propagation Delay -<br>High to Low   | 140 ns                 |                                |

| Input Threshold Voltage (High)               | 1.2 V ~ 2V             |                                |

| Input Threshold Voltage (Low)                | 0 V ~ 1V               |                                |

| Switching Frequency                          |                        |                                |

| Maximum Switching Frequency f <sub>max</sub> | 500 kHz                | This value is Device dependent |

| System Environment                           |                        |                                |

| Ambient Temperature                          | From 0 to 85°C         |                                |

| PCB Information                              |                        |                                |

| Material                                     | FR4                    |                                |

| Dimension                                    | 42.4 mm x 25 mm        |                                |

<sup>\*</sup>Actual peak output current will be affected by the turn-on and turn-off gate resistor values.

## 3.2. Functional Groups

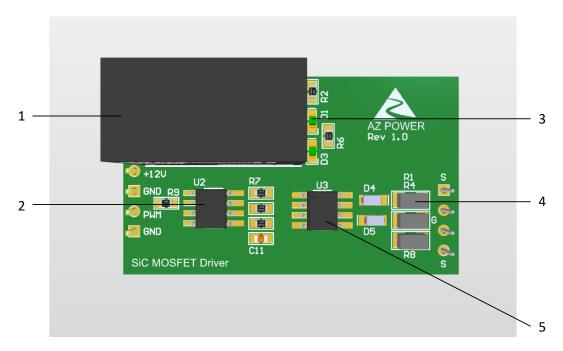

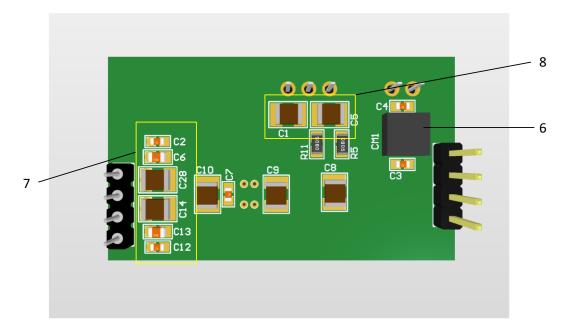

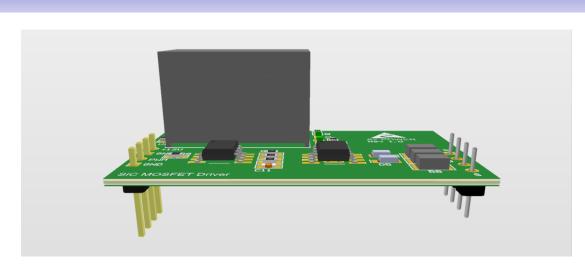

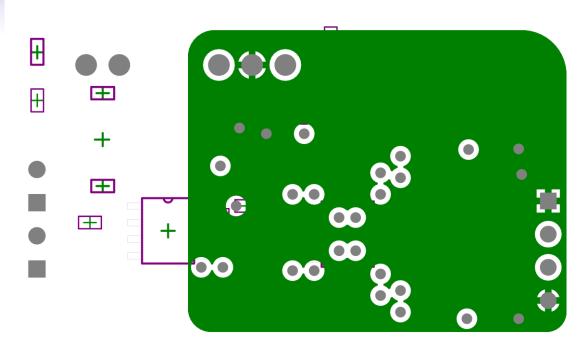

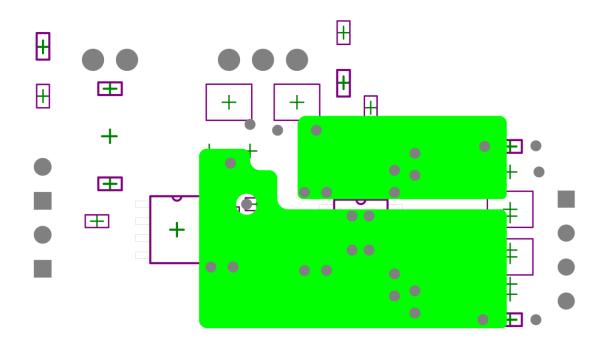

The next two figures illustrate the functional groups on the top and bottom side of the evaluation board. And a third figure shows the side view of the evaluation board. The functional groups are explained in Table 1.

Figure 2. The top view of the AZ-SiC-EVB-GD evaluation board

Figure 3. The bottom view of the AZ-SiC-EVB-GD evaluation board

Figure 4. The side view of the AZ-SiC-EVB-GD evaluation board

## **Table 1. Functional Groups of The Evaluation Board**

| Number | Functional Groups                               |  |

|--------|-------------------------------------------------|--|

| 1      | Isolated DC/DC power supply                     |  |

| 2      | Opto-coupler with 5kVRMS isolation rating       |  |

| 3      | Gate drive module power indicator               |  |

| 4      | Gate resistors                                  |  |

| 5      | Ultra-fast gate driver IC                       |  |

| 6      | Common mode EMI filter                          |  |

| 7      | Decoupling capacitors for gate driver IC        |  |

| 8      | Decoupling capacitors for isolated power supply |  |

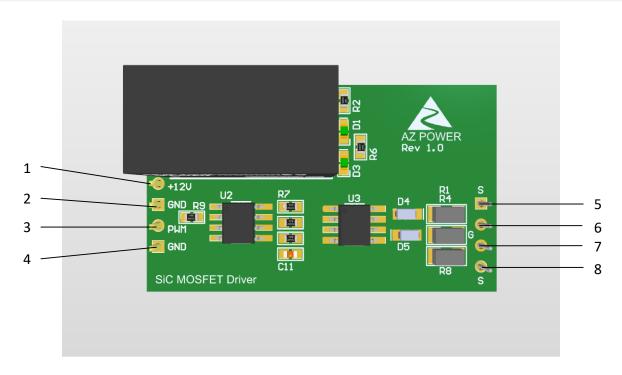

## 3.3. Interface Pin Assignment

Figure 5. The interface of the AZ-SiC-EVB-GD evaluation board

| Number | Pin              | Comments                  |

|--------|------------------|---------------------------|

| 1      | Power_Input_VDC+ | DC voltage input postive  |

| 2      | Power_Input_VDC- | DC voltage input negative |

| 3      | PWM_Input+       |                           |

| 4      | PWM_Input-       |                           |

| 6, 7   | Gate             | To MOSFET Gate            |

| 5, 8   | Source           | To MOSFET Source          |

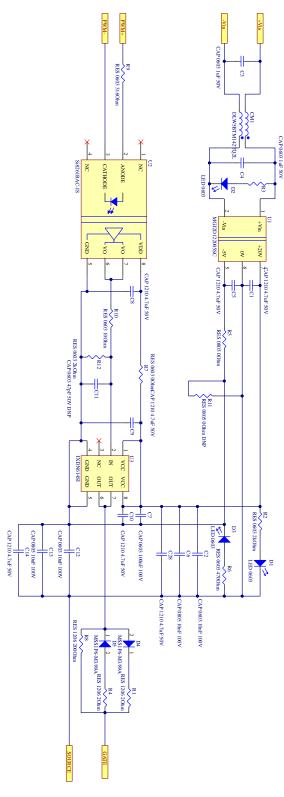

## 3.4. Schematic of The Gate Drive Board

Figure 6. The schematic of the AZ-SiC-EVB-GD evaluation board

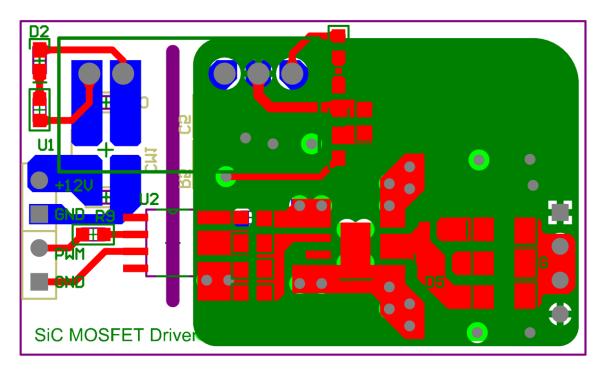

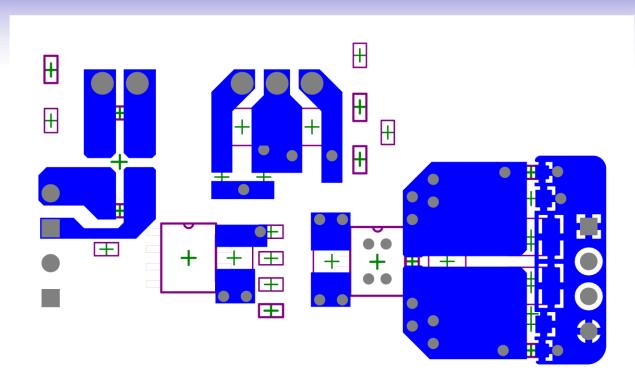

## 3.5. PCB Layout of The Gate Drive Board

Figure 7. The PCB layout of the AZ-SiC-EVB-GD evaluation board

Figure 8. The top layer PCB layout of the AZ-SiC-EVB-GD evaluation board

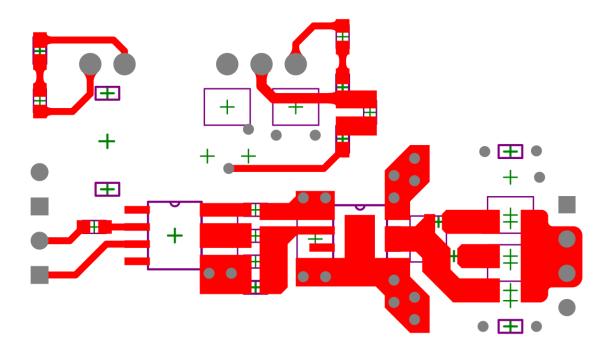

Figure 9. The 2<sup>nd</sup> layer PCB layout of the AZ-SiC-EVB-GD evaluation board

Figure 10. The 3<sup>rd</sup> layer PCB layout of the AZ-SiC-EVB-GD evaluation board

Figure 11. The bottom layer PCB layout of the AZ-SiC-EVB-GD evaluation board

### 4. Revision History

#### Major changes since last revision

| Document version | Description of change |  |  |

|------------------|-----------------------|--|--|

| 1.0              | Initial Release       |  |  |

|                  |                       |  |  |

|                  |                       |  |  |

This Product has not been designed or tested for use in, and is not intended for use in, applications implanted into the human body nor in applications in which failure of the product could lead to death, personal injury or property damage, including but not limited to equipment used in the operation of nuclear facilities, life-support machines, systems, or air-traffic control systems.

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, AZ Power Inc. disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

5601 W SLAUSON AVE 190 CULVER CITY, CA 90230 WWW.AZPE.COM

Information in this document may change without notice. All referenced product or service names and trademarks are the property of their respective owners. Copyright © 2020 AZ Power Inc. All rights reserved.