# SP6315: Dual Channel, 2.5 GHz – 2.7 GHz, Receiver Switch & LNA Front End Module

## **General Description**

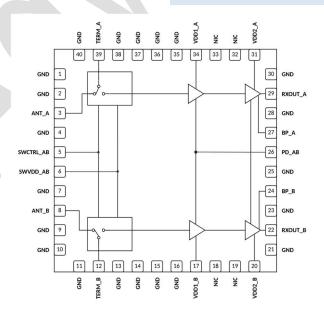

The SP6315 is a dual-channel, integrated radio frequency (RF), front-end multichip module designed for time division duplexing (TDD) applications that operate in the 5G n41 frequency band (2.496 GHz to 2.690 GHz). The SP6315 is configured in dual channels with a cascading two-stage low noise amplifier (LNA) and a high-power silicon single-pole, double-throw (SPDT) switch.

The device comes in a RoHS compliant, compact, 6 mm × 6 mm, 40-lead package.

#### **Applications**

- Wireless Infrastructure

- TDD massive multiple input and multiple output and active antenna systems

- TDD-Based communication systems

#### **Features**

- Integrated dual-channel RF front end with 2 stage LNA and high power SPDT switch along with On-chip bias and matching

- Single supply operation

- Gain

- o High gain mode: 36 dB typical at 2.6 GHz

- o Low gain mode: 16 dB typical at 2.6 GHz

- Low noise figure

- High gain mode: 1.0 dB typical at 2.6 GHz

- o Low gain mode: 1.0 dB typical at 2.6 GHz

- Low insertion loss: 0.5 dB typical at 2.6 GHz

- High Ch-Ch Isolation: -40dB typical in Rx mode

- High OIP3: 30dBm in Rx High Gain mode

- High power handling at T<sub>CASE</sub> = 105°C

- Full lifetime 5G NR average power (9 dB PAR):43 dBm

- Single event (<10 sec operation) 5G NR average power (9 dB PAR): 46 dBm

- Low supply current

- o High gain mode: 100 mA typical at 5 V (per channel)

- o Low gain mode: 46 mA typical at 5 V (per channel)

- o Power-down mode: 10 mA typical at 5 V (per channel)

- 6 mm x 6 mm, 40-lead LFCSP package.

**Figure 1 Functional Diagram**

## **Table of Contents**

| 1 Pin Configuration                              | 5  |

|--------------------------------------------------|----|

| 1.1 Pin Configuration Diagram                    | 5  |

| 1.2 Pin Description                              | 5  |

| 2 Electrical Specifications                      | 6  |

| 3 Detailed Functional Description                | 10 |

| 3.1 Functional Block Diagram                     | 10 |

| 3.2 Overview                                     | 10 |

| 3.2.1 Transmit Operation                         |    |

| 3.2.2 Receive Operation                          |    |

| 3.3 Biasing Sequence                             | 11 |

| 4 Package Information                            |    |

| 4.1 Package Marking and Dimensions               |    |

| 5 Ordering Information                           | 13 |

|                                                  |    |

| List of Tables                                   |    |

| Table 1 Pin Functions                            |    |

| Table 2 Absolute Maximum Ratings                 |    |

| Table 3 Electrical Specifications DC and Control | 7  |

| Table 4 Electrical Specifications at 2.6 GHz     | 8  |

| Table 5 Recommended Operating Conditions         | 9  |

| Table 6 Thermal Resistance                       |    |

| Table 7 Truth Table Signal Path                  | 11 |

| Table 8 Truth Table Operation                    |    |

| Table 9 SP6315 Ordering Information              | 13 |

## **List of Figures**

| -igure 1 Functional Diagram       | 1 |

|-----------------------------------|---|

| Figure 2 SP6315 Pin Configuration | 5 |

| Figure 3 Functional Block Diagram |   |

| Figure 4 Package Dimensions       |   |

# 1 Pin Configuration

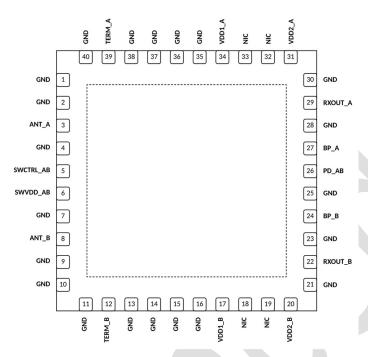

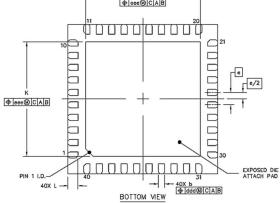

# **1.1 Pin Configuration Diagram**

Figure 2 SP6315 Pin Configuration

# 1.2 Pin Description

**Table 1 Pin Functions**

| PIN Name  | Pin No.                                                                                | Description                                                                             |

|-----------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| ANT_A     | 3                                                                                      | RF Input to Channel A.                                                                  |

| SWCTRL_AB | 5                                                                                      | Switch control for Channel A and B switch.                                              |

| SWVDD_AB  | 6                                                                                      | Supply voltage for Channel A and B switch.                                              |

| ANT_B     | 8                                                                                      | RF Input to Channel B.                                                                  |

| TERM_B    | 12                                                                                     | Termination Output for Channel B. This pin is the transmit path for Channel B.          |

| GND       | 1, 2, 4, 7, 9, 10, 11,<br>13, 14, 15, 16, 21, 23,<br>25, 28, 30, 35, 36, 37,<br>38, 40 | Ground                                                                                  |

| NIC       | 18,19,32, 33                                                                           | Not internally connected. It is recommended to connect NIC to the RF ground of the PCB. |

| VDD1_B    | 17                                                                                     | Supply voltage for Stage 1 LNA on Channel B.                                            |

| VDD2_B    | 20                                                                                     | Supply voltage for Stage 2 LNA on Channel B.                                            |

| RXOUT_B   | 22                                                                                     | RF Output. This pin is the receiver path for Channel B.                                 |

| BP_B      | 24                                                                                     | Bypass second stage LNA of Channel B.                                                   |

| PD_AB     | 26                                                                                     | Power-Down all stages of LNA for Channel A and B                                        |

| BP_A      | 27                                                                                     | Bypass second stage LNA of Channel A.                                                   |

| RXOUT_A   | 29                                                                                     | RF Output. This pin is the receiver path for Channel A.                                 |

| VDD2_A    | 31                                                                                     | Supply voltage for Stage 2 LNA on Channel A.                                            |

| VDD1_A    | 34                                                                                     | Supply voltage for Stage 1 LNA on Channel A.                                            |

| TERM_A    | 39                                                                                     | Termination Output for Channel A. This pin is the transmit path for Channel A.          |

| EPAD      | _                                                                                      | Exposed Pad. The exposed pad must be connected to RF or dc ground.                      |

www.spiritemi.com Page 5 of 14

SP-000793-DS6A

# **2 Electrical Specifications**

**Table 2 Absolute Maximum Ratings**

| Parameter                     |                                   | Symbol        | Min  | Max  | Units |

|-------------------------------|-----------------------------------|---------------|------|------|-------|

| Positive Supply Voltage       | VDD1_A, VDD1_B,<br>VDD2_A, VDD2_B |               | -0.3 | 5.5  | V     |

|                               | SWVDD_AB                          |               | -0.3 | 5.5  | V     |

| Digital Control Input Voltage | PD_AB, BP_A, BP_B                 |               | -0.3 | 5.5  | V     |

|                               | SWCTRL_AB                         |               | -0.3 | 3.6  | V     |

| DE Innut Dawer                | Transmit Input Power              | 5G NR<br>Peak |      | 55   | dBm   |

| RF Input Power                | Receive Input Power               | 5G NR<br>peak |      | 25   | dBm   |

| Tomporatura                   | Storage                           |               | -65  | 150  | °C    |

| Temperature                   | Reflow                            |               |      | 260  | °C    |

| Electrostatic Discharge       | Human Body Model                  | HBM           |      | 1000 | V     |

| Sensitivity (ESD)             | Charged Device Model              | CDM           |      | 500  | V     |

#### Notes:

- Operation of this device outside the parameter ranges given above may cause permanent damage.

- Operation of this device at the maximum operating ranges for extended periods of time may affect product reliability

www.spiritemi.com Page 6 of 14

SP-000793-DS6A

### **Table 3 Electrical Specifications DC and Control**

VDD1\_A, VDD1\_B, VDD2\_A, VDD2\_B, SWVDD\_AB = 5 V; SWCTRL\_AB = 0 V or 3.3V; BP\_A/B = 0 V or VDD1\_A/B; PD\_AB = 0 V or VDD1\_A/B; Testing Frequency: 2.6 GHz. Case Temperature (TCASE) = 25 °C, 50  $\Omega$  system, unless otherwise noted.

| Parameter           |                         | Conditions                              | Min  | Тур | Max  | Unit |

|---------------------|-------------------------|-----------------------------------------|------|-----|------|------|

|                     | High Gain               | VDD1_A/B and VDD2_A/B = 5 V per channel |      | 100 |      | mA   |

| Supply Current      | Low Gain                | VDD1_A/B and VDD2_A/B = 5 V per channel |      | 46  |      | mA   |

| (IDD)               | Power-Down<br>Mode      | VDD1_A/B and VDD2_A/B = 5 V per channel |      | 10  |      | mA   |

| TX Current (Switch) |                         | SWVDD_AB = 5 V                          |      | 4   |      | mA   |

|                     | SWCTRL_AB               | SWCTRL_AB = 3.3 V                       |      | 80  |      | uA   |

| Digital Currents    | PD_AB                   | PD_AB = 5 V                             |      | 240 |      | uA   |

|                     | BP_A/B                  | BP_A/B = 5 V per channel                |      | 120 |      | uA   |

| DIGITAL INPUT       |                         |                                         |      |     |      |      |

| CMCTDL AD           | Low (V <sub>IL</sub> )  |                                         | 0    |     | 0.63 | V    |

| SWCTRL_AB           | High (V <sub>IH</sub> ) |                                         | 1.17 |     | 3.3  | V    |

| PD_AB               | Low (VIL)               |                                         | 0    |     | 0.63 | V    |

|                     | High (V <sub>IH</sub> ) |                                         | 1.17 |     | VDD  | V    |

| BP_A/B              | Low (V <sub>IL</sub> )  |                                         | 0    |     | 0.63 | V    |

| DF_A/D              | High (V <sub>IH</sub> ) |                                         | 1.17 |     | VDD  | V    |

Notes:

www.spiritemi.com Page 7 of 14

SP-000793-DS6A

<sup>1.</sup> Measured at EPAD.

### Table 4 Electrical Specifications at 2.6 GHz

$VDD1\_A, VDD1\_B, VDD2\_A, VDD2\_B, SWVDD\_AB = 5 \ V; SWCTRL\_AB = 0 \ V \ or \ 3.3V; BP\_A/B = 0 \ V \ or \ VDD1\_A/B; PD\_AB = 0 \ V \ or \ VDD1\_A/B; Testing Frequency: 2.6 \ GHz. Case Temperature (<math>T_{CASE}$ ) = 25 °C, 50  $\Omega$  system, unless otherwise noted.

| Parameter                                      |                                                                | Conditions                                                                             | Min  | Тур | Max  | Units |

|------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------|------|-----|------|-------|

| Frequency Range                                |                                                                |                                                                                        | 2500 |     | 2700 | MHz   |

| CAINI[1]                                       | High Gain<br>Mode                                              | Describe an exetion                                                                    |      | 36  |      | dB    |

| GAIN <sup>[1]</sup>                            | Low Gain<br>Mode                                               | Receive operation                                                                      |      | 16  |      | dB    |

| CAIN EL ATNESSE                                | High Gain<br>Mode                                              | Receive operation in any 100 MHz                                                       |      | 0.2 |      | dB    |

| GAIN FLATNESS[1]                               | Low Gain<br>Mode                                               | bandwidth                                                                              |      | 0.2 |      | dB    |

| Noise Figure(NF) <sup>[1]</sup>                | High Gain<br>Mode<br>Low Gain                                  | - Receive operation                                                                    |      | 1.0 |      | dB    |

|                                                | Mode                                                           |                                                                                        |      | 1.0 |      | dB    |

| Output Third-Order Intercept Point             | High Gain<br>Mode                                              | Receive operation, two-tone<br>output power = +3 dBm per tone<br>at 1 MHz tone spacing |      | 30  |      | dBm   |

| (OIP3) <sup>[1]</sup>                          | Low Gain<br>Mode                                               | Receive operation, two-tone output power = 0 dBm per tone at 1 MHz tone spacing        |      | 25  |      | dBm   |

| Output 1 dB<br>Compression                     | High Gain<br>Mode                                              | Receive operation                                                                      |      | 17  |      | dBm   |

| (OP1dB)                                        | Low Gain<br>Mode                                               | Treceive operation                                                                     |      | 12  |      | dBm   |

| Insertion Loss <sup>[1]</sup>                  |                                                                | Transmit operation                                                                     |      | 0.5 |      | dB    |

| Channel to<br>Channel Isolation <sup>[1]</sup> | Between RXOUT_A AND RXOUT_B                                    | Receive operation                                                                      |      | -40 |      | dB    |

| Switch Isolation                               | ANT_A TO<br>TERM_A<br>AND ANT_B<br>TO<br>TERM_B <sup>[1]</sup> | Receive operation, PD_AB = 0 V                                                         |      | -15 |      | dB    |

| Input return loss                              |                                                                | Receive operation, High Gain Mode                                                      |      | -20 |      | dB    |

| Output return loss                             |                                                                | Receive operation, High Gain Mode                                                      |      | -15 |      | dB    |

| Input return loss                              |                                                                | Receive operation, Low Gain Mode                                                       |      | -20 |      | dB    |

| Output return loss                             |                                                                | Receive operation, Low Gain Mode                                                       |      | -15 |      | dB    |

| Input return loss                              |                                                                | Transmit operation                                                                     |      | -20 |      | dB    |

| Output return loss                             |                                                                | Transmit operation                                                                     |      | -15 |      | dB    |

| Switching time                                 |                                                                | 50% control voltage to 90%, 10% of RF, Tx → Rx or Rx → Tx transition                   |      | 700 |      | ns    |

Notes:

www.spiritemi.com Page 8 of 14

SP-000793-DS6A

<sup>1.</sup> Refer Truth Tables, Table 7 and Table 8

## **Table 5 Recommended Operating Conditions**

| Parameter                                    | Conditions                           | Min  | Тур | Max  | Unit  |

|----------------------------------------------|--------------------------------------|------|-----|------|-------|

| Bias Voltage Range                           | VDD1_A/B, VDD2_A/B, SWVDD_AB         | 4.75 | 5   | 5.25 | V     |

| Control Voltage Range                        | PD_AB, BP_A/B                        | 0    |     | VDD  | V     |

| Control Voltage Nange                        | SWCTRL_AB                            | 0    |     | 3.3  | V     |

|                                              | SWCTRL_AB = 3.3 V, PD_AB = 5 V,      |      |     |      |       |

|                                              | BP_A/B = 0 V,                        |      |     |      |       |

| RF Input Power at ANT_A, ANT_B               | T <sub>CASE</sub> = 105°C            |      |     |      |       |

| KF IIIput Fower at ANT_A, ANT_B              | 9 dB PAR 5G NR full lifetime average |      |     | 43   | dBm   |

|                                              | 9 dB PAR 5G NR single event          |      |     | 46   | dBm   |

|                                              | (<10 sec) average                    |      |     | 40   | ubili |

| Case Temperature Range T <sub>CASE</sub> [2] |                                      | -40  |     | +105 | °C    |

| Junction Temperature at Maximum              | Receive operation <sup>[1]</sup>     |      |     | TBD  | °C    |

| T <sub>CASE</sub> <sup>[2]</sup>             | Transmit operation <sup>[1]</sup>    |      |     | TBD  | °C    |

#### Notes:

- 1. Refer Truth Tables, Table 7 and Table 8

- 2. Measured EPAD

#### **Table 6 Thermal Resistance**

| Package Type |                             | θJC  | Unit |

|--------------|-----------------------------|------|------|

| CP-40-15     | High Gain and Low Gain Mode | 12.5 | °C/W |

| 01 -40-19    | Power-Down Mode             | 25   | °C/W |

www.spiritemi.com Page 9 of 14

sp-000793-DS6A

## 3 Detailed Functional Description

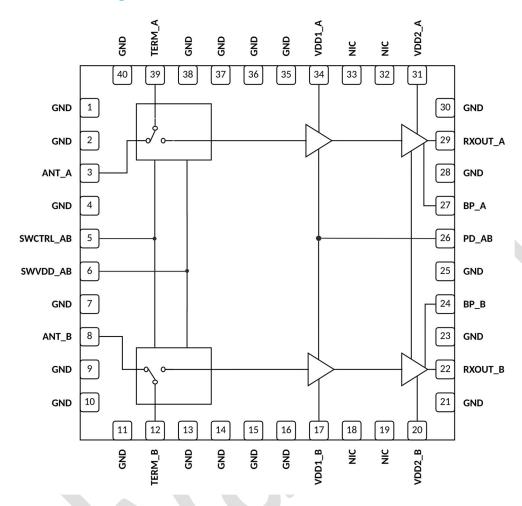

## 3.1 Functional Block Diagram

Figure 3 Functional Block Diagram

#### 3.2 Overview

The SP6315 is a dual-channel, integrated radio frequency (RF), front-end multichip module designed for time division duplexing (TDD) applications that operate in the 5G n41 frequency band (2.496 GHz to 2.690 GHz). The SP6315 is configured in dual channels with a cascading two-stage low noise amplifier (LNA) and a high-power silicon single-pole, double-throw (SPDT) switch.

In Rx high gain mode, the cascaded two-stage LNA and switch offer a low noise figure (NF) of 1.0 dB, a high gain of 36 dB at 2.6 GHz, with current consumption of 100 mA per channel. In Rx low gain mode, one stage of the two-stage LNA is in bypass, providing 16 dB of gain at a lower current of 46 mA per channel. In power-down mode, the LNAs are turned off and the device draws 10 mA per channel.

In transmit operation, when RF inputs are connected to a termination pin (TERM\_A or TERM\_B), the switch provides a low insertion loss of 0.5 dB at 2.6 GHz and handles an 5G NR signal with an average power (9 dB peak to average ratio, (PAR)) of 43 dBm for full lifetime operation and 46 dBm for single event (<10 sec). There is also an option of keeping the RX LNAs operational in the TX mode.

The SP6315 requires a positive supply voltage applied to VDD1\_A, VDD2\_A, VDD1\_B, VDD2\_B, SWVDD\_AB. Correct decoupling is required on the power supply lines for optimum noise performance, see application diagram for details.

www.spiritemi.com Page 10 of 14

#### 3.2.1 Transmit Operation

The SP6315 supports transmit operations when 3.3 V is applied to SWCTRL\_AB. In transmit operation, when an RF input is applied to ANT\_A and ANT\_B, the signal path connection is from ANT\_A to TERM\_A and from ANT\_B to TERM\_B.

The SP6315 also supports receive LNA being powered up in transmit operation. This is achieved by applying 0 V to PD AB.

#### 3.2.2 Receive Operation

In receive operation, ANT\_A is connected to RXOUT\_A and ANT\_B to RXOUT\_B. SP6315 supports high gain mode, low gain mode, power-down high isolation mode, and power-down low isolation mode in receive operation, as detailed in Table 8

When 0 V is applied to PD\_AB, the LNA is powered up and the user can select high gain mode or low gain mode. To select high gain mode, apply 0 V to BP\_A or BP\_B. To select low gain mode, apply 5 V to BP\_A or BP\_B.

When 5 V is applied to PD\_AB, the SP6315 enters power-down mode. To select power-down high isolation mode, apply 0 V to BP\_A or BP\_B. To select power-down low isolation mode, apply 5 V to BP\_A or BP\_B.

#### 3.3 Biasing Sequence

To Bias up the SP6315, perform the following steps.

- Connect GND to ground.

- 2. Bias up VDD1\_A, VDD2\_A, VDD1\_B, VDD2\_B, SWVDD\_AB.

- 3. Bias up SWCTRL AB.

- 4. Bias up PD\_AB.

- 5. Bias up BP\_A and BP\_B.

- 6. Apply an RF input signal.

To Bias down, perform these steps in the reverse order

#### **Table 7 Truth Table Signal Path**

| SWCTRL AB | Signal Path Select                                  |     |  |  |

|-----------|-----------------------------------------------------|-----|--|--|

| SWCTRL_AB | Transmit Operation <sup>[1]</sup> Receive Operation |     |  |  |

| Low       | Off                                                 | On  |  |  |

| High      | On                                                  | Off |  |  |

Notes:

#### **Table 8 Truth Table Operation**

| Operation |                         | PD_AB  | BP_A, BP_B | Signal Path       |

|-----------|-------------------------|--------|------------|-------------------|

|           | High Gain Mode          | Low    | Low        |                   |

|           | Low Gain Mode           | Low    | High       |                   |

| Receive   | Power Down High         | High   | Low        | ANT_A to RFOUT_A, |

| operation | Isolation Mode          | Tilgii | LOW        | ANT_B to RFOUT_B  |

|           | Power Down Low          | High   | High       |                   |

|           | Isolation Mode          | Tilgii | Tilgii     |                   |

| Transmit  | Insertion Loss Mode     | Hiah   | Low        | ANT_A to TERM_A,  |

| Operation | IIISEI IIOII LOSS MIOUE | riigii | LOW        | ANT_B to TERM_B   |

www.spiritemi.com Page 11 of 14

<sup>1.</sup> See the signal path descriptions in Table 8

# **4 Package Information**

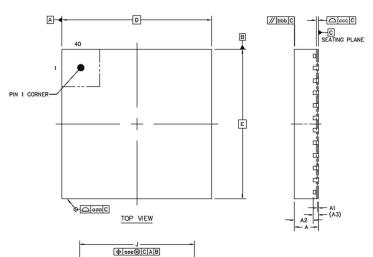

# **4.1 Package Marking and Dimensions**

|                        |   | SYMBOL | MIN          | NOM       | MAX |

|------------------------|---|--------|--------------|-----------|-----|

| TOTAL THICKNESS        |   | Α      | 0.9 0.95 1   |           |     |

| STAND OFF              |   | A1     | 0 0.035 0.05 |           |     |

| MOLD THICKNESS         |   | A2     |              | 0.75      |     |

| L/F THICKNESS          |   | A3     |              | 0.203 REF |     |

| LEAD MIDTH             |   | b      | 0.2          | 0.25      | 0.3 |

| BODY SIZE              | х | D      |              | 6 BS      | C   |

| BOUT SIZE              | Y | E      |              | 6 BS      | С   |

| LEAD PITCH             |   | e      |              | 0.5 BSC   |     |

| EP SIZE                | X | J      | 4.5          | 4.6       | 4.7 |

| EF 3126                | Y | K      | 4.5          | 4.6       | 4.7 |

| LEAD LENGTH            |   | L      | 0.3          | 0.4       | 0.5 |

| PACKAGE EDGE TOLERANCE |   | aaa    |              | 0.1       |     |

| MOLD FLATNESS          |   | bbb    |              | 0.1       |     |

| COPLANARITY            |   | ccc    |              | 0.08      |     |

| LEAD OFFSET            |   | ddd    |              | 0.1       |     |

| EXPOSED PAD OFFSE      | T | eee    |              | 0.1       |     |

|                        |   |        |              |           |     |

|                        |   |        |              |           |     |

|                        |   |        |              |           |     |

|                        |   |        |              |           |     |

|                        |   |        |              |           |     |

|                        |   |        |              |           |     |

**Figure 4 Package Dimensions**

www.spiritemi.com Page 12 of 14

SP-000793-DS6A

# **5 Ordering Information**

## Table 9 SP6315 Ordering Information

| Ordering Part Number (OPN) | Marking | Package information | Temperature Range |

|----------------------------|---------|---------------------|-------------------|

| SP6315-QMR                 | SP6315  | 40 QFN              | -40°C to 105°C    |

www.spiritemi.com Page 13 of 14

SP-000793-DS6A

#### IMPORTANT NOTICE AND DISCLAIMER

SPIRIT SEMICONDUCTOR PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Spirit Semiconductor products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Spirit Semiconductor grants you permission to use these resources only for development of an application that uses Spirit Semiconductor products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Spirit Semiconductor intellectual property or to any third party intellectual property. Spirit Semiconductor disclaims responsibility for, and you will fully indemnify Spirit Semiconductor and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Spirit Semiconductor products are provided only subject to Spirit Semiconductor Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Spirit Semiconductor resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

#### **Contact Information**

For more information visit www.spiritsemiconductor.com

For sales related information please send an email to sales@spiritsemi.co.uk

#### **Trademarks**

Spirit Semiconductor and Spirit Semiconductor Logo are trademarks of Semiconductor Limited. All referenced brands, product names, service names and trademarks are the property of their respective owners.

www.spiritemi.com Page 14 of 14