# CMx-SLx Technical Reference

PCI/104-Express Single Board Computer with 6th Generation Intel® Core™ Processor

Manual Rev.: 1.4 Revision Date: January 25, 2022 Part Number: 50M-00063-1040

# Leading EDGE COMPUTING

# Preface

#### Disclaimer

Information in this document is provided in connection with ADLINK products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in ADLINK's Terms and Conditions of Sale for such products, ADLINK assumes no liability whatsoever, and ADLINK disclaims any express or implied warranty, relating to sale and/or use of ADLINK products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. If you intend to use ADLINK products in or as medical devices, you are solely responsible for all required regulatory compliance, including, without limitation, Title 21 of the CFR (US), Directive 2007/47/EC (EU), and ISO 13485 & 14971, if any. ADLINK may make changes to specifications and product descriptions at any time, without notice.

#### Trademarks

Product names mentioned herein are used for identification purposes only and may be trademarks and/or registered trademarks of their respective companies.

| Revision | Date       | Description of Change(s)                                                                                                                                                                                                                                                                                                    |  |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1.00     | 2017-07-17 | Initial Release                                                                                                                                                                                                                                                                                                             |  |

| 1.1      | 2018-04-20 | Added heat spreader installation section to Chapter 1; re-ordered pin<br>sequence in Table 3-4 on page 31; re-labelled signals in Table 3-3 on<br>page 31 to USB0 and USB1; added BMC thermal pad to the heat<br>spreader photos in Chapter 1; added notes concerning +5V-only power<br>to Power Interface (J24) on page 37 |  |

| 1.2      | 2020-04-08 | Correct specifications, Ethernet connector pin definitions (H11)                                                                                                                                                                                                                                                            |  |

| 1.3      | 2021-02-03 | Add French safety warnings                                                                                                                                                                                                                                                                                                  |  |

| 1.4      | 2022-01-25 | Update CPU, memory, SSD specs                                                                                                                                                                                                                                                                                               |  |

#### **Revision History**

#### Copyright © 2017, 2018, 2020, 2021, 2022 ADLINK Technology, Incorporated

www.adlinktech.com

This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of the manufacturer.

#### Audience

This manual provides reference only for computer design engineers, including but not limited to hardware and software designers and applications engineers. ADLINK Technology, Inc. assumes you are qualified to design and implement prototype computer equipment.

#### **Environmental Responsibility**

ADLINK is committed to fulfill its social responsibility to global environmental preservation through compliance with the European Union's Restriction of Hazardous Substances (RoHS) directive and Waste Electrical and Electronic Equipment (WEEE) directive. Environmental protection is a top priority for ADLINK. We have enforced measures to ensure that our products, manufacturing processes, components, and raw materials have as little impact on the environment as possible. When products are at their end of life, our customers are encouraged to dispose of them in accordance with the product disposal and/or recovery programs prescribed by their nation or company.

Battery Labels (for products with battery)

#### **California Proposition 65 Warning**

**WARNING:** This product can expose you to chemicals including acrylamide, arsenic, benzene, cadmium, Tris(1,3-dichloro-2-propyl)phosphate (TDCPP), 1,4-Dioxane, formaldehyde, lead, DEHP, styrene, DINP, BBP, PVC, and vinyl materials, which are known to the State of California to cause cancer, and acrylamide, benzene, cadmium, lead, mercury, phthalates, toluene, DEHP, DIDP, DnHP, DBP, BBP, PVC, and vinyl materials, which are known to the State of California to cause birth defects or other reproductive harm. For more information go to www.P65Warnings.ca.gov.

**AVERTISSEMENT:** Ce produit peut vous exposer à des produits chimiques tels que l'acrylamide, l'arsenic, le benzène, le cadmium, le phosphate de tris (1,3-dichloro-2-propyle) (TDCPP), le 1,4-dioxane, le formaldéhyde, le plomb, le DEHP, le styrène, le DINP, BBP, PVC et matériaux en vinyle, qui sont connus dans l'État de Californie pour causer le cancer, et acrylamide, benzène, cadmium, plomb, mercure, phtalates, toluène, DEHP, DIDP, DnHP, DBP, BBP, PVC et vinyle matériaux, qui sont connus de l'État de Californie pour causer des anomalies congénitales ou d'autres troubles de la reproduction. Pour plus d'informations, visitez le site www.P65Warnings.ca.gov.

#### Conventions

The following conventions may be used throughout this manual, denoting special levels of information.

This information adds clarity or specifics to text and illustrations.

This information indicates the possibility of *minor* physical injury, component damage, data loss, and/or program corruption.

CAUTION: Ces informations indiquent la possibilité de blessures physiques mineures, de dommages aux composants, de perte de données mise en garde et / ou de corruption de programme.

This information warns of possible *serious* physical injury, component damage, data loss, and/or program corruption.

Ces informations mettent en garde contre d'éventuelles blessures physiques **graves**, des dommages aux composants, une perte de données et / ou une corruption du programme.

#### **Important Safety Instructions**

For user safety, please read and follow all **Instructions**, **WARNINGs**, **CAUTIONs**, and **NOTEs** marked in this manual and on the associated equipment before handling/operating the equipment.

- Read these safety instructions carefully.

- Keep this manual for future reference.

- Read the specifications section of this manual for detailed information on the operating environment of this equipment.

- Turn off power and unplug any power cords/cables when installing/mounting or un-installing/removing equipment.

- To avoid electrical shock and/or damage to equipment:

- ▷ Keep equipment away from water or liquid sources;

- ▷ Keep equipment away from high heat or high humidity;

- ▷ Keep equipment properly ventilated (do not block or cover ventilation openings);

- ▷ Make sure to use recommended voltage and power source settings;

- Always install and operate equipment near an easily accessible electrical socketoutlet;

- Secure the power cord (do not place any object on/over the power cord);

- Only install/attach and operate equipment on stable surfaces and/or recommended mountings; and,

- If the equipment will not be used for long periods of time, turn off the power source and unplug the equipment.

# **Table of Contents**

| Pr                           | eface      | •••••            |                                                             | ii |

|------------------------------|------------|------------------|-------------------------------------------------------------|----|

| 1                            | Prod       | uct              | Overview                                                    | 1  |

|                              | 1.1        | Des              | cription                                                    | 1  |

| 1.2 About this Manual        |            |                  | ut this Manual                                              | 1  |

| 1.3 Features                 |            |                  | ures                                                        | 2  |

|                              | 1.4        | Orde             | ering Information                                           | 5  |

|                              | 1.5        | Bloc             | k Diagram                                                   | 6  |

|                              | 1.6        | Spe              | cifications                                                 | 7  |

|                              | 1.6        | 6.1              | Physical                                                    | 7  |

|                              | 1.6        | 6.2              | Mechanical                                                  | 7  |

|                              | 1.6        | 6.3              | Electrical                                                  | 8  |

|                              | 1.6        | ò.4              | Power                                                       | 8  |

|                              | 1.6        | 6.5              | Environmental                                               | 9  |

|                              | 1.6        |                  | Thermal/Cooling Requirements                                |    |

|                              | 1.7        | Gett             | ing Started                                                 | 13 |

| 2                            | Hard       | ware             |                                                             | 17 |

| 2                            | 2.1        |                  | or IC Definitions and Locations                             |    |

|                              | 2.2        | -                | der and Connector Definitions and Locations                 |    |

|                              | 2.3        |                  | per Header Definitions                                      |    |

|                              | 2.4        |                  | ponent Features                                             |    |

|                              | 2.4        |                  | CPU                                                         |    |

|                              | 2.4        |                  | PCH                                                         |    |

|                              | 2.4        |                  | SDRAM                                                       |    |

|                              | 2.4        |                  | Gigabit Ethernet PHY Transceiver (I219 - Supporting GLAN1)  |    |

|                              | 2.4        |                  | Gigabit Ethernet Controller (I210 - Supporting GLAN2)       |    |

|                              | 2.4        |                  | SSD (Solid State Drive)                                     |    |

|                              | 2.4        |                  | BMC                                                         |    |

|                              | 2.4        | 1.8              | LM73 Temperature Sensor                                     |    |

|                              | 2.4        |                  | PTN3460I eDP-to-LVDS Converter                              |    |

|                              |            |                  | SMBus Slave Addresses                                       |    |

|                              | 2.5        |                  | idard Connectors                                            |    |

|                              | 2.5        |                  | Micro HDMI (J8)                                             |    |

| 2.5.2 Mini DisplayPort (J17) |            | 5.2              | Mini DisplayPort (J17)                                      |    |

|                              |            | USB Type-C (J28) |                                                             |    |

| •                            |            |                  |                                                             |    |

| 3                            |            |                  |                                                             |    |

|                              | 3.1        |                  | al Interfaces (H16 and J18)                                 |    |

|                              | 3.2        |                  | 3 2.0 Interface (H15 and J25)                               |    |

|                              | 3.3        |                  | ernet (H11 and J14)                                         |    |

|                              | 3.4<br>2.5 |                  | o (J8 [Micro HDMI], J17 [Mini DisplayPort], and J23 [LVDS]) |    |

| 3.5 Pov                      |            | FOW              | er Interface (J24)                                          |    |

|   | 3.6                            | Use    | GPIO Interface (J26 and J27)          | . 38 |

|---|--------------------------------|--------|---------------------------------------|------|

|   | 3.7                            | I2C    | / SMBus Interface (J31)               | . 38 |

|   | 3.8                            | Utilit | y Interface (J21)                     | . 39 |

|   | 3.8                            | 3.1    | Power Button                          | . 39 |

|   | 3.8                            | 3.2    | Reset Switch                          | . 39 |

|   | 3.8                            | 3.3    | Speaker                               | . 39 |

|   | 3.9                            | Syst   | em Fan (J22)                          | . 40 |

|   | 3.10                           |        | ery (J12)                             |      |

|   | 3.11                           | Exte   | rnal LEDs - Ethernet (J2 and J3)      | . 41 |

| 4 | Utilit                         | ies .  |                                       | 43   |

|   | 4.1                            | BIO    | S Setup                               | . 43 |

|   | 4.1                            | 1.1    | Menu Structure                        | . 43 |

|   | 4.1                            | 1.2    | Starting the BIOS Setup Utility       | . 44 |

|   | 4.1                            | 1.3    | Main Menu                             | . 44 |

|   | 4.1                            | 1.4    | Advanced Menu                         | 49   |

|   | 4.1                            | 1.5    | Boot Menu                             | . 68 |

|   | 4.1                            | 1.6    | Security Menu                         | . 69 |

|   | 4.1                            | 1.7    | Save & Exit Menu                      |      |

|   | 4.2                            | BIO    | S Checkpoints, Beep Codes             |      |

|   |                                | 2.1    | Checkpoints and Beep Codes Definition |      |

|   | 4.2                            | 2.2    | Aptio Boot Flow                       |      |

|   | 4.2                            | 2.3    | Viewing BIOS Checkpoints              |      |

|   |                                | 2.4    | Status Code Ranges                    |      |

|   |                                | 2.5    | Standard Status Codes                 |      |

|   | 4.3                            |        | IA Functions                          |      |

|   |                                | 3.1    | Board Specific SEMA functions         |      |

|   | 4.4                            |        | Time Clock (RTC)                      |      |

|   | 4.5                            | •      | s! Jumper (BIOS Recovery)             |      |

|   | 4.6                            |        | al Console                            |      |

|   | 4.7                            |        | al Console BIOS Setup                 |      |

|   | 4.8                            |        | (Serial) Cable                        |      |

|   | 4.9                            | Wate   | chdog Timer                           | . 83 |

| A | opend                          | lix A  | System Resource                       | .85  |

| A | Appendix B Technical Support89 |        |                                       |      |

# 1 Product Overview

# 1.1 Description

The CMx-SLx is a PCI/104-Express Type 1 Single Board Computer (SBC) featuring the 64-bit 6th Generation Intel® Core™ i3 and Intel® Xeon® E3 processor (formerly "Skylake-H"), supported by the Intel® CM236 Chipset. The CMx-SLx is specifically designed for customers who need high-level processing and graphics performance in a long product life solution.

The CMx-SLx Intel processor supports Intel Hyper-Threading Technology and up to 16GB of soldered ECC DDR4 memory at 1866/2133 to achieve optimum overall performance.

Integrated Intel® Generation 9 Graphics includes features such as OpenGL 5.x, OpenCL 2.x, DirectX 2015, DirectX 12, Intel® Clear Video HD Technology, Advanced Scheduler 2.0, 1.0, XPDM support, and DirectX Video Acceleration (DXVA) support for full HEVC/VP8/VP9/AVC/ MPEG2 hardware codec. Graphics outputs include single-channel 18/24-bit LVDS (eDP x4 lanes optional) and three DDI ports supporting HDMI/DVI/DisplayPort. The CMx-SLx is specifically designed for customers with high-performance processing graphics requirements who want to outsource the custom core logic of their systems for reduced development time.

The CMx-SLx features one mini DisplayPort (DDI1), one micro HDMI port (DDI2), and one single channel 18/24-bit LVDS port (eDP), two Gigabit Ethernet ports, four USB 2.0 ports, two COM ports, eight GPIOs (from BMC), two SATA 6Gb/s ports, and one onboard SATA SLC SSD up to 32GB capacity. The module is equipped with an SPI AMI EFI BIOS with CMOS backup, supporting embedded features such as fail safe BIOS, remote console, CMOS backup, hardware monitor, and watchdog timer.

The CMx-SLx is capable of working in the temperature ranges of  $0^{\circ}$ C to  $60^{\circ}$ C (standard) and  $-40^{\circ}$ C to  $85^{\circ}$ C (extended).

# **1.2** About this Manual

This manual presents the supported features of the CMx-SLx Single Board Computer (SBC). After reviewing this document you should understand the following features of the CMx-SLx.

- Board Features

- ► Functional Block Diagram

- ► Major Component (IC) Locations and Descriptions

- ▶ Header, Connector, and Socket Locations and Descriptions

- ► Specifications

- ► Interface Signal Definitions

- Board Utilities

# 1.3 Features

- ► CPU

- b 6th Gen Intel® Core™ i3 and Intel® Xeon® E3 processor (formerly "Skylake-H")

Intel® Core™ i3-6102E 1.9GHz (no Turbo), 25W (2C/GT2)

- Intel® Core™ i3-6100E 2.7GHz (no Turbo), 35W (2C/GT2)

- Intel® Xeon® E3-1505L v5 2.0/2.8GHz (Turbo), 25W (4C/GT2)

- > DMI (Direct Media Interface) with 8 GT/s point-to-point interface to the chipset

- Enhanced Intel SpeedStep® Technology (EIST)

- ▷ Hyper-Threading Technology

- ▷ Up to 3MB on-die L2 cache

- ▷ 3D graphics engine

- > Dual-channel DDR4 memory controller (only one channel connected on board)

- Chipset

- ▷ Intel CM236 PCH with ECC memory support

- ▷ Gen3 PCIe support

- ▷ 8 GT/s transfer rate

- $\triangleright$  Sensor-enhanced

- ▷ ECC memory support

- Memory

- ▷ Up to 16GB of ECC DDR4 soldered, on-board memory

- $\,\triangleright\,\,$  Eight non-ECC and one ECC, unbuffered SDRAM chips

- ▷ Single-channel, 1866/2133MHz

- > Double Data Rate interface

- ▷ 64-bit data bus

- $\triangleright$  Non-ECC option

- ► BIOS

- ▷ AMI EFI BIOS with CMOS backup of 8MB

- ▷ SPI interface

- ▷ Intel AMT 11.0 support for Xeon processors

- ▷ SEMA fail-safe

- Expansion Buses

- ▷ PCI bus version 2.3 at 33MHz

- ▷ PCIe bus version 2.0 at 100MHz

- SATA Interface

- ▷ Two SATA 6Gb/s ports from the CM236 PCH

- ▷ eSATA capable

- ▷ Up to 6Gb/second data transfer rate

- Independent DMA operation

- ▷ Native Command Queuing

- Auto Activate for DMA

- ▷ Hot Plug features

- $\,\triangleright\,\,$  Two standard SATA 6Gb/s connectors

- > One SATA 3Gb/s port dedicated for the onboard SSD

- Serial Interface

- > Two buffered serial ports (COM1-2) with full handshaking

- ▷ Two 10-pin headers

- ▷ 16550-equivalent controllers with 16-byte FIFO modes

- ▷ Full-duplex buffering and full status reporting

- ▷ Full modem capability

- ▷ Programmable word length, stop bits, and parity

- ▷ Programmable baud-rate generator

- USB 2.0 Interface

- $\triangleright$  Two root USB 2.0 hubs

- ▷ Up to six USB 2.0 ports

- ▷ USB bootable devices

- > USB Keyboard and Mouse

- ▷ USB v2.0 EHCI and v1.1 UHCI

- ▷ Over-current detection status

- ▷ Wake on USB at S3/S4

- USB 3.1 Interface

- ▷ 1x USB 3.1 Gen1 (5Gbps) host port

- ▷ 24-pin Type C connector

- ▷ Battery charging support

- Ethernet Interface

- ▷ Two fully independent Gigabit Ethernet ports

- Integrated LEDs on each port (Link/Activity and Speed)

- $\,\triangleright\,\,$  One Intel i210 IT controller chip and one i219 LM PHY transceiver chip

- ▷ Two 10-pin headers for Gigabit Ethernet user interface

- ▷ Two headers for GLAN LED signals

- ▷ IEEE 802.3 10/100BaseT and 10/100/1000BaseT compatible physical layers

- $\,\triangleright\,\,$  Auto-negotiation for speed, duplex mode, and flow control

- ▷ Full-duplex or half-duplex mode

- Full-duplex mode supports transmit and receive frames simultaneously

- Supports IEEE 802.3x Flow control in full-duplex mode

- Half-duplex mode supports enhanced proprietary collision reduction mode

- ► Video Interfaces (LVDS, DisplayPort, HDMI, and PEG)

- ▷ LVDS flat panel outputs

- Single channel capability

- Resolutions up to 1280x720 at 60Hz

- Pixel clock rates of up to 112MHz

- Pixel color depths of 18 and 24 bits

- ▷ DisplayPort

- Resolutions up to 4096x2304 pixels at 60Hz

- Pixel clock rates up to 605MHz

- AC-3 Dolby Digital

- Silent Stream Audio up to 192khz sampling rate

- $\triangleright$  HDMI outputs

- Resolutions up to 4096x2304 pixels at 30Hz

- Pixel clock rates up to 605MHz

- AC-3 Dolby Digital

- Silent Stream Audio up to 192khz sampling rate

- ▷ PCI Express graphics (PEG)

- External high-performance PCI Express graphics card support

- General-purpose PCI Express device support

- Transfer rate up to 8GT/s

- Theoretical bandwidth of up to 15.8GB/s

- PCIe Gen3 compliance

- ► GPIO Interface

- ▷ Two 6-pin interface headers

- ▷ Total of eight GPIO ports

- ▷ Sample code by request

- Utility Interface

- ▷ Power Button

- ▷ Reset Switch

- ⊳ Speaker

- Miscellaneous

- ▷ Real Time Clock (RTC) with external replaceable battery

- ▷ Battery-free boot

- Oops! Jumper support

- ▷ Serial Console support

- ▷ Watchdog Timer

- ▷ Logo Screen (Splash)

- ▷ SSD (Solid State Drive)

- ▷ Hardware Monitor (voltage and temperature)

Other configurations are possible. Please contact your local ADLINK Technology representative to discuss requirements.

# 1.4 Ordering Information

| Model Number               | Description                                                                                                                                              |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CM4-SL2-6102E-8G-8G        | PCI/104-Express Type 1 SBC, Intel® Core™ i3-6102E (max. 1.9GHz),<br>8GB DDR4 ECC, 8GB SLC SATA-SSD, 0°C to +60°C                                         |  |

| CM4-SL2-6102E-8G-8G-ETT    | PCI/104-Express Type 1 SBC, Intel® Core™ i3-6102E (max. 1.9GHz),<br>8GB DDR4 ECC, 8GB SLC SATA-SSD, -40°C to +85°C                                       |  |

| CM4-SL2-6102E-8G-8G-CC     | PCI/104-Express Type 1 SBC, Intel® Core™ i3-6102E (max. 1.9GHz),<br>8GB DDR4 ECC, 8GB SLC SATA-SSD, 0°C to +60°C, conformal coating<br>"Humiseal 1B73"   |  |

| CM4-SL2-6102E-8G-8G-ETT-CC | PCI/104-Express Type 1 SBC, Intel® Core™ i3-6102E (max. 1.9GHz),<br>8GB DDR4 ECC, 8GB SLC SATA-SSD, -40°C to +85°C, conformal<br>coating "Humiseal 1B73" |  |

| CM4-SL2-6100E-16G-32G      | PCI/104-Express Type 1 SBC, Intel Core i3-6100E (2.7GHz), CM236 chipset, 16G DDR4-ECC, 32G SLC SATA-SSD, 0°C to + 60°C                                   |  |

| CM4-SL4-1505L-16G-32G      | PCI/104-Express Type 1 SBC, Intel ® Xeon® E3-1505L v5 (2.0GHz),<br>CM236 chipset, 16G DDR4-ECC, 32G SLC SATA-SSD, 0°C to + 60°C                          |  |

#### Table 1-2: Cable Sets and Accessories

| Model Number                   | Description                                                        |

|--------------------------------|--------------------------------------------------------------------|

| CMx-SLx-X-10 CMx-SLx Cable Kit |                                                                    |

| CMx-SLx-TM-00                  | CMx-SLx Heat Spreader                                              |

| CMx-SLx-TM-10                  | CMx-SLx Passive Heat Sink (0°C to +60°C)                           |

| CMx-SLx-TM-20                  | CMx-SLx Active Heat Sink for i3-6102E CPU 25W CPU (-40°C to +85°C) |

# 1.5 Block Diagram

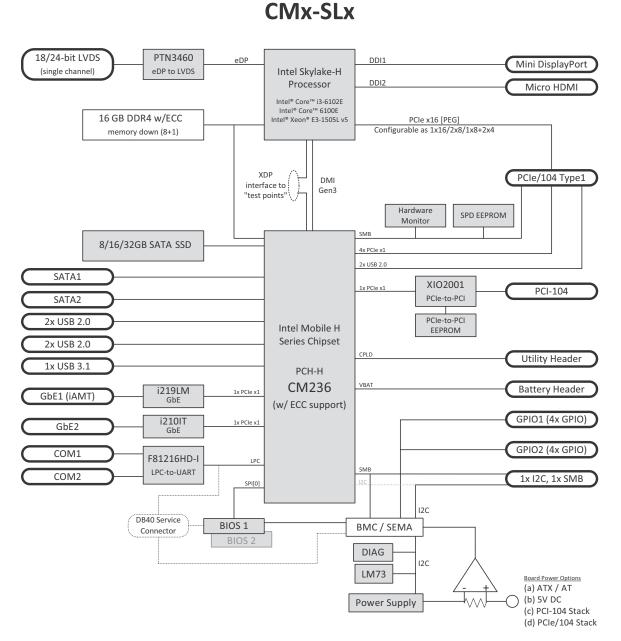

Figure 1-1 provides a functional representation of the CMx-SLx.

Figure 1-1: Functional Block Diagram

# 1.6 Specifications

### 1.6.1 Physical

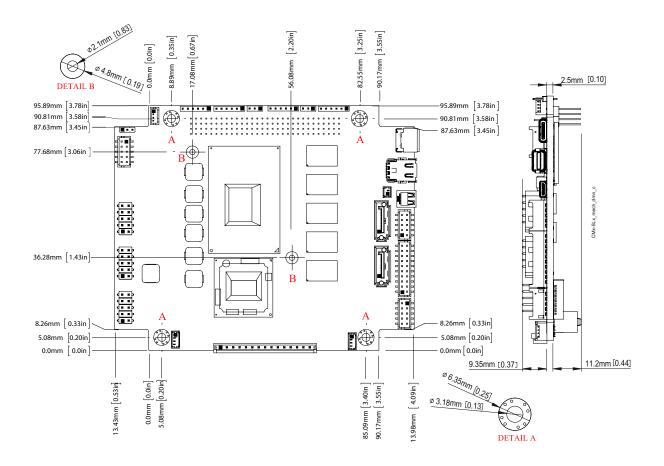

Table 1-3 provides the physical dimensions of the module.

| Table | 1-3: Weight | and Footprint  | Dimensions |

|-------|-------------|----------------|------------|

| Tuble | i o. noight | and i ootprint | Dimensions |

| Item             | Dimension               | Overall height is measured from the upper board                                                                         |

|------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Weight           | 0.12 kg (0.25 lbs)      | <ul> <li>surface to the highest permanent component</li> <li>(GLAN1 header) on the upper board surface. This</li> </ul> |

| Height (overall) | 9.35 mm (0.370) inches) | measurement does not include the heatsink, which                                                                        |

| Board thickness  | 2.50 mm (0.098 inches)  | can vary. The heatsink could increase this dimension.                                                                   |

| Width            | 95.89 mm (3.78 inches)  |                                                                                                                         |

| Length           | 117.40 mm (4.62 inches) |                                                                                                                         |

#### 1.6.2 Mechanical

All dimensions are given in inches and millimeters. Pin 1 is shown as a solid, black square on headers and connectors.

# 1.6.3 Electrical

Table 1-4 specifies the electrical characteristics of the module.

| Table 1-4: Electrical Specific |

|--------------------------------|

|--------------------------------|

| Parameter                              | Value                                                                                                                                                                                                                                                                                 |  |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Voltage Input                          |                                                                                                                                                                                                                                                                                       |  |

| Input Modes                            | <ul> <li>ATX and AT (AT mode startup controlled by<br/>SEMA and BMC)</li> </ul>                                                                                                                                                                                                       |  |

| Standard Inputs                        | ► ATX = 5V±5% / 5Vsb ±5%                                                                                                                                                                                                                                                              |  |

|                                        | ► AT = $5V\pm5\%$                                                                                                                                                                                                                                                                     |  |

|                                        | PCIe/104 Power Module = 5V±5%                                                                                                                                                                                                                                                         |  |

|                                        | NOTE: If the power supply also provides 3.3VDC and 12VDC to the board, only the 5-volt signals are routed to the I/O interfaces on the board. The 12-volt signals are routed to the PCIe/104, PCI-104, and LVDS interfaces. The 3.3-volt signals are routed to the PCI-104 interface. |  |

| RTC                                    | ► 3.0V, 2.0V to 3.3V (battery), +/-30mV ripple                                                                                                                                                                                                                                        |  |

| Power States (for all Standard Inputs) | <ul> <li>C1-C6, S0, S3, S4, S5 (Wake-on-USB S3/S4,<br/>Wake-on-LAN S3/S4/S5)</li> </ul>                                                                                                                                                                                               |  |

| Power Management                       | <ul> <li>ACPI 4.0 compliant</li> </ul>                                                                                                                                                                                                                                                |  |

### 1.6.4 Power

.

Table 1-5 provides the power consumption values of the CMx-SLx.

| Table | 1-5: Power | Supply  | Requirements     |

|-------|------------|---------|------------------|

| labio |            | o appij | n oquin on normo |

| Parameters                                                                                                                                   | 24W, Core i3-6102E SoC |

|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Input Type                                                                                                                                   | Regulated DC voltage   |

| Typical Idle Current and Power (EIST<br>enabled; 3TB HDD; Windows 10 Enterprise<br>Operating System)                                         | 2.15A (10.75W) @ 5V    |

| Typical Operating Mode Current and Power<br>(EIST enabled; 3TB HDD; Windows 10<br>Enterprise Operating System)                               | 5.26A (26.30W) @ 5V    |

| Maximum Operating Mode Current and Power<br>(EIST disabled; 3TB HDD; Windows 10<br>Enterprise Operating System; Intel TAT tool<br>v5.0.1026) | 6.69A (33.45W) @ 5V    |

| System S3 mode (3TB HDD; Windows 10<br>Enterprise Operating System)                                                                          | 0.22A (1.10W) @ 5VSB   |

| System S4 mode (3TB HDD; Windows 10<br>Enterprise Operating System)                                                                          | 0.175A (0.875W) @ 5VSB |

| System S5 mode with ECO enabled (3TB<br>HDD; Windows 10 Enterprise Operating<br>System)                                                      | 0.012A (0.06W) @ 5VSB  |

# 1.6.5 Environmental

Table 1-6 provides the most efficient operating and storage condition ranges required for this module.

| Parameter     | Conditions                                                                                                                             |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Temperature   |                                                                                                                                        |

| Operating     | -40°C to +85°C (-40°F to +185°F)<br>NOTE: this temperature range requires the CMx-SLx-TM-20 active<br>heatsink with specified airflow. |

| Storage       | –55°C to +85°C (–67°F to +185°F)                                                                                                       |

| Humidity      |                                                                                                                                        |

| Operating     | 5% to 90% relative humidity, non-condensing                                                                                            |

| Non-operating | 5% to 95% relative humidity, non-condensing                                                                                            |

Table 1-6: Environmental Requirements

Table 1-7 provides results for shock and vibration tests performed on the board.

Table 1-7: Shock and Vibration

| Parameter             | Result                                                                  |  |  |

|-----------------------|-------------------------------------------------------------------------|--|--|

| Shock Test            | 50G peak-to-peak, 11ms duration, MIL-STD-202G, Method 213B              |  |  |

| Random Vibration Test | Operating 11.96Grms, 50-2000Hz, each axis,<br>MIL-STD-202G, Method 214A |  |  |

Table 1-8 presents the average times between system failures.

#### Table 1-8: Mean Time Between Failures

| Parameter    | Value                                      |

|--------------|--------------------------------------------|

| MTBF at 40°C | 309,759 hrs (according to MIL calculation) |

| MTBF at 85°C | 71,063 hrs (according to MIL calculation)  |

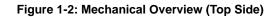

#### 1.6.6 Thermal/Cooling Requirements

The CMx-SLx is designed to operate at its maximum CPU speed and requires a thermal solution to cool the CPU. ADLINK offers an active heatsink, a heat spreader, and a passive heatsink (separate order numbers) for cooling. The heatsinks can be used for module evaluation. If a custom heatsink is used, it is recommended to connect it to the ADLINK heat spreader. This facilitates future module upgrades without the need to re-design the custom heatsink. Refer to Figure 1-3 for active heatsink dimensions. See Figure 1-4 for passive heatsink and heat spreader dimensions. Figure 1-6 provides airflow specifications. See "Getting Started" on page 13 for installation instructions.

Figure 1-3: Active heatsink mounting dimensions (top side)

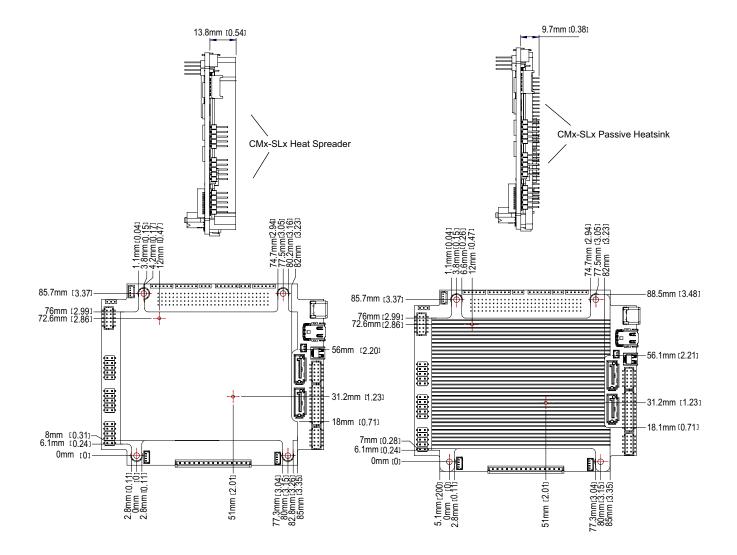

Figure 1-4 provides dimensions and mounting orientations of the passive heatsink and the heat spreader.

Figure 1-4: Passive Heatsink and Heat Spreader mounting dimensions (top side)

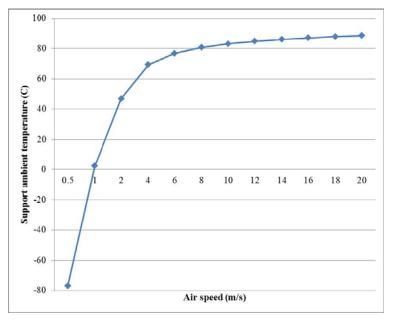

Figure 1-5 provides airflow versus ambient temperature ratios with regard to one airflow direction. See Figure 1-6 for an illustration of the airflow direction.

Figure 1-5: Temperature vs Airflow Chart

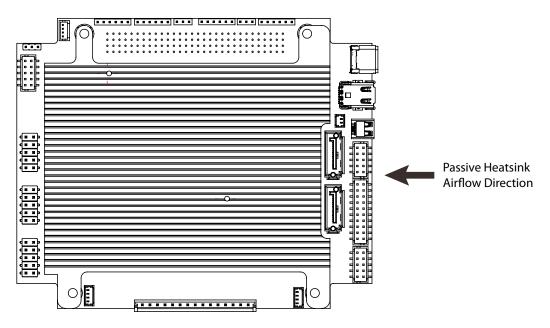

Figure 1-6 presents direction of airflow across the fins of the passive heatsink. Refer to Figure 1-5 for required airflow with regard to ambient temperature.

# 1.7 Getting Started

This section provides the most efficient way to setup and power on your CMx-SLx SBC. Select a clean flat, anti-static work surface for setup and operation, large enough to include any external peripherals and optional devices.

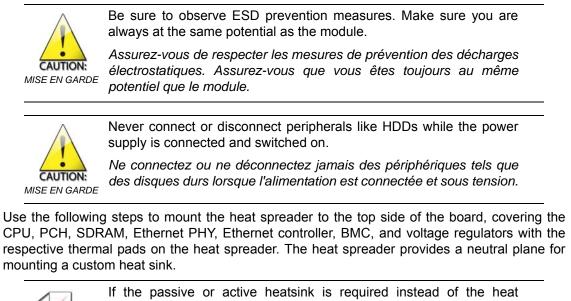

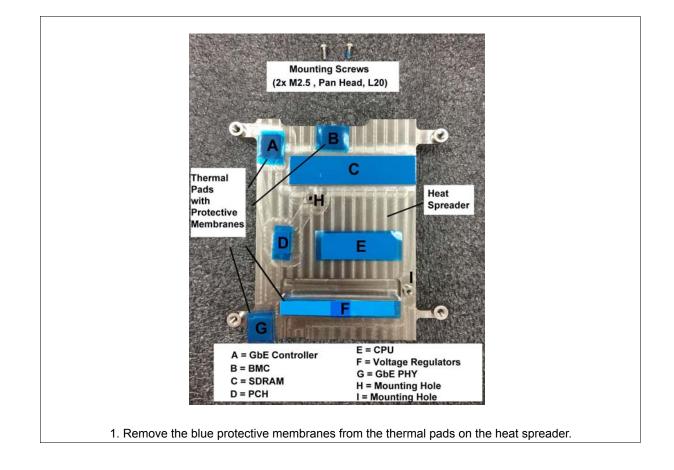

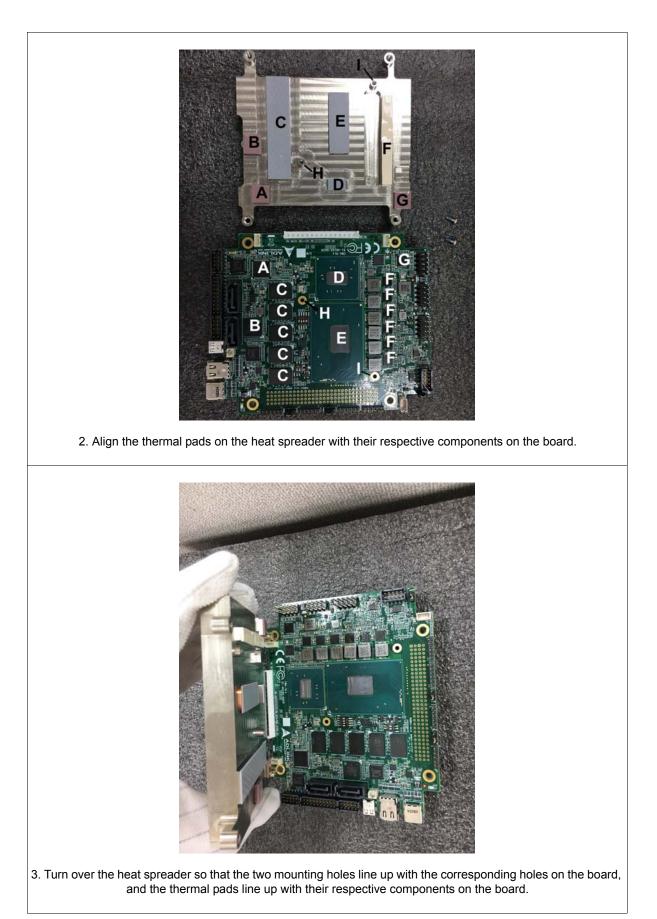

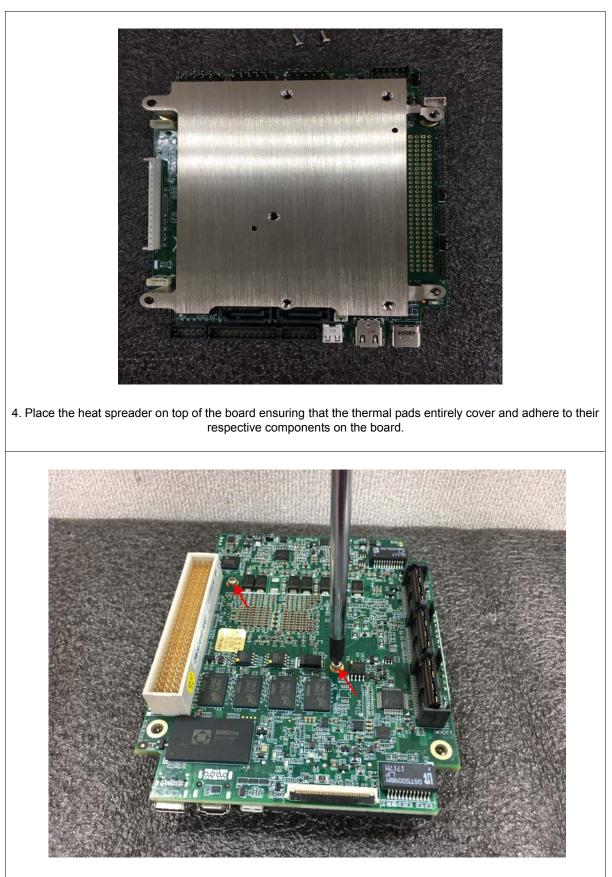

If the passive or active heatsink is required instead of the heat spreader, use the same mounting procedure used for the heat spreader, as described in the following steps. See "Thermal/Cooling Requirements" on page 10 for cooling solution requirements.

5. Turn over the assembly so that the board lays on top of the heat spreader and the heat spreader lays on the work surface. 6. Install two M2.5, pan head, L20 mounting screws at 2kgf. cm torque in the two mounting holes on the board. See the two red arrows in the photo above for locations of the mounting holes.

The passive and active heatsinks mount on top of the board (without the heat spreader) using the same installation steps for the heat spreader, provided above.

Use the cable set provided by ADLINK Technology to connect the CMx-SLx to an LCD monitor. Connect either PS/2 or USB keyboard or mouse, respectively. Use the SATA cable to connect the hard disk. Make sure that the pins match their counterparts correctly and are not twisted. If you plan to use additional peripherals, connect them to the appropriate headers.

Connect a 5-volt, 5 amps power supply to the power connector and switch on the power.

The 5 amps value is the minimum you should have for the standard peripherals mentioned. For additional peripherals, make sure enough power is available. The system will not work if there is not enough supply current for all your devices.

The display shows the BIOS messages. If you want to change the standard BIOS settings, press the <DEL> key to enter the BIOS setup menus. See Chapter 4 for setup details.

If you need to load the BIOS default values, they can be automatically loaded at boot time.

The CMx-SLx boots from CD drives, USB flash drives, hard disks, or microSD cards. If the media is connected and contains a valid operating system image, the display then shows the boot screen of your operating system.

The CMx-SLx needs adequate cooling measures depending on the desired operating temperature range. Using the board without cooling could damage the board permanently.

# 2 Hardware

This chapter describes the major integrated circuits (ICs) and interface connectors and headers on the module. The third and fourth sections of this chapter further describe the major ICs (including the manufacturers' model numbers) and the standard interface connectors on the board.

# 2.1 Major IC Definitions and Locations

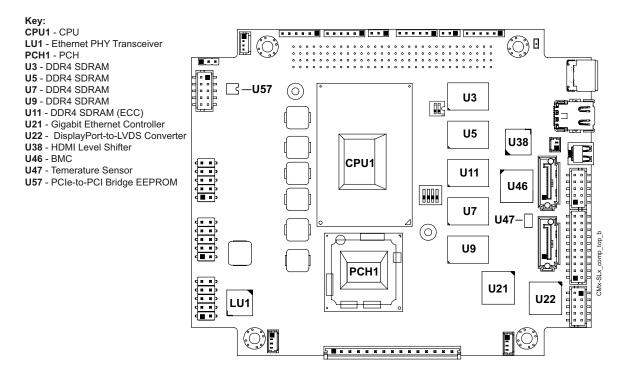

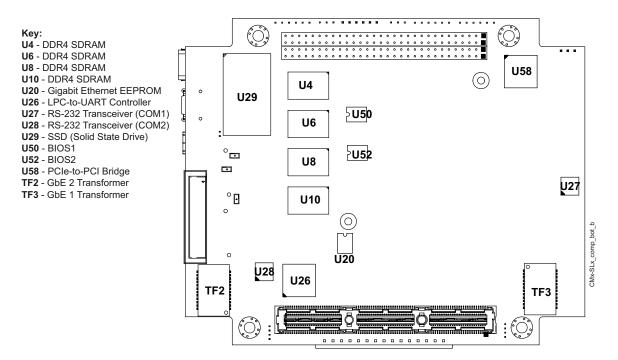

Table 2-1 describes the major ICs on the CMx-SLx, including a brief description of each IC. Figures 2-1 and 2-2 show the locations of the major ICs.

| Chip Type                                                                   | Mfg.            | Model                                                                                                                 | Description                                                                    | Function                                                                                                                         |

|-----------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| CPU (CPU1)                                                                  | Intel           | Core™ i3-6102E, 1.9GHz<br>(25W tuned to 17W)<br>Core™ i3-6100E, 2.7GHz<br>(35W)<br>Xeon® E3-1505L v5, 2.0GHz<br>(25W) | Central Processing<br>Unit with 2 execution<br>cores and up to 3MB<br>L2 cache | Integrates<br>Processor Core<br>and Graphics<br>Memory<br>Controller Hub                                                         |

| Gigabit Ethernet<br>PHY Transceiver<br>(LU1)                                | Intel           | WGI219LM SLKJ3                                                                                                        | Single-port Gigabit<br>Ethernet PHY<br>Transceiver for<br>GLAN1 interface      | Provides a<br>standard IEEE<br>802.3 Ethernet<br>interface for<br>Ethernet transfer<br>rates up to 1000<br>Mb/s                  |

| Chipset (PCH1)]                                                             | Intel           | CM236                                                                                                                 | I/O Hub for common<br>user interfaces                                          | Provides<br>Southbridge<br>interfaces and<br>off loads some<br>Northbridge<br>functions from<br>the CPU                          |

| DDR4 SDRAM<br>(U3, U5, U7, U9,<br>[and U11 to enable<br>ECC])               | Micron<br>Hynix | N/A                                                                                                                   | On-board DDR4,<br>memory module                                                | Provides<br>high-speed data<br>transfer                                                                                          |

| DDR4 SDRAM<br>(U4, U6, U8, U10 -<br>all on bottom side<br>[see Figure 2-2]) | Micron<br>Hynix | N/A                                                                                                                   | On-board DDR4,<br>memory module                                                | Provides<br>high-speed data<br>transfer                                                                                          |

| Ethernet EEPROM<br>(U20)                                                    | Winbond         | W25Q16DVSSIG                                                                                                          | Three-Wire Serial<br>EEPROM for Gigabit<br>Ethernet Controller                 | Provides storage<br>for MAC<br>addresses,<br>serial numbers,<br>and pre-boot<br>configuration<br>data                            |

| Gigabit Ethernet<br>Controller (U21 on<br>bottom side; see<br>Figure 2-2)   | Intel           | WGI210IT SLJXT                                                                                                        | Single-port Gigabit<br>Ethernet controller for<br>GLAN2 interface              | Integrates GbE<br>MAC, PHY, and<br>SGMII/SerDes<br>to enable 10T/<br>100TX/1000T<br>Ethernet signals<br>using the PCIe<br>x1 bus |

Table 2-1: Major Component Descriptions and Functions

| Chip Type                                                                        | Mfg.                 | Model                                  | Description                                                                                                                                                                | Function                                                                                                                                                                            |

|----------------------------------------------------------------------------------|----------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Embedded<br>DisplayPort-to-LVDS<br>Converter (U22)                               | NXP                  | PTN3460                                | Embedded<br>DisplayPort (eDP) to<br>LVDS bridge device<br>that enables<br>connectivity between<br>an embedded<br>DisplayPort (eDP)<br>source and an LVDS<br>display panel. | Processes the<br>incoming<br>embedded<br>DisplayPort<br>(eDP) stream,<br>performs eDP to<br>LVDS protocol<br>conversion, and<br>transmits<br>processed<br>stream in LVDS<br>format. |

| LPC-to-UART<br>Controller (U26)                                                  | Fintek               | F81216AU-I                             | Serial communication controller                                                                                                                                            | Provides 4<br>UART ports<br>through the LPC<br>bus                                                                                                                                  |

| RS-232 Transceiver<br>(U27)                                                      | Texas<br>Instruments | TRS3253EIRSMR                          | Transceiver for Serial<br>1 RS-232 signals                                                                                                                                 | Transmits and<br>receives RS-232<br>signals for<br>COM1                                                                                                                             |

| RS-232 Transceiver<br>(U28)                                                      | Texas<br>Instruments | TRS3253EIRSMR                          | Transceiver for Serial 2 RS-232 signals                                                                                                                                    | Transmits and<br>receives RS-232<br>signals for<br>COM2                                                                                                                             |

| Solid State Drive<br>[SSD] - SATA (U29) -<br>on bottom side [see<br>Figure 2-2]) | Greenliant           | 8GB: GLS85LS1008P<br>32GB GLS85LS1032P | Industrial-grade<br>soldered solid-state<br>storage module                                                                                                                 | Provides solid<br>state storage<br>through SATA<br>6Gb/s port                                                                                                                       |

| HDMI Level Shifter<br>(U38)                                                      | NXP                  | PTN3360DBS                             | HDMI level-shift IC<br>for HDMI video                                                                                                                                      | Converts HDMI<br>differential input<br>from the PCH to<br>TMDS<br>differential<br>output for the<br>HDMI interface                                                                  |

| BMC (U46)                                                                        | Texas<br>Instruments | TM4C123BH6ZRBT7R                       | Microcontroller                                                                                                                                                            | Provides<br>logistics and<br>forensic<br>information, flat<br>panel control,<br>I2C bus control,<br>user flash,<br>Watchdog Timer<br>and fan control                                |

| Temperature Sensor<br>- CPU (U47 on<br>bottom side; see<br>Figure 2-2)           | Texas<br>Instruments | LM73                                   | Digital-output<br>temperature sensor                                                                                                                                       | Measures its<br>own temperature<br>and the<br>temperature of<br>the CPU thermal<br>diode and<br>provides<br>temperature<br>correction with<br>fan speed<br>control.                 |

Table 2-1: Major Component Descriptions and Functions (Continued)

| Chip Type                                                                      | Mfg.                 | Model                | Description                                                           | Function                                                                                  |

|--------------------------------------------------------------------------------|----------------------|----------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| SPI Flash (U50 and U52)                                                        | Macronix             | MX25L12835FM2I-10GRT | Serial Peripheral<br>Interface Flash<br>Memory chip (for<br>firmware) | Stores BIOS 0<br>and BIOS 1 in<br>Flash Memory                                            |

| EEPROM,<br>PCIe-to-PCI Bridge<br>(U57 - on bottom<br>side [see<br>Figure 2-2]) | Atmel                | AT24C08D             | Two-Wire Serial<br>EEPROM for<br>PCIe-to-PCI Bridge                   | Stores<br>PCIe-to-PCI<br>bridge<br>configuration<br>data                                  |

| PCIe-to-PCI Bridge<br>(U58)                                                    | Texas<br>Instruments | XIO2001              | PCIe-to-PCI interface                                                 | Migrates legacy<br>PCI interfaces                                                         |

| Gb Ethernet<br>Transformer (TF3 -<br>on bottom side) [see<br>Figure 2-2]       | BOTHHAND             | GST5009M             | Gigabit Ethernet<br>Magnetics                                         | Provides<br>electrical<br>isolation for<br>Gigabit Ethernet<br>PHY transceiver<br>(GLAN1) |

| Gb Ethernet<br>Transformer (TF2 -<br>on bottom side) [see<br>Figure 2-2]       | BOTHHAND             | GST5009M             | Gigabit Ethernet<br>Magnetics                                         | Provides<br>electrical<br>isolation for<br>Gigabit Ethernet<br>controller<br>(GLAN2)      |

Table 2-1: Major Component Descriptions and Functions (Continued)

Figure 2-1: Component Locations (Top Side)

Figure 2-2: Component Locations (Bottom Side)

# 2.2 Header and Connector Definitions and Locations

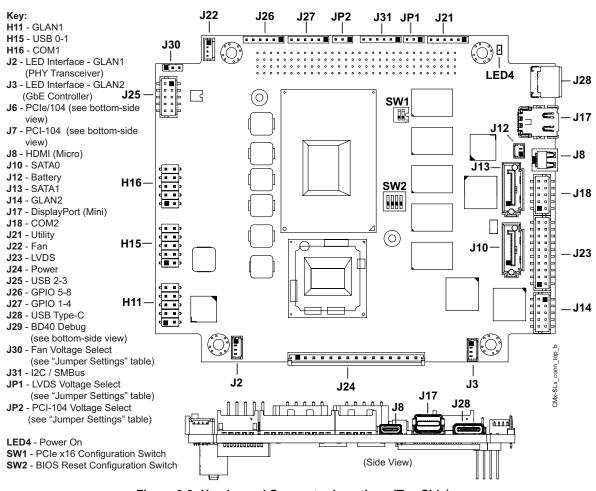

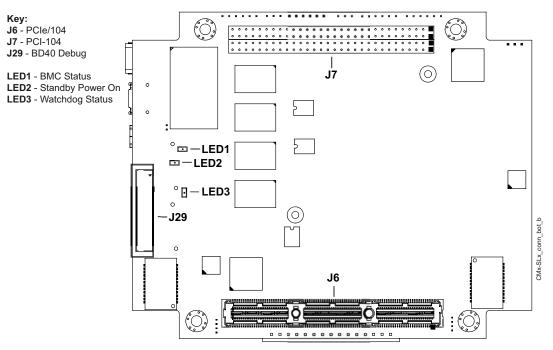

Table 2-2 describes the headers, connectors, and sockets shown in Figures 2-3 and 2-4.

| Header/Connector #       | Access | Description                                                                                                                     |  |  |  |

|--------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| H11 – GLAN1              | Тор    | 10-pin, 0.100" (2.54mm) header for Gigabit Ethernet port 1<br>(JIH JVE, 21N22564-10M00B-01G-6-C-02)                             |  |  |  |

| H15 – USB (0-1)          | Тор    | 10-pin, 0.100" (2.54mm) header for USB 2.0 ports 0-1<br>(JIH JVE, 21N22564-10M00B-01G-6-C-02)                                   |  |  |  |

| H16 – COM1               | Тор    | 10-pin, 0.100" (2.54mm) header for serial port 1<br>(JIH JVE, 21N22564-10M00B-01G-6-C-02)                                       |  |  |  |

| J2 – LED - GLAN1         | Тор    | 4-pin, 0.049" (1.25mm) shrouded, single-row header for Gigabit<br>Ethernet port 1 LED<br>(REGO, 830-1251-02STD-3.2-6T)          |  |  |  |

| J3 – LED - GLAN2         | Тор    | 4-pin, 0.049" (1.25mm) shrouded, single-row header for Gigabit<br>Ethernet port 2 LED<br>(REGO, 830-1251-02STD-3.2-6T)          |  |  |  |

| J6 – PCIe/104            | Bottom | 156-pin, 0.025" (0.64mm) standard PCI Express connector for SMBus, USB 2.0, PCIe x1, and PCI interfaces (SAMTEC, ASP-129646-03) |  |  |  |

| J7 – PCI-104             | Bottom | 60-pin, 0.079" (2mm) standard PCI-104, male connector for PCI interfaces (EPT, 264-17302)                                       |  |  |  |

| J8 – HDMI (Micro)        | Тор    | 19-pin, 0.016" (0.04mm), standard micro-connector for HDMI<br>Type D video port<br>(MOLEX, 46765-0001)                          |  |  |  |

| J10 – SATAO              | Тор    | 7-pin, 0.050" (1.27mm) standard connector for SATA 6Gb/s port<br>0<br>(WIN WIN, WATF-07DBLBA1UW)                                |  |  |  |

| J12 – Battery            | Тор    | 2-pin, 0.049" (1.25mm) shrouded header for power from<br>external battery<br>(REGO, 830-1251-02STD-3.2-6T)                      |  |  |  |

| J13 – SATA1              | Тор    | 7-pin, 0.050" (1.27mm) standard connector for SATA 6Gb/s port<br>1<br>(WIN WIN, WATF-07DBLBA1UW)                                |  |  |  |

| J14 – GLAN2              | Тор    | 10-pin, 0.079" (2mm) shrouded header for Gigabit Ethernet port<br>2<br>(CST, CSI-2221-102R)                                     |  |  |  |

| J17 – DisplayPort (MIni) | Тор    | 20-pin, right-angle Thunderbolt connector for Mini DisplayPort<br>interface<br>(FOXCONN, 3VT11207-N730-7H)                      |  |  |  |

| J18 – COM2               | Тор    | 10-pin, 0.079" (2mm) shrouded header for serial port 2<br>(CST, CSI-2221-102R)                                                  |  |  |  |

| J21 – Utility            | Тор    | 6-pin, 0.079" (2mm) single-row header for Power Button, Reset<br>Switch, and Speaker<br>(SAMTEC, TMM-106-03-L-S)                |  |  |  |

| J22 – Fan                | Тор    | 4-pin, 0.049" (1.25mm) single-row, shrouded header for power<br>to external fan<br>(HIROSE, DF13-4P-1.25DSA)                    |  |  |  |

| J23 – LVDS               | Тор    | 20-pin, 0.079" (2mm) shrouded header for LVDS video port (CST, CSI-2221-202R)                                                   |  |  |  |

| J24 – Power              | Тор    | 15-pin, 0.100" (2.54mm) shrouded, straight header for<br>supplying external power to the board<br>(JST, B15B-EH-A/LF)           |  |  |  |

#### Table 2-2: Header and Connector Descriptions

|                                                          | Table 2-2. Treader and Connector Descriptions (Continued) |                                                                                                                                                                                                                                                                                         |  |  |  |

|----------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Header/Connector #                                       | Access                                                    | Description                                                                                                                                                                                                                                                                             |  |  |  |

| J25 – USB 2-3                                            | Тор                                                       | 10-pin, 0.079" (2mm) shrouded header for USB 2.0 ports 2-3 (CST, CSI-2221-102R)                                                                                                                                                                                                         |  |  |  |

| J26 – GPIO1, (ports 5-8)                                 | Тор                                                       | 6-pin, 0.079" (2mm) single-row header for GPIO1, ports 5-8<br>(SAMTEC, TMM-106-03-L-S)                                                                                                                                                                                                  |  |  |  |

| J27 – GPIO2 (ports 1-4)                                  | Тор                                                       | 6-pin, 0.079" (2mm) single-row header for GPIO2, ports 1-4<br>(SAMTEC, TMM-106-03-L-S)                                                                                                                                                                                                  |  |  |  |

| J28 – USB Type-C                                         | Тор                                                       | 24-pin, standard female right-angle connector for USB 3.1 host function<br>(FOXCONN, UT11113-11604-7)                                                                                                                                                                                   |  |  |  |

| J29 – DB40 Debug                                         | Bottom                                                    | 40-pin, DB40 Front-Flip connector for debug card (Molex, 502790-4091)                                                                                                                                                                                                                   |  |  |  |

| J30 – Fan Voltage Select (see<br>Table 2-3 for settings) | Тор                                                       | 3-pin, 0.079" (2mm) single-row jumper header for setting the fan interface voltage (JIH21N1250-03S10B-01G-4/2.8-G)                                                                                                                                                                      |  |  |  |

| J31 – I2C / SMBus                                        | Тор                                                       | 6-pin, 0.079" (2mm) single-row header for I2C and SMBus<br>interfaces<br>(SAMTEC, TMM-106-03-L-S)                                                                                                                                                                                       |  |  |  |

| JP1 – LVDS Voltage Select                                | Тор                                                       | 3-pin, 0.079" (2mm) single-row jumper header for setting the LVDS interface voltage (JIH21N1250-03S10B-01G-4/2.8-G)                                                                                                                                                                     |  |  |  |

| JP2 – PCI-104 Voltage Select                             | Тор                                                       | 3-pin, 0.079" (2mm) single-row jumper header for setting the<br>PCI-104 interface voltage<br>(JIH21N1250-03S10B-01G-4/2.8-G)                                                                                                                                                            |  |  |  |

| LED1 – BMC Status                                        | Bottom                                                    | Indicates system-error blink codes (Blue)<br>[LIGITEK, LG-192DBK-CT/T]                                                                                                                                                                                                                  |  |  |  |

| LED2 – +3V3 Standby Power On                             | Bottom                                                    | Indicates standby power on (Green)<br>[LIGITEK, LG-192G-CT]                                                                                                                                                                                                                             |  |  |  |

| LED3 – Watchdog Status                                   | Bottom                                                    | Indicates triggered watchdog timer (Red)<br>[LIGITEK, LG-192HRF-CT]                                                                                                                                                                                                                     |  |  |  |

| LED4 – +5V Power On                                      | Тор                                                       | Indicates +5V power on (Green)<br>[LIGITEK, LG-192G-CT]                                                                                                                                                                                                                                 |  |  |  |

| SW1 – PCIe x16 Lane<br>Configuration Switch              | Тор                                                       | 2-pole dip switch for selecting CPU PCIe x16 lane<br>configurations (WIN WIN, DHN-02-T-V-T/R)<br><u>Switch Positions</u> <u>Lane Configurations</u><br>1-OFF, 2-OFF = 1x16 [Default]<br>1-OFF, 2-ON = 2x8<br>1-ON, 2-OFF = Reserved<br>1-ON, 2-ON = 1x8, 2x4<br><u>Switch Positions</u> |  |  |  |

|                                                          |                                                           |                                                                                                                                                                                                                                                                                         |  |  |  |

| Header/Connector #                       | Access | Description                                                                   |

|------------------------------------------|--------|-------------------------------------------------------------------------------|

| SW2 – BIOS Reset<br>Configuration Switch | Тор    | 4-pole dip switch for configuring BIOS reset<br>(DIPTRONICS, DHNF-04-T-Q-T/R) |

|                                          |        | Pole 1 - CPU_BIOS_Default<br>▶ OFF= User settings active [default]            |

|                                          |        | <ul> <li>ON = Resets BIOS user settings</li> </ul>                            |

|                                          |        | Pole 2 - BIO_ Mode<br>► OFF = Failsafe BIOS [default]                         |

|                                          |        | ON = Normal BIOS                                                              |

|                                          |        | Pole 3 - SEL_BIOS<br>► OFF = BIOS 1 active                                    |

|                                          |        | ON = BIOS 0 active [default]                                                  |

|                                          |        | Pole 4 - POSTWDT_DIS#<br>► OFF = Watchdog timer disabled [default]            |

|                                          |        | <ul> <li>ON = Watchdog timer active</li> </ul>                                |

|                                          |        | 4 Switch Poles                                                                |

Table 2-2: Header and Connector Descriptions (Continued)

Figure 2-3: Header and Connector Locations (Top Side)

Figure 2-4: Header and Connector Locations (Bottom Side)

Pin 1 is shown as a larger, black square on headers and connectors.

# 2.3 Jumper Header Definitions

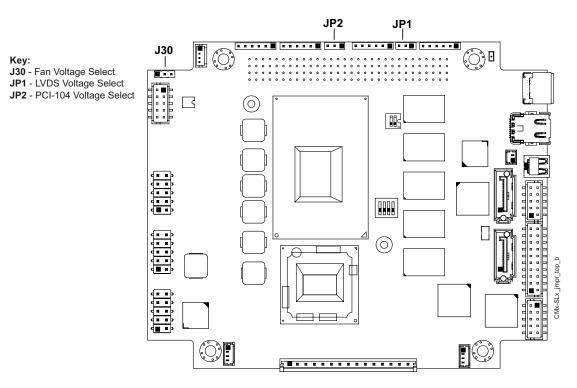

Table 2-3 describes the jumper headers shown in Figure 2-5. All jumper headers provide 0.079" (2mm) pitch.

| Jumper Header                                                     | Jumper on Pins 1-2           | Jumper on Pins 2-3             |

|-------------------------------------------------------------------|------------------------------|--------------------------------|

| J30 – Fan Voltage                                                 | Enable +5V (1-2)             | Enable +12V (2-3)<br>(Default) |

| JP1 – LVDS Voltage Selection<br>(JIH JVE, 27S1001-OPS35-01G-B)    | Enable +3.3V (1-2) (Default) | Enable +5V (2-3)               |

| JP2 – PCI-104 Voltage Selection<br>(JIH JVE, 27S1001-OPS35-01G-B) | Enable +3.3V (1-2) (Default) | Enable +5V (2-3)               |

| Table | 2-3: | Jumper | Settings |

|-------|------|--------|----------|

|-------|------|--------|----------|

Note: Remove all jumpers to set 18-bit LCD interface.

Figure 2-5: Jumper Header Locations (Top Side)

# 2.4 Component Features

This section further describes the supported features of the CMx-SLx major, on-board hardware components.

#### 2.4.1 CPU

The CMx-SLx features the 6th Generation Intel® Core<sup>™</sup> i3 and Intel® Xeon® E3 processor. The CPU integrates a high-performance 64-bit, x86 Processor Core with Memory Controller and GEN 9 graphics engine. This single chip—based on Intel 64 Architecture and built on 14-nm process technology—provides two execution cores and a Gen 3 Direct Media Interface (DMI) for high-speed connectivity to the Chipset. The CPU also supports Intel Hyper-Threading Technology and up to 16GB of DDR4 SDRAM memory at 1866MHz for high overall performance. Refer to the 6th Generation Intel Processor Data Sheet for H-Platforms on the Intel website for more information.

#### 2.4.4 Chipset

The Intel® CM236 Chipset functions as the IO hub, controlling the DMI and system clock on the CPU and delivering IO interfaces at transfer rates of 8 GT/s. The CM236 supports Gen 3 PCIe connectivity with new technologies such as Intel Rapid Storage Technology 14, Context Sensing SDK, and Platform Trust Technology 3.0. Refer to the CM236 data sheet at the Intel website.

#### 2.4.2 SDRAM

The CMx-SLx employs one 1866/2133MHz memory channel with one rank of eight system memory chips (and one additional chip for ECC). The board provides up to 16GB of extended memory using 16Gb DDR4 SDRAM chips. The CPU features Intel FMA (Fast Memory Access) technology, providing Just-in-Time Scheduling for issuing concurrent requests, Command Overlap for issuing multiple overlapping commands, and Out-of-Order Scheduling to re-order requests made to the same open page.

#### 2.4.5 Gigabit Ethernet PHY Transceiver (I219 - Supporting GLAN1)

The Intel I219 provides a dedicated Physical Layer (PHY) interconnect between the Media Access Controller (MAC) on the Chipset and the first Gb Ethernet interface (GLAN1) on the CMx-SLx. The PHY circuitry provides a standard IEEE 802.3 Ethernet interface for 10BASE-T, 100BASE-TX, and 1000BASE-T applications (802.3, 802.3U, and 802.3ab). The I219 allows for less power consumption during periods of low data activity with the support for the Energy Efficient Ethernet (EEE) 802.az specification. Communication between the I219 and the Chipset occurs through PCIe and SMBus interfaces. The PCIe interface is used for all link speeds when the system is in an active state, and the SMBus interface is used only when the system is in a low power state. For remote, out-of-band system management, the I219 supports Intel Active Management Technology (AMT) 11.0. Refer to the Intel Ethernet Connection I219 data sheet on the Intel web site for more information.

# 2.4.6 Gigabit Ethernet Controller (I210 - Supporting GLAN2)

The second Gb Ethernet interface (GLAN2) originates from the Intel I210 Controller, which provides a single-port controller that supports GbE functionality using the high-speed PCIe standard, v2.1 (2.5GT/s). The I210 features a fully-integrated Media Access Control (MAC) and a Physical Layer (PHY), which enable 1000BASE-T implementations such as rack-mounted or pedestal servers in add-on NIC or LAN-on-Motherboard (LOM) designs. Other implementations include blade servers such as LOMs or mezzanine cards as well as embedded applications such as switch add-on cards and network appliances. Additionally, the I210 integrates an SGMII/SerDes port, which allows MAC-to-MAC blade server connections or MAC-to-external PHY connections. Refer to the Intel I210 Ethernet Controller data sheet on the Intel web site.

# 2.4.7 SSD (Solid State Drive)

The CMx-SLx provides an on-board, 8GB SSD for user storage. The SSD communicates with the Chipset through the SATA 3Gb/s port and is user-accessible through the BIOS Boot menu and the OS interface. For more information, refer to the GLS85LS1008P/GLS85LS1032P SSD data sheet on the Greenliant website.

# 2.4.3 BMC

The Board Management Controller (BMC) is a micro-controller chip that transmits and receives data to and from the SEMA, BIOS, and debug utilities—monitoring system performance, behavior, and diagnostics at transfer speeds up to 3.33Mbps at 400KHz. The BMC queries components on the board for data related to temperature, power-supply voltage and current, power sequencing, logistics and forensics, flat panel control, I2C bus control, user flash, Watchdog Timer, and fan control. Refer to the Texas Instruments web site for more information on the TM4C123GH6ZRB micro-controller.

# 2.4.4 LM73 Temperature Sensor

The temperature sensor operates over a wide temperature range (-40°C to +150°C) with a 14-bit mode maximum resolution. Programmed to the BMC and controlled through the SEMA user interface, the temperature sensor monitors system temperatures and issues alerts, time outs, resets, and shutdowns, protecting the system as it approaches temperature limits. For more information on the LM73 Temperature Sensor, refer to the data sheet on the Texas Instruments website.

# 2.4.5 PTN3460I eDP-to-LVDS Converter

The PTN3460I supports single-bus or dual-bus LVDS signalling with color depths of 18 bits per pixel or 24 bits per pixel and pixel clock frequency up to 112MHz. LVDS data packing can be done either in VESA or JEIDA formats. Also, the DP AUX interface transports I2C-over-AUX commands and supports EDID-DDC communication with an LVDS panel. To support panels without EDID ROM, the PTN3460 can emulate EDID ROM behavior, avoiding specific changes in system video BIOS. Find more details on the NXP website.

#### 2.4.6 SMBus Slave Addresses

Table 2-8 lists the corresponding slave addresses of the devices on the SMBus.

| Address (HEX) | Function              | Device         |

|---------------|-----------------------|----------------|

| (50)          | BIOS / SEMA           | BMC            |

| (92)          | Temperature Sensor    | LM73           |

| (C0)          | eDP-to-LVDS Converter | PTN3460I       |

| (C8)          | GbE PHY               | I219           |

| APR           | PCIe Connector        | PCIe Connector |

Table 2-8: SMBus Slave Addresses

# 2.5 Standard Connectors

The section describes the industry-standard connectors on the board.

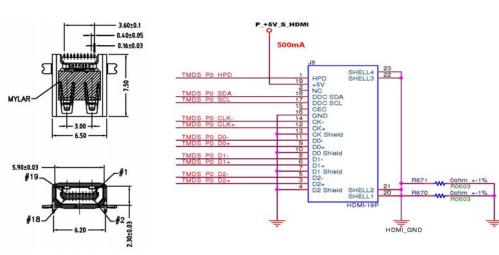

#### 2.5.1 Micro HDMI (J8)

The Micro HDMI connector (J8) provides the standard interface for IO connection to and from an HDMI audiovisual device. Figure 2-6 provides schematic and mechanical presentations of the micro HDMI connector.

Make sure the width of the mating connector does not conflict with the width of the mini DisplayPort mating connector.

Assurez-vous que la largeur du connecteur correspondant n'est pas en conflit avec la largeur du connecteur correspondant mini DisplayPort.

Figure 2-6: Micro HDMI connector

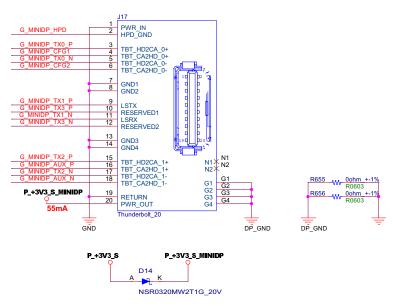

# 2.5.2 Mini DisplayPort (J17)

The Mini DisplayPort connector (J17) provides the standard interface to drive IO connection to and from a DisplayPort audiovisual device. Figure 2-7 provides schematic and mechanical presentations of the Mini DisplayPort connector.

CAUTION: MISE EN GARDE Make sure the width of the mating connector does not conflict with the widths of the micro HDMI and USB Type-C mating connectors.

Assurez-vous que la largeur du connecteur d'accouplement n'est pas en conflit avec les largeurs des connecteurs d'accouplement micro HDMI et USB Type-C.

Figure 2-7: Mini DisplayPort connector

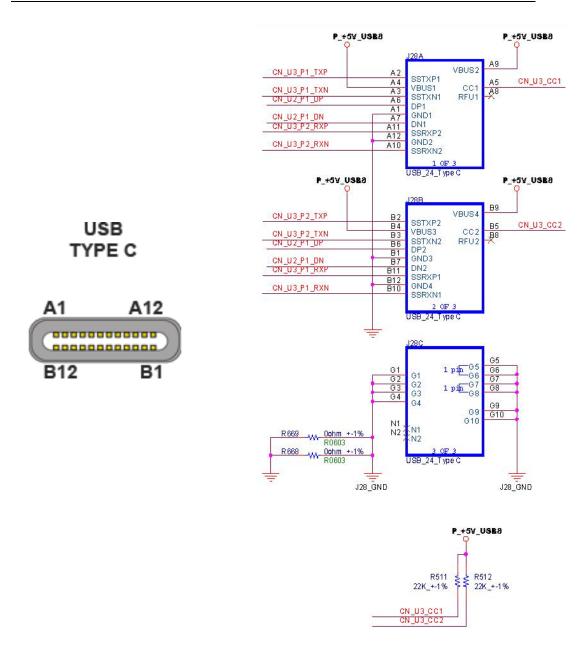

# 2.5.3 USB Type-C (J28)

The USB Type-C connector (J28) provides a standard USB Type-C interface for super-speed USB 3.1 host and device signals. Figure 2-8 provides schematic and mechanical presentations of the USB Type-C connector.

Make sure the width of the mating connector does not conflict with the width of the mini DisplayPort mating connector.

Assurez-vous que la largeur du connecteur correspondant n'est pas en conflit avec la largeur du connecteur correspondant mini DisplayPort.

Figure 2-8: USB Type-C connector

# 3 Interfaces

This chapter provides descriptions and signal definitions only of the non-standard interfaces on the board. Descriptions and signal definitions of standard interfaces such as PCI-104 and SATA can be found in their respective specification data sheets. If certain signals of standard interfaces have been modified or disconnected, those interfaces will be described in this chapter.

The tables in this chapter define pin sequence using the method in the following example: A 10-pin header with two rows of pins, using odd/even numbering, where pin 2 is directly across from pin 1, is noted as **10 pins, 2 rows, odd/even pin sequence (1, 2)**. Consecutive numbering is noted, for example, as **24 pins, 2 rows, consecutive pin sequence (1, 13)**, where pin 13 is directly across from pin 1. Refer to Figure 2-3 and Figure 2-4 for pin-1 locations.

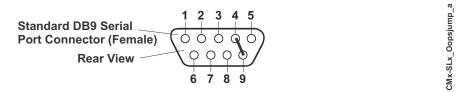

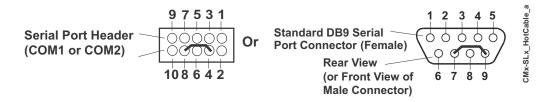

# 3.1 Serial Interfaces (H16 and J18)

Table 3-1 provides the signals for serial port 1 interface. Table 3-2 provides the signals for serial port 2 interface. Serial port 1 uses a 10-pin, vertical header with 2 rows, odd/even sequence (1, 2), and 0.100" (2.54mm) pitch. Serial port 2 uses a 10-pin, vertical header with 2 rows, odd/even sequence (1, 2), and 0.079" (2.00mm) pitch.

| Pin<br># | Signal  | DB9 # | Description                                                                                                                                                                                                                                                          |  |

|----------|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1        | S1_DSR# | 6     | COM1 Data Set Ready – Indicates external serial device is powered,<br>initialized, and ready. Used as hardware handshake with DTR for<br>overall readiness.                                                                                                          |  |

| 2        | S1_DCD# | 1     | COM1 Data Carrier Detect – Indicates external serial device is detecting a carrier signal (i.e., a communication channel is currently open). In direct connect environments, this input is driven by DTR as part of the DTR/DSR handshake.                           |  |

| 3        | S1_RTS# | 7     | COM1 Request To Send – Indicates serial port is ready to transmit data. Used as hardware handshake with CTS for low level flow control.                                                                                                                              |  |

| 4        | S1_RXD  | 2     | COM1 Receive Data – Serial port receive data input is typically held<br>at a logic 1 (mark) when no data is being transmitted, and is held<br>"Off" for a brief interval after an "On" to "Off" transition on the RTS<br>line to allow the transmission to complete. |  |

| 5        | S1_CTS# | 8     | COM1 Clear To Send – Indicates external serial device is ready to receive data. Used as hardware handshake with RTS for low level flow control.                                                                                                                      |  |

| 6        | S1_TXD  | 3     | COM1 Transmit Data – Serial port transmit data output is typically<br>held to a logic 1 when no data is being sent. Typically, a logic 0 (On)<br>must be present on RTS, CTS, DSR, and DTR before data can be<br>transmitted on this line.                           |  |

| 7        | S1_RI#  | 9     | COM1 Ring Indicator – Indicates external serial device is detecting a ring condition. Used by software to initiate operations to answer and open the communications channel.                                                                                         |  |