# **PPM-C412**

PC/104-Plus Single Board Computer Based on DM&P Vortex DX3 CPU

# **Product Manual**

# **Revision History**

| Document<br>Version | Last Updated<br>Date | Brief Description of Change                                                          |

|---------------------|----------------------|--------------------------------------------------------------------------------------|

| v1.0                | 10/30/2017           | Initial release                                                                      |

| v2.0                | 12/21/2021           | Rebranded manual, updated J107 part number, added Engineering<br>Mode Enable in BIOS |

# **Copyright and Trademarks**

Copyright 2021, WINSYSTEMS, Inc.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of WINSYSTEMS, Inc. The information in the document is subject to change without notice. The information furnished by WINSYSTEMS, Inc. in this publication is believed to be accurate and reliable. However, WINSYSTEMS, Inc. makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. WINSYSTEMS, Inc. makes no warranty of merchantability or fitness for any purpose. WINSYSTEMS, Inc. assumes no responsibility for any errors that may appear in this document.

### **Trademark Acknowledgments**

WINSYSTEMS is a registered trademark of WINSYSTEMS, Inc.

Pico-Clasp is a registered trademarks of Molex, Inc.

AMI UEFI BIOS is a registered trademark of American Megatrends, Inc.

All other marks are the property of their respective companies.

# **Table of Contents**

| 1 | <b>Bef</b><br>1.1 | warnings                                   |

|---|-------------------|--------------------------------------------|

| 2 | Intr              | oduction                                   |

| 3 | Fund              | tionality                                  |

| 4 | Feat              | ures                                       |

| 5 | <b>Gen</b><br>5.1 | eral Operation                             |

| 6 | Spe               | ifications                                 |

| 7 | Con               | iguration                                  |

|   | 7.1               | Component Layout                           |

|   |                   | 7.1.1 Top View                             |

|   |                   | 7.1.2 Bottom View                          |

|   |                   | 7.1.3 Top View Indicators and Jumpers 15   |

|   | 7.2               | I/O Port Map                               |

|   | 7.3               | Interrupt Map                              |

|   | 7.4               | PCI Devices and Functions                  |

|   | 7.5               | DOS Legacy Memory Map                      |

|   | 7.6               | Memory Shadowing                           |

|   | 7.7               | I/O Address Space                          |

|   | 7.8               | Digital I/O Register Definitions           |

|   | 7.0               |                                            |

|   |                   | 7.8.1       Port 0 through 5 I/O           |

|   |                   | 7.8.3 PAGE/LOCK                            |

|   |                   | 7.8.4         POL0 through POL2         21 |

|   |                   | 7.8.5 ENAB0 through ENAB2                  |

|   |                   | 7.8.6 INT_ID0 through INT_ID2 21           |

|   | 7.9               | Watchdog Timer                             |

|   |                   | 7.9.1 Advanced                             |

|   |                   | 7.9.2 Standard                             |

|    |       | 7.9.3                                                                                                                                                                                 | Legacy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 7.10  | Real-tin                                                                                                                                                                              | 1e Clock/Calendar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|    | 7.11  | SP1 Spe                                                                                                                                                                               | aker                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    |       | -                                                                                                                                                                                     | ors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

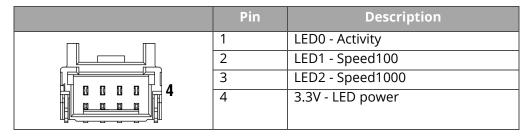

|    |       | 7.12.1<br>7.12.2<br>7.12.3<br>7.12.4<br>7.12.5<br>7.12.6<br>7.12.7<br>7.12.8<br>7.12.9<br>7.12.10<br>7.12.11<br>7.12.12<br>7.12.13<br>7.12.14<br>7.12.15<br><b>LED Indi</b><br>7.13.1 | J1 SATA PWR SATA Power Connector       23         J3 Power and Reset       24         J4 External Battery Connector       24         J5/J6 PC104 PC/104 Bus       25         J7 Multi I/O Connector       27         J103 10/100/1000 Mbps Ethernet       32         J100 Gigabit Ethernet LEDs       33         J8 CompactFlash Socket       33         J9 PC/104-Plus (PCI-104) Bus       34         J101 SATA Serial ATA (SATA)       35         J102 Digital Input/Output or GPIO       35         J105 USB 2.0 Ports       37         J106 Analog VGA Connector       38         J107 Backlight Power Connector       39         Vortex Fast Ethernet Indicators       39         D6 Status LED       39 |

|    |       | 7.13.3                                                                                                                                                                                | i210T Gigabit Ethernet Indicator 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8  | BIOS  |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|    | 8.1   | General                                                                                                                                                                               | Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    | 8.2   | Entering                                                                                                                                                                              | Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|    | 8.3   | Navigat                                                                                                                                                                               | ing the Menus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    | 8.4   | Enginee                                                                                                                                                                               | ring Mode Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    | 8.5   | <b>BIOS Sp</b>                                                                                                                                                                        | lash Screen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    | 8.6   | <b>BIOS Se</b>                                                                                                                                                                        | tting Storage Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|    |       | 8.6.1<br>8.6.2<br>8.6.3                                                                                                                                                               | CMOS Storage Locations.49Saving the CMOS Configuration.49Updating the BIOS FLASH PROM49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

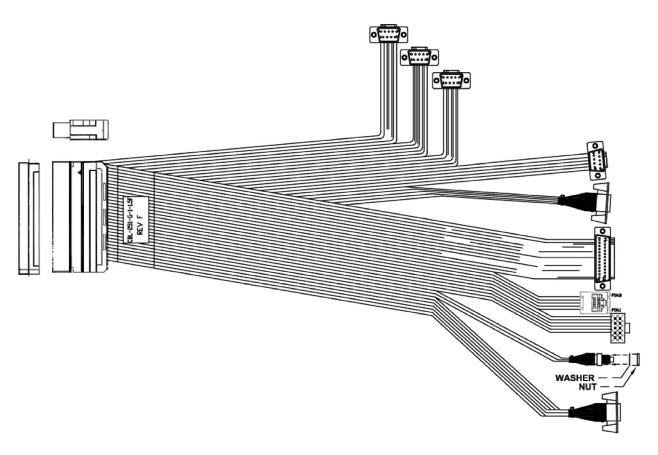

| 9  | Cable | es and A                                                                                                                                                                              | Accessories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10 | Soft  | ware Dr                                                                                                                                                                               | ivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Α | Best Practices                  |

|---|---------------------------------|

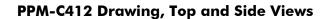

| B | Mechanical Drawings             |

| C | Power-on Self-Test (POST) Codes |

| D | Warranty Information            |

# 1. Before You Begin

Review the warnings in this section and the best practice recommendations (see "Best Practices" on page 51) when using and handling the WINSYSTEMS PPM-C412. Following these recommendations provides an optimal user experience and prevents damage. Read through this document and become familiar with the PPM-C412 before proceeding.

FAILING TO COMPLY WITH THESE BEST PRACTICES MAY DAMAGE THE PPM-C412 AND VOID YOUR WARRANTY.

### 1.1 Warnings

Only qualified personnel should configure and install the PPM-C412. While observing the best practices, pay particular attention to the following.

#### Avoid electrostatic discharge (ESD)

Only handle the circuit board and other bare electronics when electrostatic discharge (ESD) protection is in place. Having a wrist strap and a fully grounded workstation is the minimum ESD protection required before the ESD seal on the product bag is broken.

# 2. Introduction

This manual provides configuration and usage information for the PPM-C412. If you still have questions, contact Technical Support at (817) 274-7553, Monday through Friday, between 8 AM and 5 PM Central Standard Time (CST).

Refer to the WINSYSTEMS website for other accessories (including cable drawings and pinouts) that can be used with your PPM-C412.

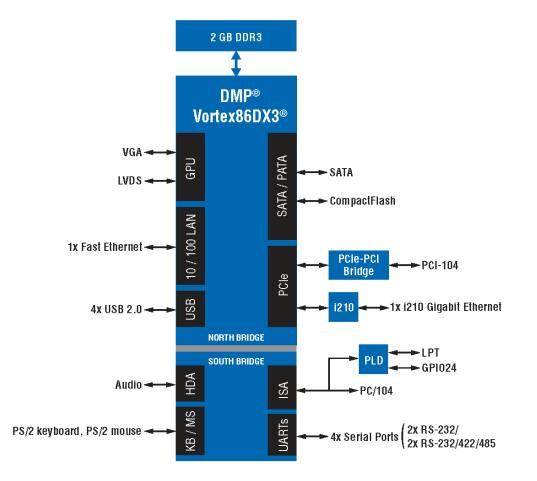

# 3. Functionality

The PPM-C412 is a single-board computer (SBC). It is a full-featured embedded system with a variety of on-board I/O options.

Two display interfaces (VGA and LVDS) are supported, along with stereo audio. Communication interfaces include one Fast Ethernet port, one Gigabit Ethernet port, four USB 2.0 ports, and four serial channels (two RS232/422/485 and two RS232). Twenty-four general-purpose I/O lines are individually programmable for input, output, or interrupt-driven applications, capable of fully latched event sensing with softwareprogrammable polarity. For additional flexibility, the I/O lines can be paired with external isolation and relay modules.

The PPM-C412 provides an upgrade for existing PC/104-*Plus* compatible single board computers. It is designed for harsh environments and reliability, with an optional thermal solution for operating temperatures between -40 and +85°C (-40 and +185°F).

Linux and other x86 operating systems can be initialized from the SATA, CompactFlash, or USB interfaces. This provides flexible data storage options.

The PPM-C412 has an integrated display controller that interfaces to both VGA and LVDS panel displays. The video output mode is selected in the CMOS setup.

Simultaneous LVDS panel and VGA mode is also supported. The VGA connector is located at **J106**. The LVDS interface is located at **J104**. The mode is selected in the BIOS. The backlight power connector is located at **J107**.

Contact a WINSYSTEMS applications engineer for information about available cable kits and supported panels.

NOTE WINSYSTEMS can provide custom configurations for OEM clients. Contact an application engineer for details.

# 4. Features

The PPM-C412 provides the following features.

#### Processor

DM&P 1 GHz Vortex DX3 SOC

### **Operating Systems (compatibility)**

- Windows Embedded 7 (WES7)

- Linux

- DOS

- Other x86 RTOS

### Memory

Up to 2 GB of DDR3 SDRAM (soldered down)

### BIOS

AMI

### Video

- VGA or LVDS (simultaneous operation supported)

- VGA resolutions up to 1920x1440

- LVDS resolutions up to 1600x1200 with 18-bits/pixel color panel support

### Ethernet

- Intel<sup>®</sup> i210 10/100/1000 Mbps controller

- Vortex 10/100 Mbps controller

#### Storage

- 1 CompactFlash socket

- 1 SATA channel

### General Purpose Input/Output (GPIO)

24 bidirectional 5 V I/O lines capable of event sense and interrupt generation

### **Serial Interfaces**

- Four USB 2.0 ports with ESD suppression

- Four serial COM ports

- Two RS232/422/485

- Two RS232 only

### **Bus Expansion**

• PC/104-Plus (PC/104 and PCI-104)

### **Line Printer Port**

• Bidirectional (SPP/ECP/EPP)

### Watchdog Timer

• Up to 255 minute reset

### Audio

- 2-channel line-level input

- 2-channel speaker-level output

- Stereo microphone input

#### Power

+5 VDC required, 1.2 A typical

### **Industrial Operating Temperature**

• -40 to +85°C (-40 to +185°F)

### **Form Factor**

• 3.60" x 3.80" (90 mm x 96 mm)

### **Additional Features**

- Real-time clock with optional battery backup

- Activity status LEDs on-board

- PS/2 keyboard and mouse supported

# 5. General Operation

## 5.1 System Block Diagram

# 6. Specifications

The PPM-C412 adheres to the following specifications and requirements.

| COM1 and COM2General purpose<br>input/output (GPIO)24 bidirectional I/O lines, 5V tolerant, with 12 mA sink<br>and 1 mA source capabilityVGAUp to 1920x1440 resolutionLVDS displaySupports one 24-bit SDR MODE LVDS LCD panel                                                                                                                                                                                                                                                                                                                                                          | Feature                  | Specification                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------|

| Processor1-GHz Vortex DX3 SOCPower+5 VDC +/- 5%<br>Max: 1.6 A<br>Typical: 1.2 APC/104 interface16-bit, stackthroughPC/104-Plus<br>interface32-bit PCI, stackthrough 33 MHzEthernet data rate• Intel i210 - 10/100/1000 Mbps controllerUSB interfaceFour USB 2.0 portsSerial interfaceFour serial channels with RS232 levels plus RS422/485 of<br>COM1 and COM2General purpose<br>input/output (GPIO)24 bidirectional I/O lines, 5V tolerant, with 12 mA sink<br>and 1 mA source capabilityVGAUp to 1920x1440 resolutionLVDS displaySupports one 24-bit SDR MODE LVDS LCD panel         | Electrical Specification | ons                                                                          |

| Power+5 VDC +/- 5%<br>Max: 1.6 A<br>Typical: 1.2 APC/104 interface16-bit, stackthroughPC/104-Plus<br>interface32-bit PCI, stackthrough 33 MHzEthernet data rate• Intel i210 - 10/100/1000 Mbps controller<br>• Vortex 10/100 Mbps controllerUSB interfaceFour USB 2.0 portsSerial interfaceFour serial channels with RS232 levels plus RS422/485 of<br>COM1 and COM2General purpose<br>input/output (GPIO)24 bidirectional I/O lines, 5V tolerant, with 12 mA sink<br>and 1 mA source capabilityVGAUp to 1920x1440 resolutionLVDS displaySupports one 24-bit SDR MODE LVDS LCD panel   | Nodel description        | PPM-C412 PC/104-Plus single board computer                                   |

| Max: 1.6 A<br>Typical: 1.2 APC/104 interface16-bit, stackthroughPC/104-Plus<br>interface32-bit PCI, stackthrough 33 MHzEthernet data rate• Intel i210 - 10/100/1000 Mbps controllerEthernet data rate• Intel i210 - 10/100/1000 Mbps controllerUSB interfaceFour USB 2.0 portsSerial interfaceFour serial channels with RS232 levels plus RS422/485 G<br>COM1 and COM2General purpose<br>input/output (GPIO)24 bidirectional I/O lines, 5V tolerant, with 12 mA sink<br>and 1 mA source capabilityVGAUp to 1920x1440 resolutionLVDS displaySupports one 24-bit SDR MODE LVDS LCD panel | Processor                | 1-GHz Vortex DX3 SOC                                                         |

| Typical: 1.2 APC/104 interface16-bit, stackthroughPC/104-Plus<br>interface32-bit PCI, stackthrough 33 MHzEthernet data rate• Intel i210 - 10/100/1000 Mbps controllerEthernet data rate• Intel i210 - 10/100/1000 Mbps controllerUSB interfaceFour USB 2.0 portsSerial interfaceFour serial channels with RS232 levels plus RS422/485 of<br>COM1 and COM2General purpose<br>input/output (GPIO)24 bidirectional I/O lines, 5V tolerant, with 12 mA sink<br>and 1 mA source capabilityVGAUp to 1920x1440 resolutionLVDS displaySupports one 24-bit SDR MODE LVDS LCD panel              | Power                    |                                                                              |

| PC/104 interface16-bit, stackthroughPC/104-Plus<br>interface32-bit PCI, stackthrough 33 MHzEthernet data rate• Intel i210 - 10/100/1000 Mbps controllerEthernet data rate• Intel i210 - 10/100/1000 Mbps controllerUSB interfaceFour USB 2.0 portsSerial interfaceFour serial channels with RS232 levels plus RS422/485 of<br>COM1 and COM2General purpose<br>input/output (GPIO)24 bidirectional I/O lines, 5V tolerant, with 12 mA sink<br>and 1 mA source capabilityVGAUp to 1920x1440 resolutionLVDS displaySupports one 24-bit SDR MODE LVDS LCD panel                            |                          |                                                                              |

| PC/104-Plus<br>interface32-bit PCI, stackthrough 33 MHzEthernet data rate• Intel i210 - 10/100/1000 Mbps controllerEthernet data rate• Vortex 10/100 Mbps controllerUSB interfaceFour USB 2.0 portsSerial interfaceFour serial channels with RS232 levels plus RS422/485 or<br>COM1 and COM2General purpose<br>input/output (GPIO)24 bidirectional I/O lines, 5V tolerant, with 12 mA sink<br>and 1 mA source capabilityVGAUp to 1920x1440 resolutionLVDS displaySupports one 24-bit SDR MODE LVDS LCD panel                                                                           |                          | 5.                                                                           |

| interface• Intel i210 - 10/100/1000 Mbps controllerEthernet data rate• Intel i210 - 10/100/1000 Mbps controllerUSB interfaceFour USB 2.0 portsSerial interfaceFour serial channels with RS232 levels plus RS422/485 of COM1 and COM2General purpose24 bidirectional I/O lines, 5V tolerant, with 12 mA sink and 1 mA source capabilityVGAUp to 1920x1440 resolutionLVDS displaySupports one 24-bit SDR MODE LVDS LCD panel                                                                                                                                                             |                          | -                                                                            |

| · Vortex 10/100 Mbps controllerUSB interfaceFour USB 2.0 portsSerial interfaceFour serial channels with RS232 levels plus RS422/485 of COM1 and COM2General purpose<br>input/output (GPIO)24 bidirectional I/O lines, 5V tolerant, with 12 mA sink<br>and 1 mA source capabilityVGAUp to 1920x1440 resolutionLVDS displaySupports one 24-bit SDR MODE LVDS LCD panel                                                                                                                                                                                                                   |                          | 32-bit PCI, stackthrough 33 MHz                                              |

| USB interfaceFour USB 2.0 portsSerial interfaceFour serial channels with RS232 levels plus RS422/485 of<br>COM1 and COM2General purpose<br>input/output (GPIO)24 bidirectional I/O lines, 5V tolerant, with 12 mA sink<br>and 1 mA source capabilityVGAUp to 1920x1440 resolutionLVDS displaySupports one 24-bit SDR MODE LVDS LCD panel                                                                                                                                                                                                                                               | Ethernet data rate       | Intel i210 - 10/100/1000 Mbps controller                                     |

| Serial interfaceFour serial channels with RS232 levels plus RS422/485 of<br>COM1 and COM2General purpose<br>input/output (GPIO)24 bidirectional I/O lines, 5V tolerant, with 12 mA sink<br>and 1 mA source capabilityVGAUp to 1920x1440 resolutionLVDS displaySupports one 24-bit SDR MODE LVDS LCD panel                                                                                                                                                                                                                                                                              |                          | Vortex 10/100 Mbps controller                                                |

| COM1 and COM2General purpose<br>input/output (GPIO)24 bidirectional I/O lines, 5V tolerant, with 12 mA sink<br>and 1 mA source capabilityVGAUp to 1920x1440 resolutionLVDS displaySupports one 24-bit SDR MODE LVDS LCD panel                                                                                                                                                                                                                                                                                                                                                          | JSB interface            | Four USB 2.0 ports                                                           |

| input/output (GPIO)and 1 mA source capabilityVGAUp to 1920x1440 resolutionLVDS displaySupports one 24-bit SDR MODE LVDS LCD panel                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Serial interface         | Four serial channels with RS232 levels plus RS422/485 on COM1 and COM2       |

| LVDS display         Supports one 24-bit SDR MODE LVDS LCD panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | /GA                      | Up to 1920x1440 resolution                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _VDS display             | Supports one 24-bit SDR MODE LVDS LCD panel                                  |

| <ul> <li>Single display max. resolution up to<br/>1920x1440@60 Hz</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          | <ul> <li>Single display max. resolution up to<br/>1920x1440@60 Hz</li> </ul> |

| Dual display max. resolution up to<br>1280x1024@60 Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |                                                                              |

| Audio MIC in, speaker out, and line in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Audio                    | MIC in, speaker out, and line in                                             |

| LPT interface Bidirectional (SPP/ECP/EPP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _PT interface            | Bidirectional (SPP/ECP/EPP)                                                  |

| SATA interface Supports one serial ATA 1.0 channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SATA interface           | Supports one serial ATA 1.0 channel                                          |

| Keyboard Standard PS/2 or USB interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Keyboard                 | Standard PS/2 or USB interface                                               |

| Mouse Standard PS/2 or USB interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Vouse                    | Standard PS/2 or USB interface                                               |

| System Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |                                                                              |

| Capacity 2 GB DDR3 RAM soldered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Capacity                 | 2 GB DDR3 RAM soldered                                                       |

| Solid state disk One Type I/II CompactFlash card device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | One Type I/II CompactFlash card                                              |

| Mechanical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | itions                   |                                                                              |

| Dimensions 3.6 x 3.8 in. (90 x 96 mm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Dimensions               | 3.6 x 3.8 in. (90 x 96 mm)                                                   |

| Weight 5.8 oz. (163 gm) with heat spreader/8.98 oz. (255 gm) with heatsink                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Neight                   |                                                                              |

| Board thickness 0.078 in.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Board thickness          | 0.078 in.                                                                    |

| Feature                                                                         | Specification                                                                              |  |

|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|

| Environmental Spec                                                              | ifications                                                                                 |  |

| Temperature                                                                     | Operational from -40 to +65°C (-40 to +149°F) with heat spreader (still air)               |  |

|                                                                                 | Operational from -40 to +85°C (-40 to +185°F) with heat spreader (300 LFM airflow)         |  |

|                                                                                 | Operational from -40 to +80°C (-40 to +176°F) with additional heat sink (still air)        |  |

|                                                                                 | Operational from -40 to +85°C (-40 to +185°F) with additional heat sink (200 LFM airflow)  |  |

| Humidity (RH)                                                                   | 5% to 95% noncondensing                                                                    |  |

| Mechanical shock testing                                                        | MIL-STD-202G, Method 213B, Condition A 50g half-sine,<br>11 ms duration per axis, 3 axis   |  |

| Random vibration testing                                                        | MIL-STD-202G, Method 214A, Condition D .1g/Hz<br>(11.95g rms), 20 minutes per axis, 3 axis |  |

| RoHS compliant                                                                  | Yes                                                                                        |  |

| MTBF                                                                            | 7.60 years, MIL-217 part count reliability method using manufacturer's failure rate data   |  |

| Operating Systems                                                               |                                                                                            |  |

| Runs Linux, DOS, Windows Embedded 7, and other x86-compatible operating systems |                                                                                            |  |

# 7. Configuration

This section describes the PPM-C412 components and configuration.

### 7.1 Component Layout

The PPM-C412 provides components on the top and bottom of the board.

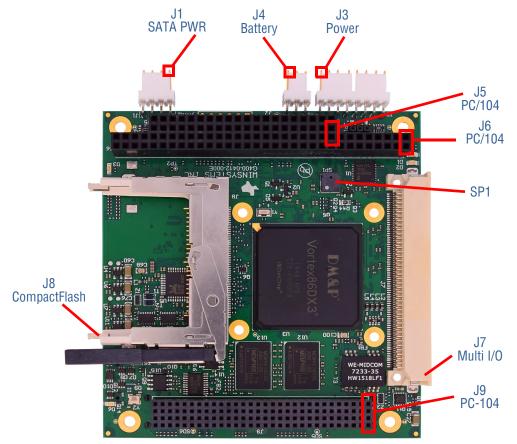

### 7.1.1 Top View

NOTE The reference line to each component part has been drawn to pin 1, and is also highlighted with a square, where applicable.

| Component | Description                                                              | Reference |

|-----------|--------------------------------------------------------------------------|-----------|

| J1        | SATA power                                                               | page 23   |

| J3        | Power                                                                    | page 24   |

| J4        | Battery                                                                  | page 24   |

| J5        | PC/104 16 bit                                                            | page 25   |

| J6        | PC/104 8 bit                                                             | page 25   |

| J7        | Multi I/O - PS/2 keyboard/mouse, serial ports, 10/100 ENET port, and LPT | page 27   |

| J8        | CompactFlash                                                             | page 33   |

| J9        | PCI-104                                                                  | page 34   |

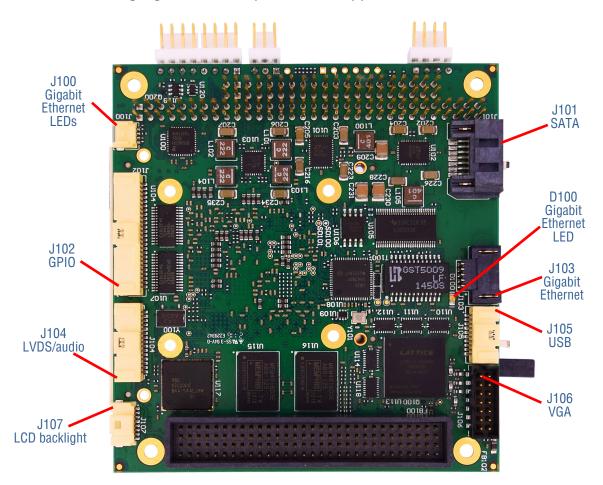

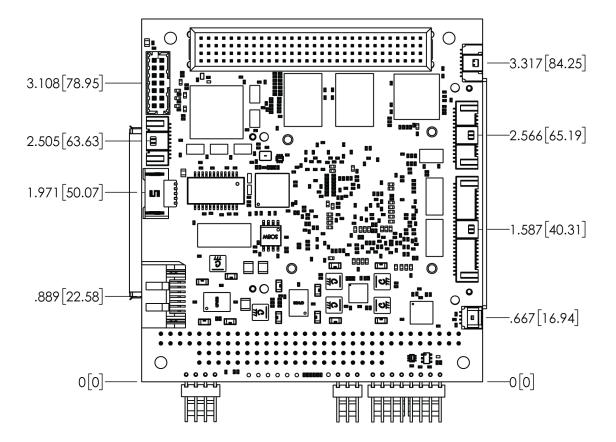

### 7.1.2 Bottom View

NOTE The reference line to each component part has been drawn to pin 1, and is also highlighted with a square, where applicable.

| Component | Description                       | Reference |

|-----------|-----------------------------------|-----------|

| J100      | Gigabit Ethernet LEDs             | page 33   |

| J101      | SATA                              | page 35   |

| J102      | GPIO                              | page 35   |

| J103      | Gigabit Ethernet                  | page 32   |

| J104      | LVDS/audio                        | page 36   |

| J105      | 4x USB 2.0                        | page 37   |

| J106      | VGA                               | page 38   |

| J107      | LCD backlight                     | page 39   |

| D100      | Gigabit Ethernet activity (green) | page 40   |

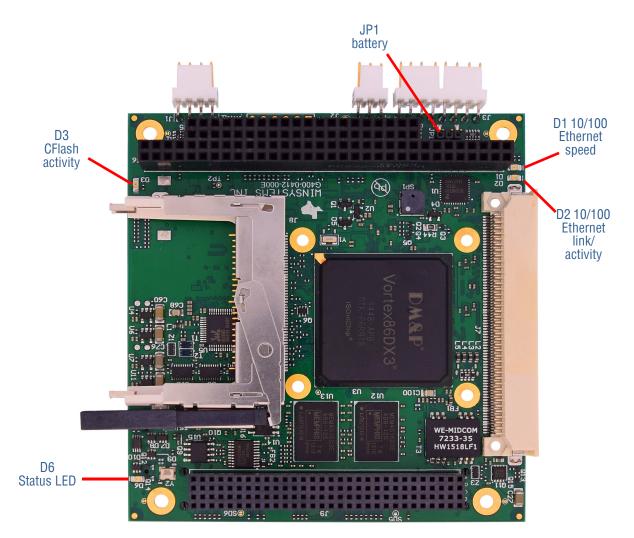

### 7.1.3 Top View Indicators and Jumpers

### Indicators

| Component | Description                             | Color  |

|-----------|-----------------------------------------|--------|

| D1        | 10/100 Ethernet speed Indicator         | Red    |

| D2        | 10/100 Ethernet link/activity indicator | Yellow |

| D3        | CFLASH activity                         | Red    |

| D6        | Status LED                              | Green  |

### Jumpers

| Component | Description             |

|-----------|-------------------------|

| JP1       | CMOS battery boot delay |

NOTE When installed in either position, the JP1 jumper causes a 6 second boot delay. This jumper must be installed to ensure proper boot when no external CMOS battery is connected.

v2.0

# 7.2 I/O Port Map

Following is a list of I/O ports for the PPM-C412.

NOTE The PPM-C412 uses a plug and play (PnP) BIOS resource allocation. Take care to avoid contention with resources allocated by the BIOS.

| Hex Range | Usage                                    |

|-----------|------------------------------------------|

| 000-00F   | 8237 DMA controller #1                   |

| 010-01F   | Free                                     |

| 020-021   | 8259 PIC #1                              |

| 022-03F   | Reserved                                 |

| 040-043   | 8254 PIT                                 |

| 044-04D   | Free                                     |

| 04E-04F   | Reserved for on-board configuration      |

| 050-05F   | Free                                     |

| 060-06F   | 8042 Keyboard/mouse controller           |

| 070-07F   | CMOS RAM, clock/calendar                 |

| 080-09F   | DMA page registers                       |

| 0A0-0BF   | 8259 PIC #2                              |

| 0C0-0DF   | 8237 DMA controller #2                   |

| 0E0-0EF   | DOS/4G 32-bit DOS extender registers     |

| 0F0-0F1   | Math co-processor control                |

| 0F2-0F7   | Free                                     |

| 0F8-0FF   | Math co-processor                        |

| 100-102   | Video controllers                        |

| 103-11F   | Free                                     |

| 120-12F   | Digital I/O (default)                    |

| 130-14F   | Free                                     |

| 150       | Reserved for on-board configuration      |

| 151-1CF   | Free                                     |

| 1D0-1DF   | Legacy watchdog (1D0-enabled; 1D8 - Pet) |

| 1E8-1EB   | Reserved for on-board configuration      |

| 1EC       | Interrupt status register                |

| 1ED       | Status LED                               |

| 1EE-1EF   | Watchdog timer control                   |

| 1F0-1FF   | IDE controller #1                        |

| 200-277   | Free                                     |

| 278-27F   | Free (option for LPT)                    |

| 280-2A7   | Free                                     |

| 2A8-2AF   | Free (option for on-board serial ports)  |

| 2B0-2DF   | Video controllers                        |

| 2E0-2E7   | Free                                     |

| 2E8-2EF   | COM4 (default)                           |

| 2F0-2F7   | Free                                     |

| 2F8-2FF   | COM2 (default)                           |

| 300-377   | Free                                     |

| 378-37B   | LPT (default)                            |

| 37C-3A7   | Free                                     |

| 3A8-3AF   | Free (option for on-board serial ports)  |

| 3B0-3BB   | Video controllers                        |

| Hex Range | Usage                                  |

|-----------|----------------------------------------|

| 3BC-3BF   | Free (option for LPT)                  |

| 3C0-3DF   | Video controllers                      |

| 3E0-3E7   | Free                                   |

| 3E8-3EF   | COM3 (default)                         |

| 3F0-3F7   | Free                                   |

| 3F8-3FF   | COM1 (default)                         |

| 4D0h-4D1h | Interrupt edge/level control registers |

| 564-568   | Advanced watchdog                      |

## 7.3 Interrupt Map

Hardware interrupts (IRQs) are supported for both PC/104 (ISA) and PC/ 104-*Plus* (PCI) devices. The user must reserve IRQs in the BIOS CMOS configuration for use by legacy devices. The PCI/PnP BIOS uses unreserved IRQs when allocating resources during the boot process. The table below lists IRQ resources as used by the PPM-C412.

| IRQ                          | Device                                                                      |  |  |  |  |  |  |

|------------------------------|-----------------------------------------------------------------------------|--|--|--|--|--|--|

| IRQ0                         | 18.2 Hz heartbeat                                                           |  |  |  |  |  |  |

| IRQ1                         | Keyboard                                                                    |  |  |  |  |  |  |

| IRQ2                         | Chained to slave controller (IRQ9)                                          |  |  |  |  |  |  |

| IRQ3                         | COM2                                                                        |  |  |  |  |  |  |

| IRQ4                         | COM1                                                                        |  |  |  |  |  |  |

| IRQ5                         | COM3                                                                        |  |  |  |  |  |  |

| IRQ6                         | COM4                                                                        |  |  |  |  |  |  |

| IRQ7                         | LPT                                                                         |  |  |  |  |  |  |

| IRQ8                         | Real time clock                                                             |  |  |  |  |  |  |

| IRQ9                         | Free                                                                        |  |  |  |  |  |  |

| IRQ10                        | Digital I/O                                                                 |  |  |  |  |  |  |

| IRQ11                        | Free                                                                        |  |  |  |  |  |  |

| IRQ12                        | Mouse                                                                       |  |  |  |  |  |  |

| IRQ13                        | Floating point processor                                                    |  |  |  |  |  |  |

| IRQ14                        | IDE                                                                         |  |  |  |  |  |  |

| IRQ15                        | Free                                                                        |  |  |  |  |  |  |

| These IRQ reference utility. | s are default settings that can be changed by the user in the CMOS Settings |  |  |  |  |  |  |

Some IRQs can be freed for other uses if the hardware features they are assigned to are not being used. To free an interrupt, use the CMOS setup screens to disable any unused board features or their IRQ assignments.

# 7.4 PCI Devices and Functions

### **Internal Devices**

| Bus | Device | Function | Device ID                                                        | Device/Function Description                    |  |

|-----|--------|----------|------------------------------------------------------------------|------------------------------------------------|--|

| 0   | 0      | 0        | 0F00h                                                            | Device: SoC transaction router                 |  |

| 0   | 2      | 0        | 0F31h                                                            | Device: Graphics and display                   |  |

| 0   | 19     | 0        | 0F20h (IDE)<br>0F21h (IDE)<br>0F22h<br>(AHCI)<br>0F23h<br>(AHCI) | Device: SATA                                   |  |

| 0   | 26     | 0        | 0F18h                                                            | Device: Trusted execution engine               |  |

| 0   | 27     | 0        | 0F04h                                                            | Device: HD audio                               |  |

| 0   | 28     | 28 0 0   | 0F48h                                                            | Device: PCI Express                            |  |

|     |        |          |                                                                  | Function: Root port 1                          |  |

|     |        | 1        | 0F4Ah                                                            | Device: PCI Express                            |  |

|     |        |          |                                                                  | Function: Root port 2                          |  |

|     |        | 2        | 0F4Ch                                                            | Device: PCI Express                            |  |

|     |        |          |                                                                  | Function: Root port 3                          |  |

|     |        | 3        | 0F4Eh                                                            | Device: PCI Express                            |  |

|     |        |          |                                                                  | Function: Root port 4                          |  |

| 0   | 29     | 0        | 0F34h                                                            | Device: EHCI USB                               |  |

| 0   | 31     | 0        | 0F1Ch                                                            | Device: Platform controller unit               |  |

|     |        |          |                                                                  | Function: LPC: Bridge to Intel<br>legacy block |  |

| 0   | 31     | 3        | 0F12h                                                            | Device: Platform controller unit               |  |

|     |        |          |                                                                  | Function: SMBus port                           |  |

#### **External Devices**

| Bus | Device | Function | Device ID | Device/Function Description         |

|-----|--------|----------|-----------|-------------------------------------|

| 3   | 0      | 0        | 104Ch     | Device: 8240                        |

|     |        |          |           | Function: PCI/PCI bridge            |

| 5   | 0      | 0        | 12D8h     | Device: 2304                        |

|     |        |          |           | Function: PCI/PCI bridge            |

| 6   | 1      | 0        | 12D8h     | Device: 2304                        |

|     |        |          |           | Function: PCI/PCI bridge            |

| 6   | 2      | 0        | 12D8h     | Device: 2304                        |

|     |        |          |           | Function: PCI/PCI bridge            |

| 7   | 0      | 0        | 8086h     | Device: 8086                        |

|     |        |          |           | Function: Intel Ethernet controller |

| 8   | 0      | 0        | 8086h     | Device: 8086                        |

|     |        |          |           | Function: Intel Ethernet controller |

### 7.5 DOS Legacy Memory Map

| Hex Range           | Usage                          |

|---------------------|--------------------------------|

| 0000:0000-0009:FFFF | Main memory (DOS area)         |

| 000A:0000-000B:FFFF | Legacy video area (SMM memory) |

| 000C:0000-000D:FFFF | Expansion area                 |

| 000E:0000-000E:FFFF | Extended system BIOS (lower)   |

| 000F:0000-000F:FFFF | System BIOS (upper)            |

| 0010:0000-7FFF:FFFF | Main memory                    |

### 7.6 Memory Shadowing

Any block of memory that can be designated as read only or write only can be "shadowed" into DRAM memory. Typically, this is done to allow ROM code to execute more rapidly out of main DRAM. ROM is used as read only during the copy process while DRAM at the same time is designated write only. After copying, the DRAM is designated read only so that ROM is shadowed. CPU bus transactions are routed accordingly. The PMC does not respond to transactions originating from PCI or ISA masters and targeted at shadowed memory blocks.

### 7.7 I/O Address Space

The SoC positively decodes accesses to all internal registers, including PCI configuration registers (CF8h and CFCh), PC/AT compatible I/O registers (8237, 8254, and 8259), and all relocatable I/O space registers (UART).

### 7.8 Digital I/O Register Definitions

The PPM-C412 uses the WINSYSTEMS exclusive WS16C48. This device provides 48 lines of digital I/O though only 24 are available on the PPM-C412. There are 16 unique registers within the WS16C48. The following table summarizes the registers.

| I/O Address Offset | Page 0      | Page 1      | Page 2      | Page 3      |

|--------------------|-------------|-------------|-------------|-------------|

| 00h                | Port 0 I/O  | Port 0 I/O  | Port 0 I/O  | Port 0 I/O  |

| 01h                | Port 1 I/O  | Port 1 I/O  | Port 1 I/O  | Port 1 I/O  |

| 02h                | Port 2 I/O  | Port 2 I/O  | Port 2 I/O  | Port 2 I/O  |

| 03h                | Port 3 I/O  | Port 3 I/O  | Port 3 I/O  | Port 3 I/O  |

| 04h                | Port 4 I/O  | Port 4 I/O  | Port 4 I/O  | Port 4 I/O  |

| 05h                | Port 5 I/O  | Port 5 I/O  | Port 5 I/O  | Port 5 I/O  |

| 06h                | Int_Pending | Int_Pending | Int_Pending | Int_Pending |

| 07h                | Page/Lock   | Page/Lock   | Page/Lock   | Page/Lock   |

| 08h                | Reserved    | Pol_0       | Enab_0      | Int_ID0     |

| 09h                | Reserved    | Pol_1       | Enab_1      | Int_ID1     |

| 0Ah                | Reserved    | Pol_2       | Enab_2      | Int_ID2     |

The following sections provide details on each of the internal registers.

### 7.8.1 Port 0 through 5 I/O

Each I/O bit in each of the six ports can be individually programmed for input or output. Writing a 0 to a bit position causes the corresponding output pin to go to a high-impedance state (pulled high by external 10 k $\Omega$  resistors), allowing it to be used as an input. When used in the input mode, a read reflects the inverted state of the I/O pin, such that a high on the pin reads as a 0 in the register. Writing a 1 to a bit position causes that output pin to sink current (up to 12 mA), effectively pulling it low.

### 7.8.2 INT\_PENDING

This read-only register reflects the combined state of the INT\_ID0 through INT\_ID2 registers. When any of the lower three bits are set, it indicates that an interrupt is pending on the I/O port corresponding to the bit positions that are set.

Reading this register allows an interrupt service routine to quickly determine if any interrupts are pending, and which I/O port has a pending interrupt.

### 7.8.3 PAGE/LOCK

This register serves two purposes. The upper two bits (D6 and D7) select the register page in use. Bits 0-5 allow the I/O ports to be locked. Write a 1

to the I/O port position to prohibit further writes to the corresponding I/O port. The following table lists the page bits.

| Page   | D7 | D6 | D5-D0 |

|--------|----|----|-------|

| Page 0 | 0  | 0  | 1/0   |

| Page 1 | 0  | 1  | 1/0   |

| Page 2 | 1  | 0  | 1/0   |

| Page 3 | 1  | 1  | 1/0   |

### 7.8.4 POL0 through POL2

These registers are accessible when Page 1 is selected. They allow interrupt polarity selection on a port-by-port and bit-by-bit basis. Writing a 1 to a bit position selects the rising edge detection interrupts. Writing a 0 to a bit position selects falling edge detection interrupts.

### 7.8.5 ENABO through ENAB2

These registers are accessible when Page 2 is selected. They allow for port-by-port and bit-by-bit enabling of the edge detection interrupts. When set to a 1, the edge detection interrupt is enabled for the corresponding port and bit. When cleared to 0, the bit's edge detection interrupt is disabled. Note that this register can be used to individually clear a pending interrupt by disabling and re-enabling the pending interrupt.

### 7.8.6 INT\_ID0 through INT\_ID2

These registers are accessible when Page 3 is selected. They are used to identify currently pending edge interrupts. A bit, when read as a 1, indicates that an edge of the polarity programmed into the corresponding polarity register has been recognized. Note that a write to this register (value ignored) clears ALL the pending interrupts in this register.

### 7.9 Watchdog Timer

The PPM-C412 features an advanced watchdog timer that can be used to guard against software lockups. Three interfaces are provided to the watchdog timer. The Advanced interface is the most flexible and recommended for new designs. The other two interface options are provided for software compatibility with older WINSYSTEMS single-board computers.

### 7.9.1 Advanced

Enable the watchdog timer in the BIOS Settings by entering a value for Watch-Dog Timeout on the Peripherals screen. Any non-zero value represents the number of minutes prior to reset during system boot. When the operating system is loaded, disable or reconfigure the watchdog in the application software.

NOTE WINSYSTEMS recommends using a long timeout if the watchdog is enabled when trying to boot any operating system.

Enable, disable, or reset the watchdog by writing the appropriate values to the configuration registers located at I/O addresses 565h and 566h. Enable the watchdog by writing a timeout value other than zero to the I/O address 566h and disable it by writing 00h to this I/O address. Service the watchdog timer by writing the desired timeout value to I/O port 566h. If the watchdog has not been serviced within the allotted time, the circuit resets the CPU.

Set the timeout value from 1 second to 256 minutes. If port 565h bit 7 equals 0, the timeout value written into I/O address 566h is in minutes. The timeout value written to address 566h is in seconds if port 565 bit 7 equals 1.

| Port Address | Port Bit 7<br>Value | Port Address | Value | Reset<br>Interval |

|--------------|---------------------|--------------|-------|-------------------|

| 565H         | Х                   | 566H         | 00h   | Disabled          |

| 565H         | 1                   | 566H         | 03h   | 3 seconds         |

| 565H         | 1                   | 566H         | 1Eh   | 30 seconds        |

| 565H         | 0                   | 566H         | 04h   | 4 minutes         |

| 565H         | 0                   | 566H         | 05h   | 5 minutes         |

### Watchdog timer examples

### 7.9.2 Standard

Enable or disable the watchdog via software by writing an appropriate timeout value to I/O port 1EEH.

| Port Address | Value | Reset Interval |

|--------------|-------|----------------|

| 1EEH         | 00h   | Disabled       |

|              | 01h   | 3 seconds      |

|              | 03h   | 30 seconds     |

|              | 05h   | 300 seconds    |

| 1EFH         | Any   | Reset timer    |

### 7.9.3 Legacy

The legacy watchdog timer has a fixed reset interval of 1.5 seconds. Enable the watchdog by writing 1 or disable it by writing a 0 to I/O port address 1D0.

| Port Address | Value | Reset Interval  |

|--------------|-------|-----------------|

| 1D0          | 00h   | Disabled        |

|              | 01h   | Enabled 1.5 sec |

| 1D8H         | Any   | Reset timer     |

### 7.10 Real-time Clock/Calendar

A real-time clock is used as the AT-compatible clock/calendar. It supports a number of features including periodic and alarm interrupt capabilities. In addition to the time and date-keeping functions, the system configuration is kept in CMOS RAM contained within the clock section. A battery must be enabled for the real-time clock to retain time and date during a power down.

### 7.11 SP1 Speaker

An on-board speaker, SP1, is available for sound generation.

### 7.12 Connectors

### 7.12.1 J1 SATA PWR SATA Power Connector

### **Layout and Pin Reference**

| Pin | Name               |  |  |  |  |

|-----|--------------------|--|--|--|--|

|     | ■ □ □ □<br>1 2 3 4 |  |  |  |  |

| 1   | +5V                |  |  |  |  |

| 2   | GND                |  |  |  |  |

| 3   | GND                |  |  |  |  |

| 4   | +12V               |  |  |  |  |

### Connectors

- PCB connector: Molex 22-11-2042 (SATA PWR)

- Mating connector: Molex 39-01-2105 (housing)

- Mating connector: Molex 08-55-0101 (crimp)

### 7.12.2 J3 Power and Reset

Power is applied to the PPM-C412 through the 8-pin Molex connector at **J3**. The definitions for **J3** are listed in the table below.

An optional reset button can be connected between pin 8 and ground. Momentary contact between pin 8 and ground causes the PPM-C412 to reset. There is also a reset push-button supplied on the CBL-251-G-1-1.5 Multi-I/O cable. This cable is includes in the cable set CBL-SET-412-1.

**Power fail reset:** A precision voltage comparator monitors the +5 V status. Upon detection of an out-of-tolerance condition, the board is reset. This action is critically important in the event of brown-out or power fail conditions. The reset circuit also ensures that the power is nominal before releasing reset. A reset condition occurs when  $V_{CC}$  drops between 4.6 V and 4.75 V for more than 150 ms.

### **Layout and Pin Reference**

| Pin | Name |   |   |   |   | Pin |   |   | Name |     |

|-----|------|---|---|---|---|-----|---|---|------|-----|

|     |      | 8 | 7 | 6 | 5 | 4   | 3 | 2 | 1    | ]   |

|     |      | 0 | 0 | 0 | 0 | 0   | 0 | 0 | 0    |     |

| 1   | -12V | ' |   |   |   | 5   |   |   | GN   | D   |

| 2   | +12\ | / |   |   |   | 6   |   |   | GN   | ID  |

| 3   | +5V  |   |   |   |   | 7   |   |   | GN   | ID  |

| 4   | +5V  |   |   |   |   | 8   |   |   | RES  | SET |

#### Connectors

- PCB connector: Molex 22-12-2084 (PWR)

- Mating connector: Molex 10-11-2083 (housing)

- Mating connector: Molex 08-55-0124 (crimp)

### 7.12.3 J4 External Battery Connector

An optional external battery, connected to **J4**, supplies the PPM-C412 board with standby power for the real-time clock and CMOS setup RAM. Extended temperature lithium batteries are available from WINSYSTEMS, part numbers:

- BAT-LTC-E-36-16-1

- BAT-LTC-E-36-27-1

A power supervisory circuit contains the voltage sensing circuit and an internal power switch to route the battery or standby voltage to the circuits selected for backup. The battery automatically switches on when the  $V_{\rm CC}$  of the systems drops below the battery voltage and off when  $V_{\rm CC}$  returns to normal.

### **Layout and Pin Reference**

|     | Pin | Name        | Description           |

|-----|-----|-------------|-----------------------|

|     | 1   | GND         | Ground                |

| 1 💽 | 2   | VBAT (BAT+) | Battery voltage input |

| 3   |     | GND         | Ground                |

|     |     |             |                       |

#### Connectors

- PCB connector: Molex 22-11-2032

- Mating connector: Molex 22-01-3037 (housing)

- Mating connector: Molex 08-56-0109 or 08-56-0110 (crimp)

WINSYSTEMS battery BAT-LTC-E-36-16-1 and BAT-LTC-E-36-27-1 (connected to **J4**) simplify these connections to the board.

### BAT-LTC-E-36-16-1

BAT-LTC-E-36-27-1

### 7.12.4 J5/J6 PC104 PC/104 Bus

The PC/104 bus is electrically equivalent to the 8- and 16-bit ISA bus. Standard PC/104 I/O cards can be populated on PPM-C412's PC/104 bus, located at J5 and J6. The interface does not support hot swap capability. The PC/104 bus connector pin definitions are provided here for reference. Refer to the PC/104 Specification <<u>Not in this doc>></u> for specific signal and mechanical specifications.

|         | Pin | Name     | Pin | Name             | Pin | Name    | Pin | Name     |          |  |

|---------|-----|----------|-----|------------------|-----|---------|-----|----------|----------|--|

|         |     | 1        |     | A1 IOCHK# B1 GND | GND | J6      |     |          |          |  |

|         |     |          |     |                  | A2  | SD7     | B2  | RESET    |          |  |

|         |     |          |     |                  | A3  | SD6     | B3  | +5V      | -        |  |

|         |     |          |     |                  | A4  | SD5     | B4  | IRQ9     | _        |  |

|         |     |          |     |                  | A5  | SD4     | B5  | NC       | -        |  |

|         |     |          |     |                  | A6  | SD3     | B6  | DRQ2     | _        |  |

|         |     |          |     |                  | A7  | SD2     | B7  | -12V     | _        |  |

| 0 = - 0 |     |          |     |                  | A8  | SD1     | B8  | OWS      | _        |  |

|         | D0  | GND      | C0  | GND              | A9  | SD0     | B9  | +12V     |          |  |

|         | D1  | MEMCS16# | C1  | SBHE#            | A10 | IOCHRDY | B10 | GND      | A1 00 B1 |  |

| 0 CO    | D2  | IOCS16#  | C2  | LA23             | A11 | AEN     | B11 | SMEMW#   |          |  |

|         | D3  | IRQ10    | C3  | LA22             | A12 | SA19    | B12 | SMEMR#   |          |  |

|         | D4  | IRQ11    | C4  | LA21             | A13 | SA18    | B13 | IOW#     |          |  |

|         | D5  | IRQ12    | C5  | LA20             | A14 | SA17    | B14 | IOR#     |          |  |

|         | D6  | IRQ15    | C6  | LA19             | A15 | SA16    | B15 | DACK3#   |          |  |

|         | D7  | IRQ14    | C7  | LA18             | A16 | SA15    | B16 | DRQ3     |          |  |

| 9 🗄 C19 | D8  | DACK0#   | C8  | LA17             | A17 | SA14    | B17 | DACK1#   |          |  |

|         | D9  | DRQ0     | C9  | MEMR#            | A18 | SA13    | B18 | DRQ1     |          |  |

|         | D10 | DACK5#   | C10 | MEMW#            | A19 | SA12    | B19 | REFRESH# |          |  |

|         | D11 | DRQ5     | C11 | SD8              | A20 | SA11    | B20 | BCLK     |          |  |

|         | D12 | DACK6#   | C12 | SD9              | A21 | SA10    | B21 | IRQ7     |          |  |

|         | D13 | DRQ6     | C13 | SD10             | A22 | SA9     | B22 | IRQ6     |          |  |

|         | D14 | DACK7#   | C14 | SD11             | A23 | SA8     | B23 | IRQ5     | A32 🖽 B3 |  |

|         | D15 | DRQ7     | C15 | SD12             | A24 | SA7     | B24 | IRQ4     | _        |  |

|         | D16 | +5V      | C16 | SD13             | A25 | SA6     | B25 | IRQ3     |          |  |

|         | D17 | MASTER#  | C17 | SD14             | A26 | SA5     | B26 | DACK2#   | _        |  |

|         | D18 | GND      | C18 | SD15             | A27 | SA4     | B27 | TC       |          |  |

|         | D19 | GND      | C19 | GND              | A28 | SA3     | B28 | BALE     | _        |  |

|         |     |          |     | ·                | A29 | SA2     | B29 | +5V      | 7        |  |

|         |     |          |     |                  | A30 | SA1     | B30 | OSC      | 7        |  |

|         |     |          |     |                  | A31 | SA0     | B31 | GND      | 7        |  |

|         |     |          |     |                  | A32 | GND     | B32 | GND      | 1        |  |

### **Layout and Pin Reference**

### **Additional Information**

- Rows C and D are not required on 8-bit modules.

- B10 and C19 are key locations. WINSYSTEMS uses key pins as connections to GND.

- Signal timing and function are as specified in ISA specification.

- Signal source/sink current differ from ISA values.

### Connectors

- 64-pin TEKA SBL PC232-A-1A7-M

- 40-pin TEKA SBL PC220-A-1A7-M

There are no keys in the connector, and no cut pins.

### 7.12.5 J7 Multi I/O Connector

The Multi-IO connector includes the PS/2 keyboard, PS/2 mouse, four serial, LPT, ENET2, and PBReset, all terminated via the connector at **J7**.