# JDI

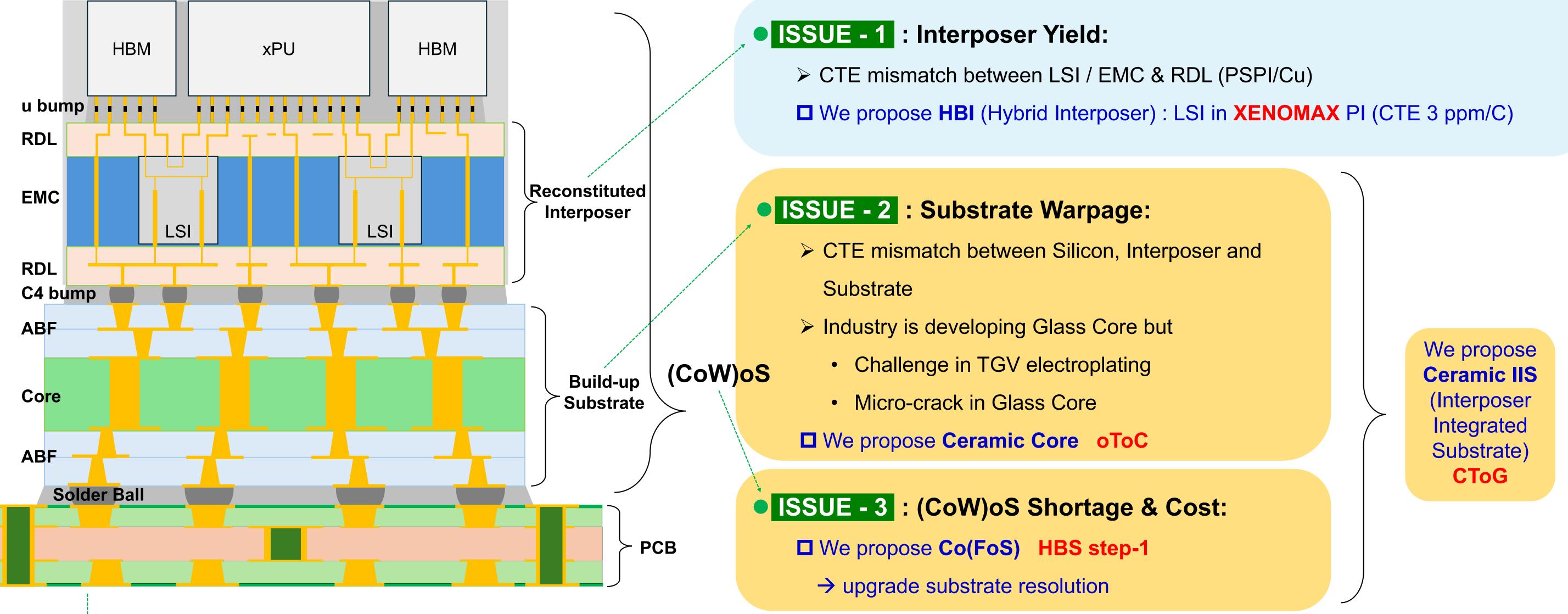

# Challenges of CoWoS and Al Server

## **ISSUE - 4** : Complicated stack-up limits the performance of AI server

- $\succ$  Electrical interconnect : massive and long electrical paths  $\rightarrow$  High power consumption

We propose n\*(CoR)o(FoS) > Optical interconnect : Industry is developing CPO  $\rightarrow$  Challenges in Fiber/Chip connect and networking U We propose eo-HBS (Hybrid Substrate) : RDL(e) & Waveguide(o) on a large substrate as Motherboard HBS step-3

## HBS step-2

## PANEL JEMI 方略電子

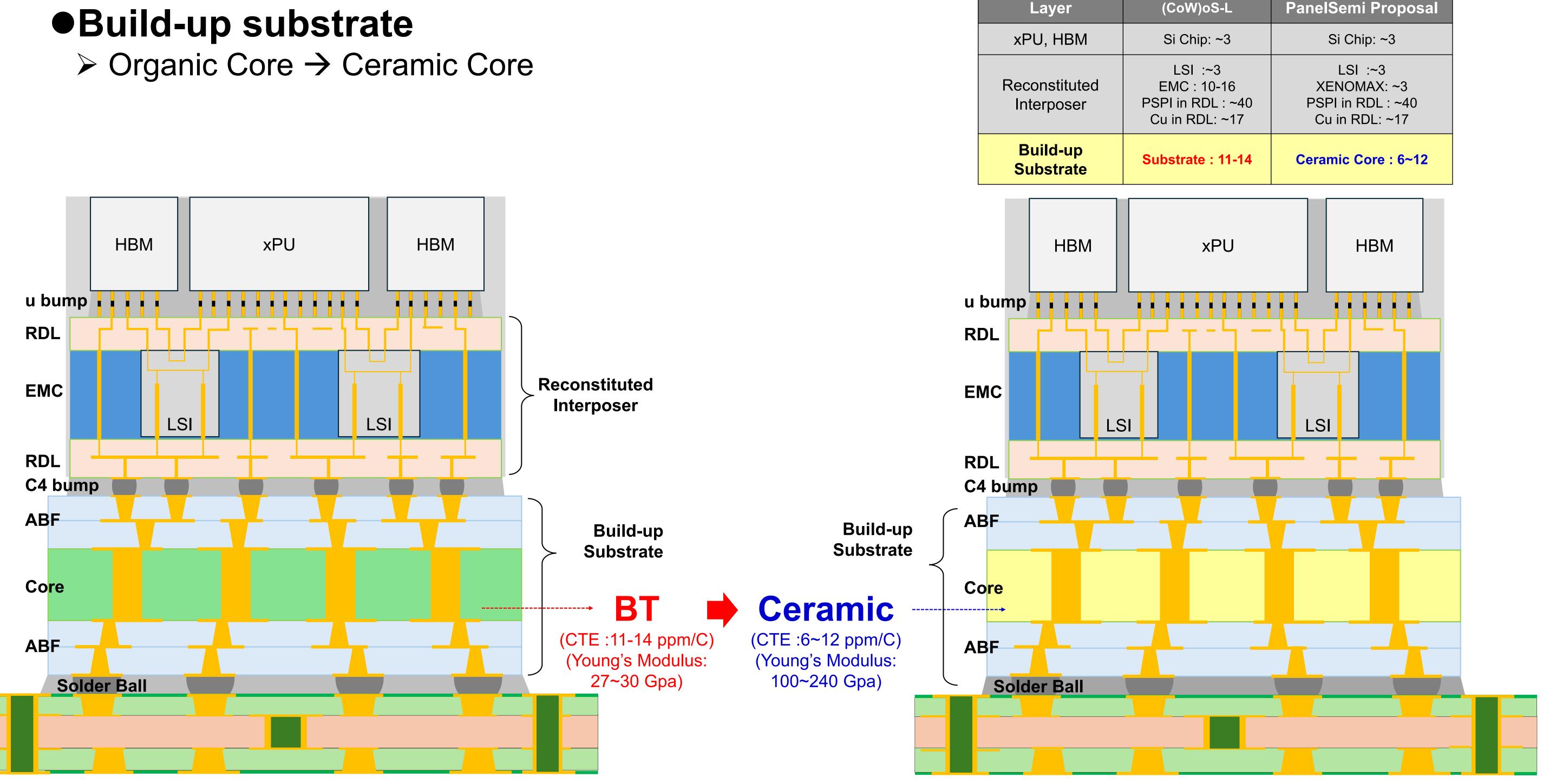

## **PanelSemi Proposal for Issue-2**

## PANEL SEMI 方略電子

| oW)oS-L                                        | PanelSemi Proposal                                            |

|------------------------------------------------|---------------------------------------------------------------|

| Chip: ~3                                       | Si Chip: ~3                                                   |

| SI :~3<br>C : 10-16<br>n RDL : ~40<br>RDL: ~17 | LSI :~3<br>XENOMAX: ~3<br>PSPI in RDL : ~40<br>Cu in RDL: ~17 |

| rate : 11-14                                   | Ceramic Core : 6~12                                           |

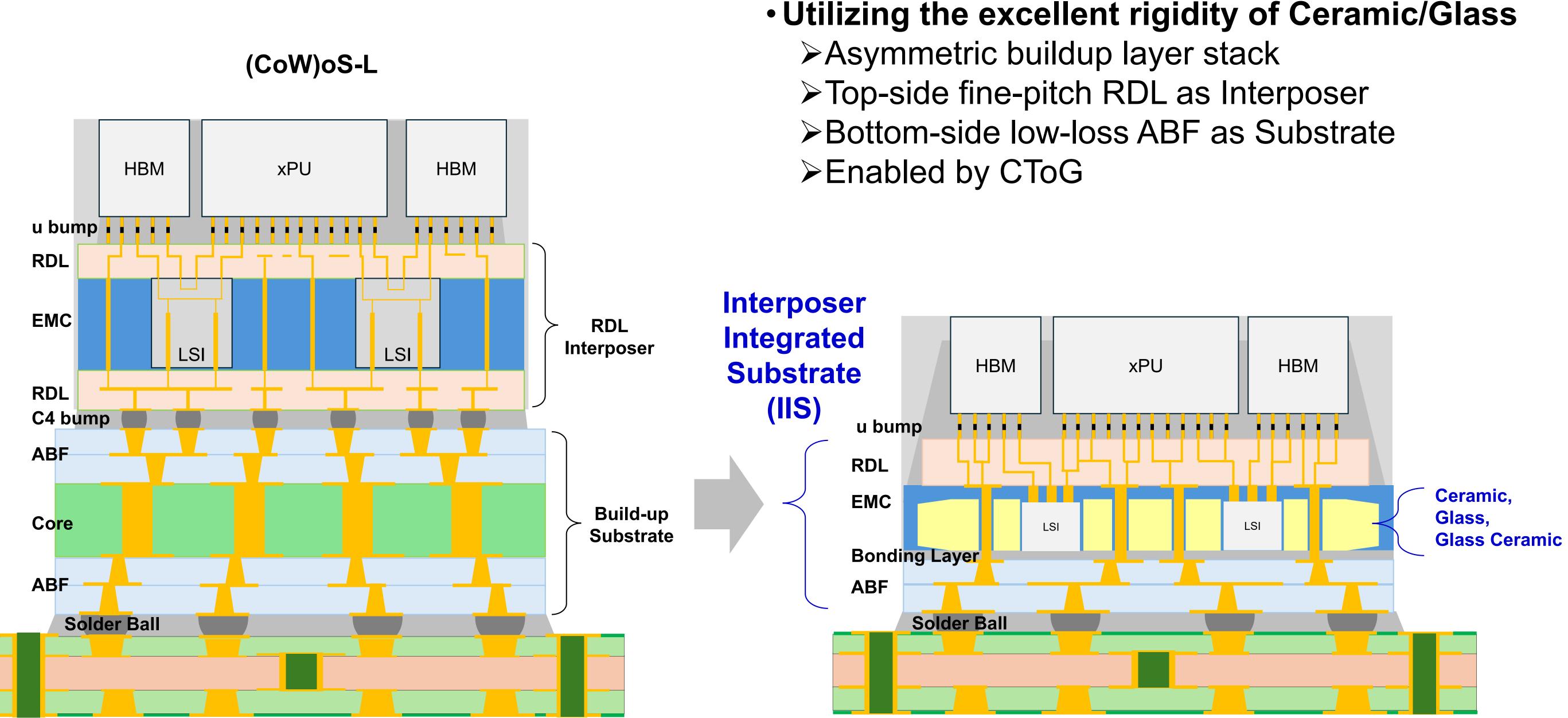

## **Ceramic/Glass IIS (Interposer Integrated Substrate)**

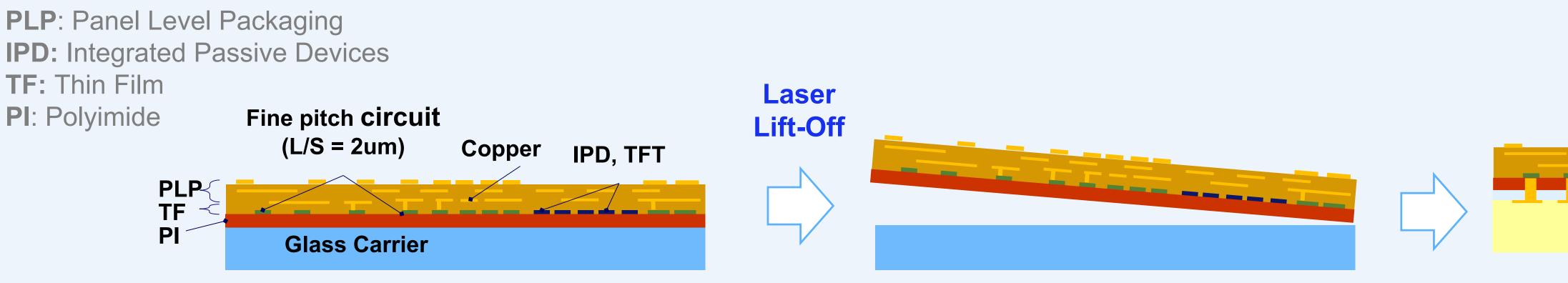

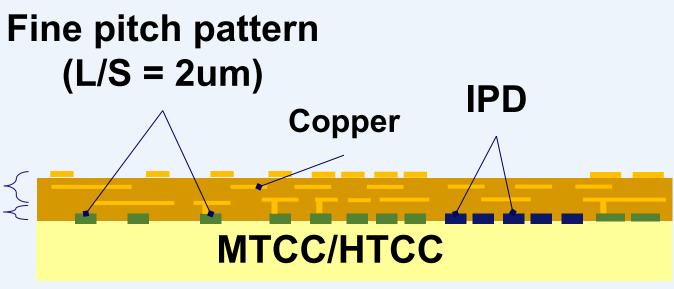

## Fine-pitch Ceramic Substrate & FoS (Film on Substrate)

## Fine-pitch Ceramic Substrate Process

Fabricate fine-pitch pattern (L/S = 2um) directly on MTCC/HTCC substrate by WLP ecosystem

WLP TF

**WLP**: Wafer Level Packaging

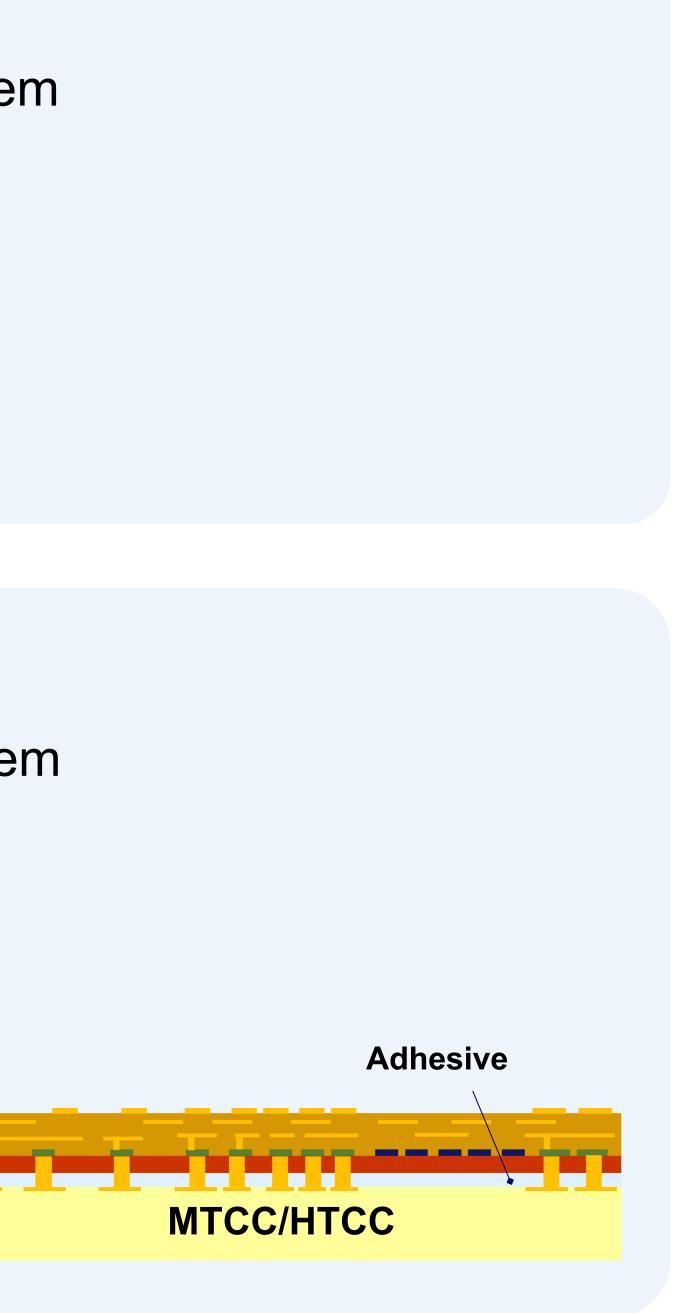

## Fine-pitch FoS (Film on Substrate) Process

$\geq$  Fabricate fine-pitch pattern (L/S = 2 um) onto PI (XENOMAX PI) on Glass by PLP ecosystem

>Lift off PI w/ pattern from glass then laminate PI w/ pattern onto MTCC/HTCC substrate

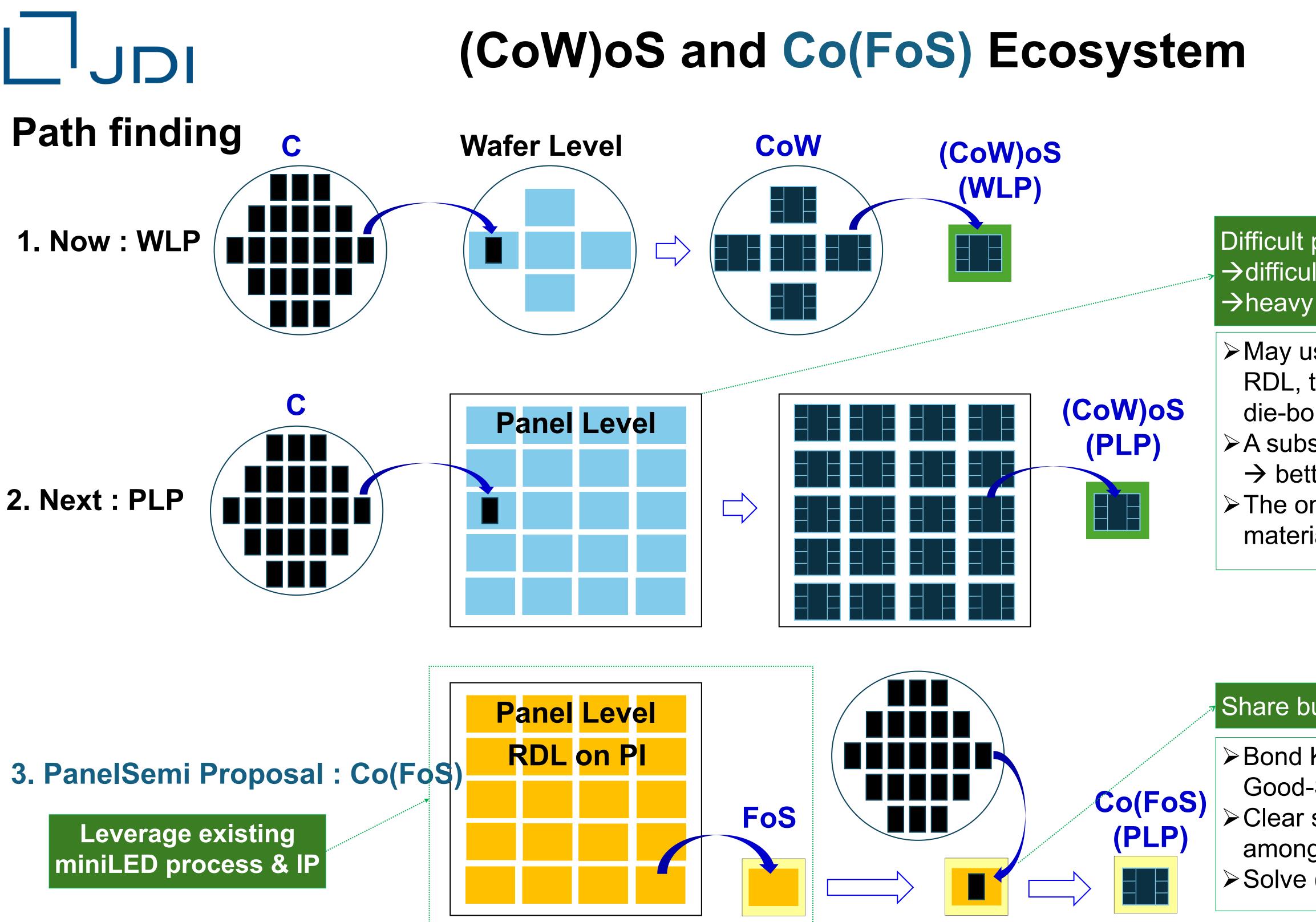

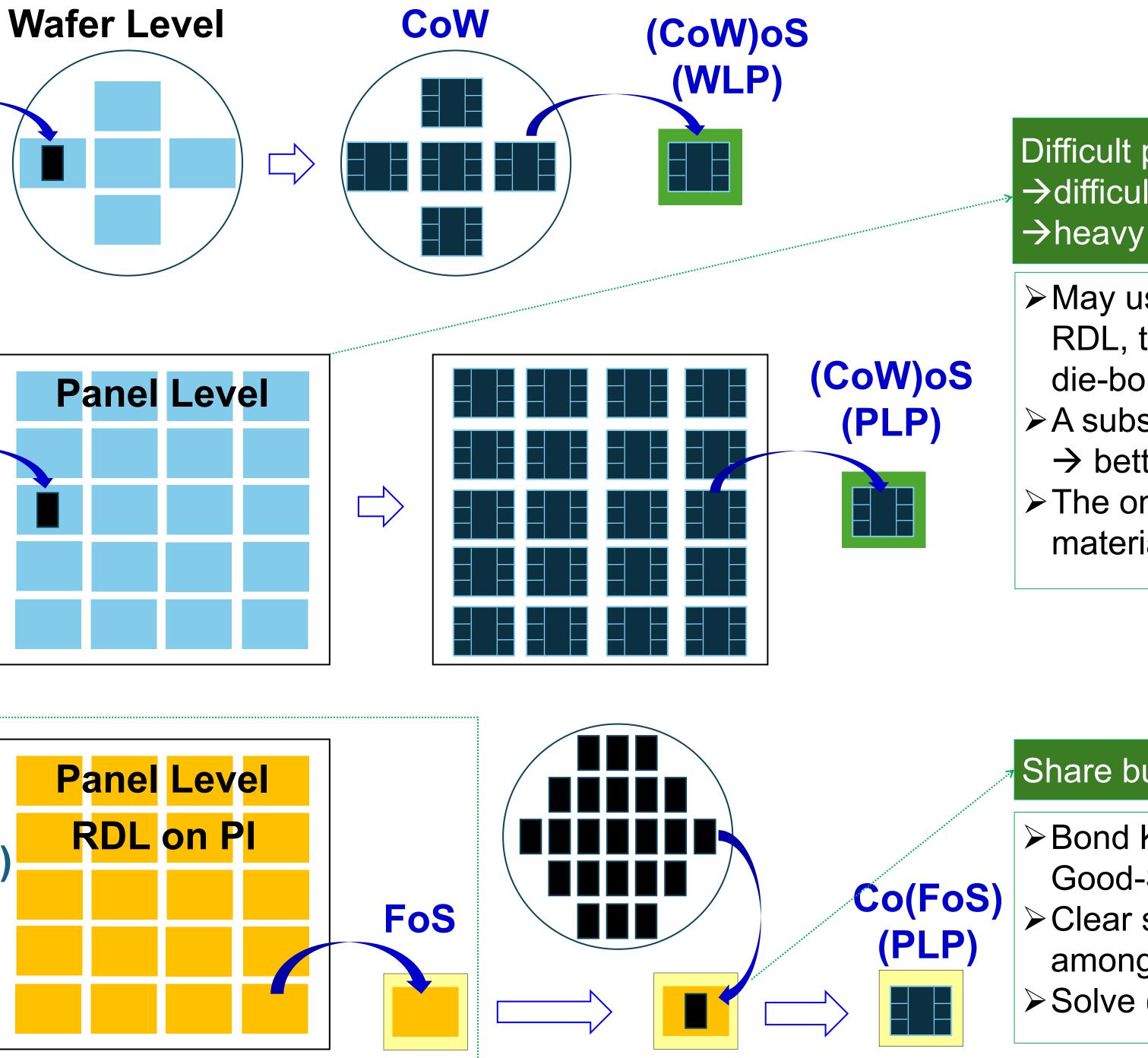

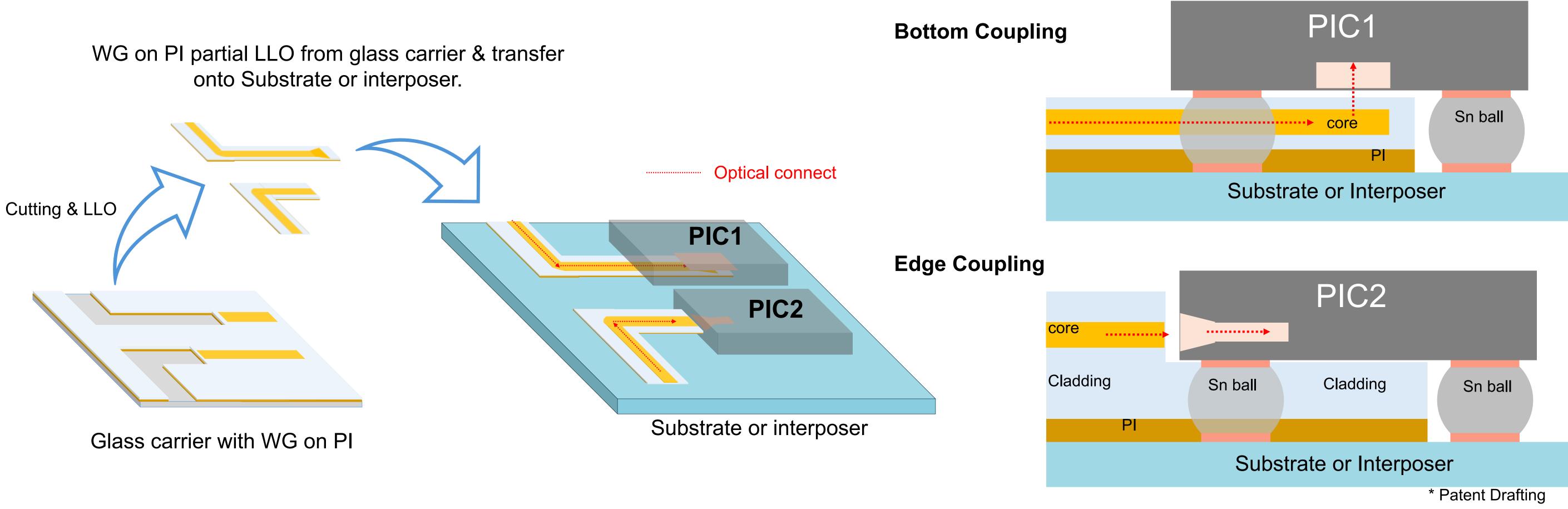

## Difficult processes after die-bond $\rightarrow$ difficult for OSAT (Yield responsibility) $\rightarrow$ heavy burden for Chip maker

> May use TFT G4.5 (730x920mm) for RDL, then cut it into 600x600mm for die-bond, molding,...

> A substrate larger than 600x600mm  $\rightarrow$  better uniformity, less warpage > The only waste of BOM is glass, other materials cover 600x600mm only

## Share burden by Substrate & OSAT

Bond Known-Good-Die on Known-Good-Substrate  $\rightarrow$  high yield > Clear supply-chain responsibilities among Chip, Substrate and OSAT Solve (CoW)oS shortage & cost issues

#

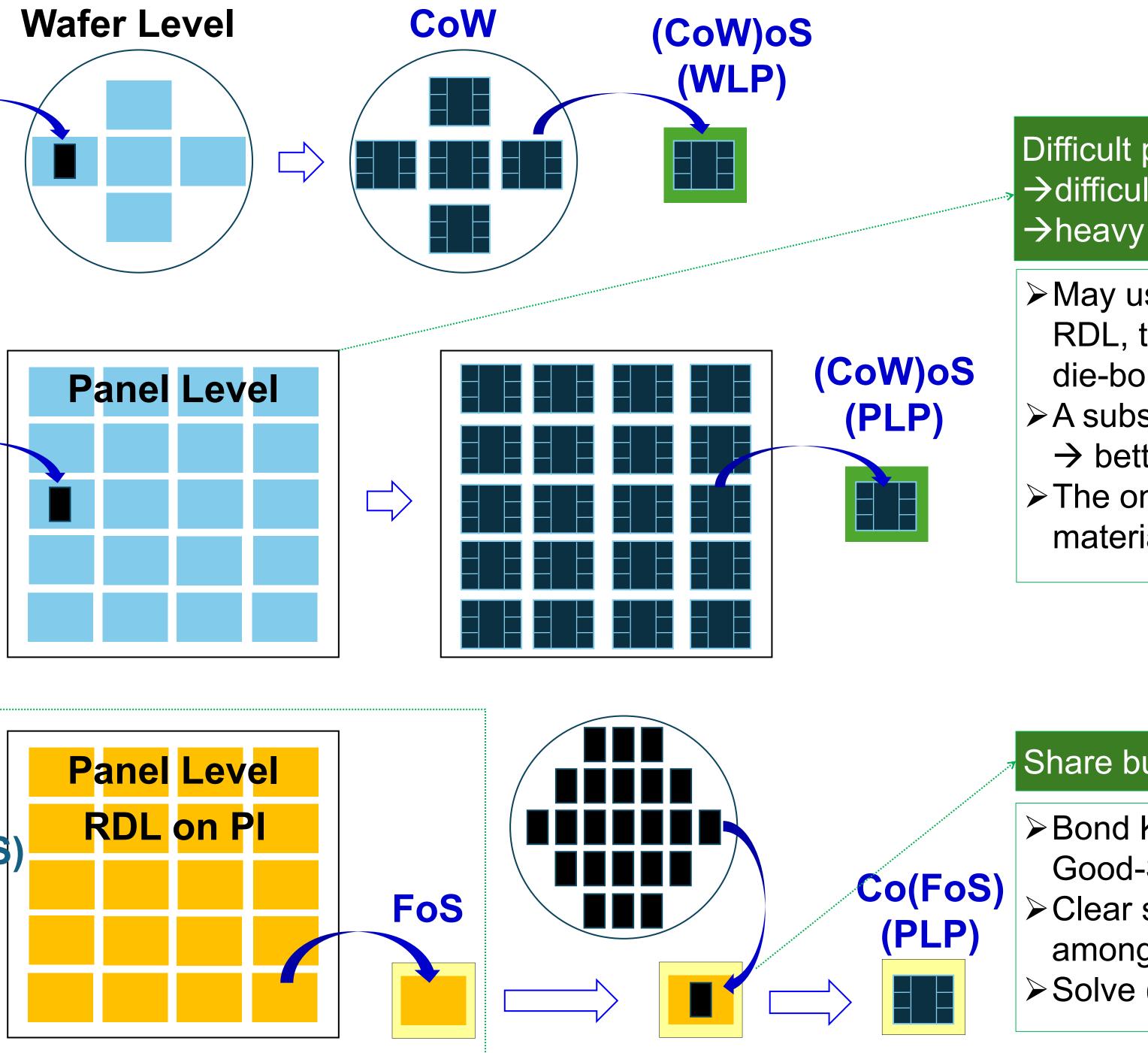

# **CPO - Waveguide on PI (Partial Transfer)**

• WG on PI could be laser cutting & partial transfer to Substrate or Interposer. The partially transferred WG on PI can avoid the IC electrical connection pad. • Bottom coupling & Edge coupling can be achieved by adjusting the cladding thickness according to the type of Waveguide material.

onto Substrate or interposer.

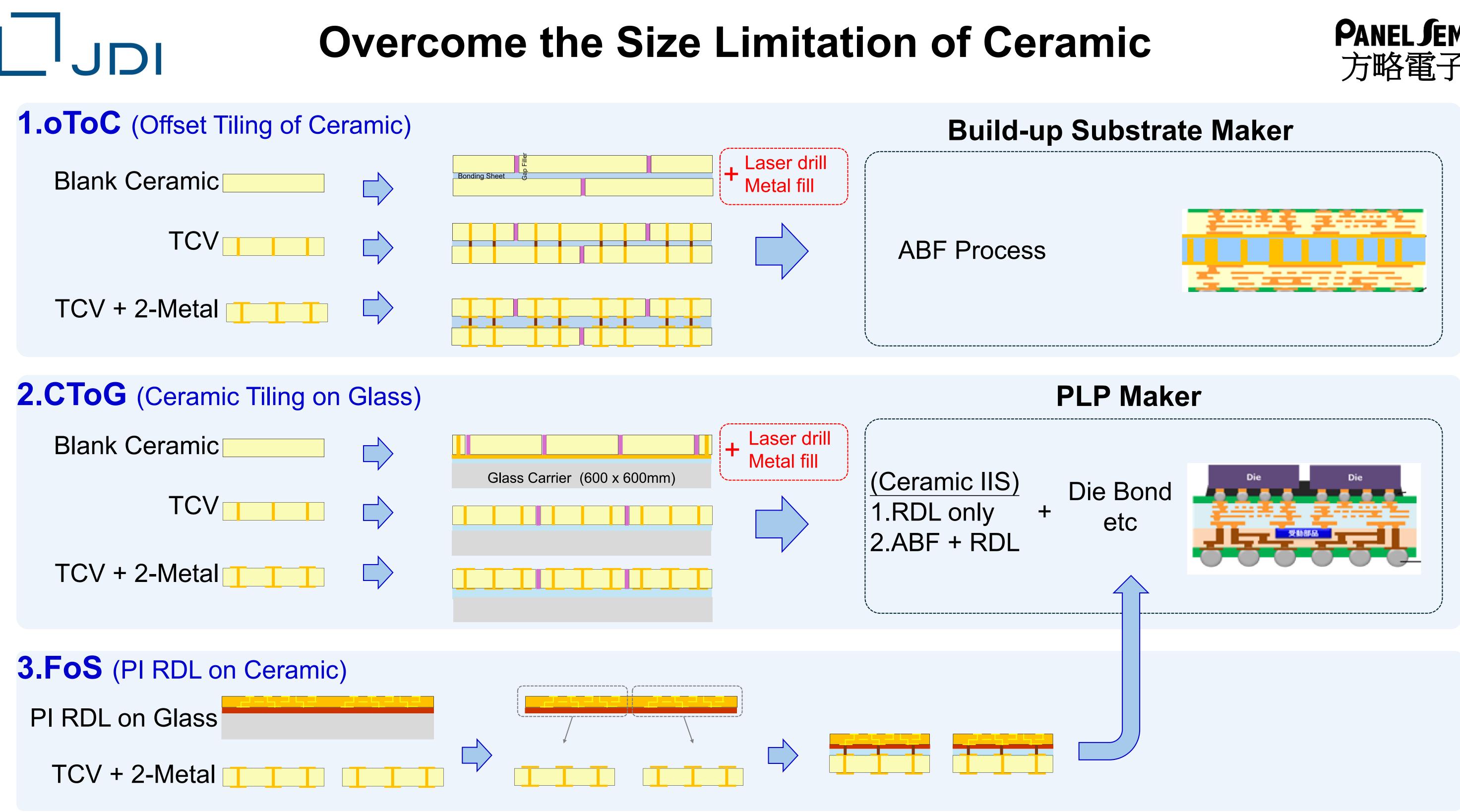

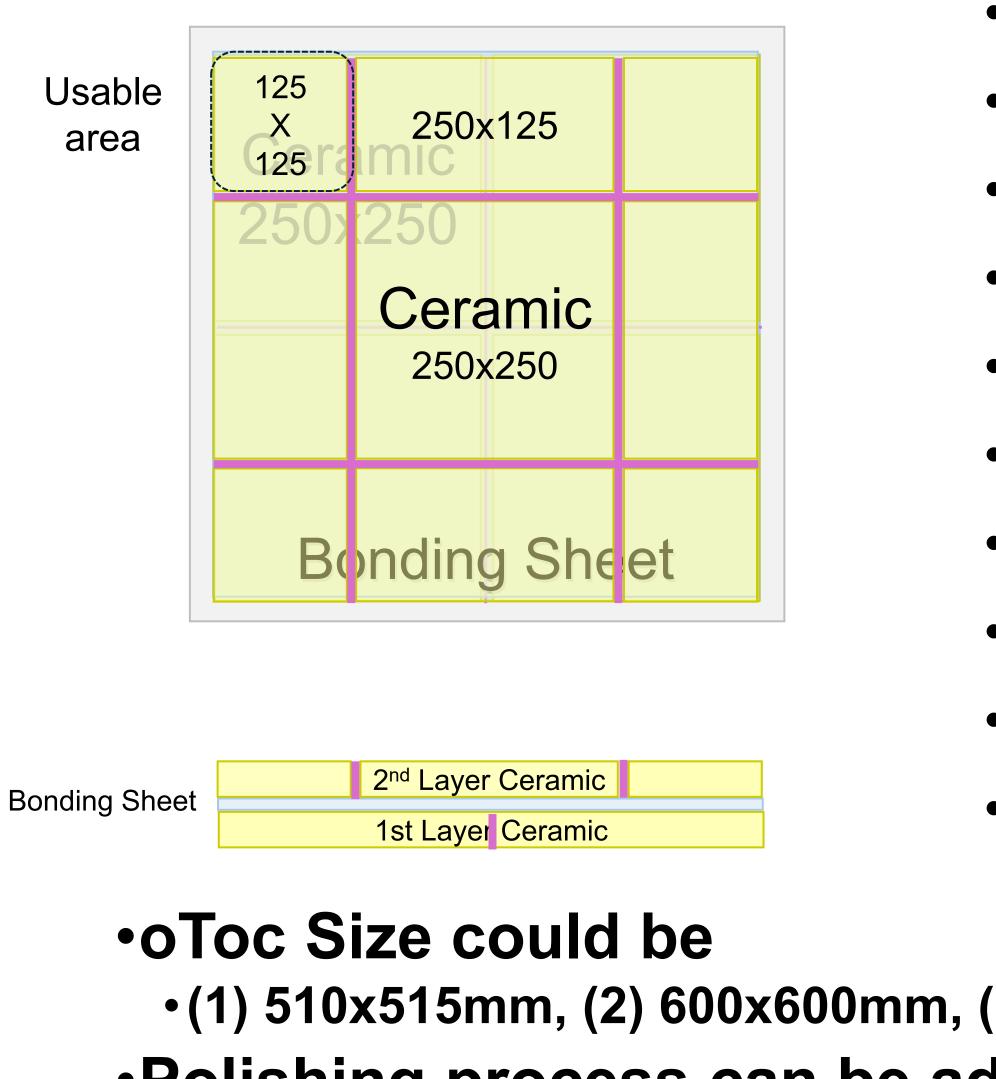

# **Offset Tiling of Ceramic (oToC)**

•oToC is a method of tiling ceramic substrates to achieve a larger size, which is suitable for the double-sided process commonly used by build-up substrate makers. It may also be used for the single-sided process by TFT or PLP makers.

- Prepare a glass carrier

- Attach bonding sheet to the glass carrier

- •Attach ceramic tiles (1st Layer) onto the carrier

- •Dispense gap filler between the ceramic tiles

- •Attach another bonding sheet

- Attach ceramic tiles (2nd Layer) with an offset to the 1st Layer

- •Dispense gap filler between the ceramic tiles

- Remove the carrier

- •4 x 4 usable areas, each 125 x 125 mm

- Cross-Section

•(1) 510x515mm, (2) 600x600mm, (3) 620x750mm [G3.5 TFT], (4) 730x920mm [G4.5 TFT] above and more. Polishing process can be added if needed.

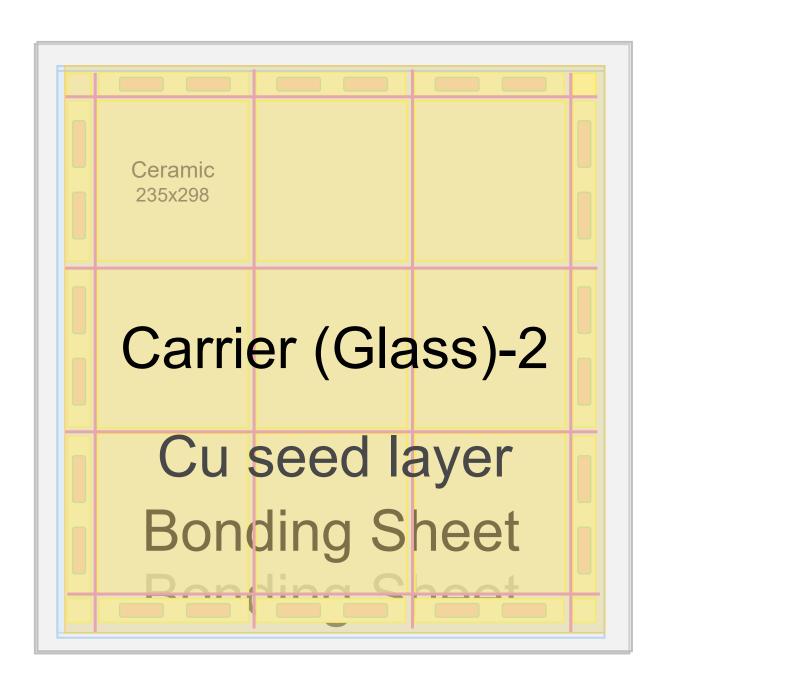

# **Ceramic Tiling on Glass (CToG)**

## •CToG Size could be (1) 730x920mm, (2) 600x600mm, (3) 510x515mm and more. Polishing process can be added if needed.

•CToG is a method of tiling ceramic substrates onto a larger size glass carrier.

- •Prepare a glass carrier-1

- •Attach bonding sheet to the glass carrier-1

- Attach ceramic tiles onto the carrier

- •Attach ceramic bars with through via onto the carrier

- Attach dummy ceramic tiles at corners

- •Dispense gap filler between the ceramic tiles Deposit Cu seed layer

- Attach bonding sheet above Cu seed layer

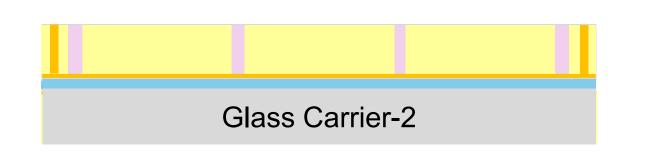

- Attach glass carrier-2 on top and remove glass carrier-1

- Cross-Section