THE ELECTRICAL ENGINEERING HANDBOOK

Computers, Software Engineering, and Digital Devices

Edited by Richard C. Dorf

Taylor & Francis

#### Purpose

The purpose of *The Electrical Engineering Handbook*, *3rd Edition* is to provide a ready reference for the practicing engineer in industry, government, and academia, as well as aid students of engineering. The third edition has a new look and comprises six volumes including:

Circuits, Signals, and Speech and Image Processing Electronics, Power Electronics, Optoelectronics, Microwaves, Electromagnetics, and Radar Sensors, Nanoscience, Biomedical Engineering, and Instruments Broadcasting and Optical Communication Technology Computers, Software Engineering, and Digital Devices Systems, Controls, Embedded Systems, Energy, and Machines

Each volume is edited by Richard C. Dorf, and is a comprehensive format that encompasses the many aspects of electrical engineering with articles from internationally recognized contributors. The goal is to provide the most up-to-date information in the classical fields of circuits, signal processing, electronics, electromagnetic fields, energy devices, systems, and electrical effects and devices, while covering the emerging fields of communications, nanotechnology, biometrics, digital devices, computer engineering, systems, and biomedical engineering. In addition, a complete compendium of information regarding physical, chemical, and materials data, as well as widely inclusive information on mathematics is included in each volume. Many articles from this volume and the other five volumes have been completely revised or updated to fit the needs of today and many new chapters have been added.

The purpose of this volume, *Computers, Software Engineering, and Digital Devices*, is to provide a ready reference to subjects in the fields of digital and logical devices, displays, testing, software, and computers. Here we provide the basic information for understanding these fields. We also provide information about the emerging fields of programmable logic, hardware description languages, and parallel computing.

#### Organization

The information is organized into three sections. The first two sections encompass 20 chapters and the last section summarizes the applicable mathematics, symbols, and physical constants.

Most articles include three important and useful categories: defining terms, references, and further information. *Defining terms* are key definitions and the first occurrence of each term defined is indicated in boldface in the text. The definitions of these terms are summarized as a list at the end of each chapter or article. The *references* provide a list of useful books and articles for follow-up reading. Finally, *further information* provides some general and useful sources of additional information on the topic.

#### **Locating Your Topic**

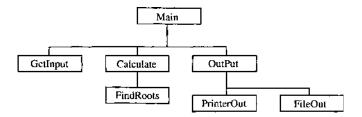

Numerous avenues of access to information are provided. A complete table of contents is presented at the front of the book. In addition, an individual table of contents precedes each section. Finally, each chapter begins with its own table of contents. The reader should look over these tables of contents to become familiar with the structure, organization, and content of the book. For example, see Section II: Computer Engineering,

then Chapter 17: Parallel Processors, and then Chapter 17.2: Parallel Computing. This tree-and-branch table of contents enables the reader to move up the tree to locate information on the topic of interest.

Two indexes have been compiled to provide multiple means of accessing information: subject index and index of contributing authors. The subject index can also be used to locate key definitions. The page on which the definition appears for each key (defining) term is clearly identified in the subject index.

The Electrical Engineering Handbook, 3rd Edition is designed to provide answers to most inquiries and direct the inquirer to further sources and references. We hope that this handbook will be referred to often and that informational requirements will be satisfied effectively.

#### Acknowledgments

This handbook is testimony to the dedication of the Board of Advisors, the publishers, and my editorial associates. I particularly wish to acknowledge at Taylor & Francis Nora Konopka, Publisher; Helena Redshaw, Editorial Project Development Manager; and Richard Tressider, Project Editor. Finally, I am indebted to the support of Elizabeth Spangenberger, Editorial Assistant.

Richard C. Dorf Editor-in-Chief

## Editor-in-Chief

**Richard C. Dorf,** Professor of Electrical and Computer Engineering at the University of California, Davis, teaches graduate and undergraduate courses in electrical engineering in the fields of circuits and control systems. He earned a Ph.D. in electrical engineering from the U.S. Naval Postgraduate School, an M.S. from the University of Colorado, and a B.S. from Clarkson University. Highly concerned with the discipline of electrical engineering and its wide value to social and economic needs, he has written and lectured internationally on the contributions and advances in electrical engineering.

Professor Dorf has extensive experience with education and industry and is professionally active in the fields of robotics, automation, electric circuits, and communications. He has served as a visiting professor at the University of Edinburgh, Scotland; the Massachusetts Institute of Technology; Stanford University; and the University of California, Berkeley.

Professor Dorf is Fellow of The Institute of Electrical and Electronics Engineers and a Fellow of the American Society for Engineering Education. Dr. Dorf is widely known to the profession for his *Modern Control Systems*, *10th Edition* (Addison-Wesley, 2004) and *The International Encyclopedia of Robotics* (Wiley, 1988). Dr. Dorf is also the co-author of *Circuits, Devices and Systems* (with Ralph Smith), *5th Edition* (Wiley, 1992), and *Electric Circuits, 7th Edition* (Wiley, 2006). He also is author of *Technology Ventures* (McGraw-Hill, 2005) and *The Engineering Handbook, 2nd Edition* (CRC Press, 2005).

## Advisory Board

**Frank Barnes** University of Colorado Boulder, Colorado

**Joseph Bronzino** Trinity College Hartford, Connecticut

**Wai-Kai Chen** University of Illinois Chicago, Illinois

**Delores Etter** United States Naval Academy Annapolis, Maryland

**Lyle Feisel** State University of New York Binghamton, New York **William Kersting** New Mexico State University Las Cruces, New Mexico

**Vojin Oklobdzia** University of California Davis, California

John V. Oldfield Syracuse University Syracuse, New York

**Banmali Rawat** University of Nevada Reno, Nevada **Richard S. Sandige** California Polytechnic State University San Luis Obispo, California

**Leonard Shaw** Polytechnic University Brooklyn, New York

**John W. Steadman** University of South Alabama Mobile, Alabama

**R. Lal Tummala** Michigan State University East Lansing, Michigan

## Contributors

**M. Abdelguerfi** University of New Orleans New Orleans, Louisiana

**Cajetan M. Akujuobi** Prairie View A&M University Prairie View, Texas

**Carl A. Argila** Software Engineering Consultant Pico Rivera, California

**B.R. Bannister** University of Hull (retired) Hull, U.K.

**Bill D. Carroll** University of Texas Arlington, Texas

**Michael D. Ciletti** University of Colorado Colorado Springs, Colorado

**George A. Constantinides** Imperial College of Science London, U.K.

J. Arlin Cooper Sandia National Laboratories Albuquerque, New Mexico

Edward W. Czeck Chrysatis Symbolic Design North Billerica, Massachusetts

**Bulent I. Dervisoglu** Silicon Graphics, Inc. Mountain View, California

**R. Eskicioglu** University of Alberta Edmonton, Canada **James M. Feldman** Northeastern University Boston, Massachusetts

**Tse-yun Feng** Pennsylvania State University University Park, Pennsylvania

**James F. Frenzel** University of Idaho Moscow, Idaho

**Raphael Finkel** University of Kentucky Lexington, Kentucky

James M. Gilbert University of Hull Hull, U.K.

**Peter Graham** University of Minnesota Saint Paul, Minnesota

**Chris G. Guy** University of Reading Reading, U.K.

**Carl Hamacher** Queen's University Kingston, Canada

**H.S. Hinton** Utah State University Logan, Utah

**Barry W. Johnson** University of Virginia Charlottesville, Virginia

**Anna M. Johnston** Sandia National Laboratories Albuquerque, New Mexico **Paul C. Jorgensen** Grand Valley State University Rockford, Michigan

**Miro Kraetzl** Defence Science and Technology Organisation Salisbury, Australia

Dhammika Kurumbalapitiya Harvey Mudd College Claremont, California

**Peter A. Lee** East of England Development Agency Cambridge, U.K.

Young Choon Lee University of Sydney Sydney, Australia

**Ted G. Lewis** Naval Postgraduate School Monterey, California

**Albert A. Liddicoat** California Polytechnic State University San Luis Obispo, California

**Jay Liebowitz** Johns Hopkins University Rockville, Maryland

**M. Mansuripur** University of Arizona Tucson, Arizona

**Johannes J. Martin** University of New Orleans New Orleans, Louisiana

James E. Morris Portland State University Lake Oswego, Oregon **Gregory L. Moss** Purdue University West Lafayette, Indiana

**Franco P. Preparata** Brown University Providence, Rhode Island

**W. David Pricer** Pricer Business Services Charlotte, Vermont

**Jacques Raymond** University of Ottawa Ottawa, Canada

**Evelyn P. Rozanski** Rochester Institute of Technology Rochester, New York

**Matthew N.O. Sadiku** Prairie View A&M University Prairie View, Texas

**Richard S. Sandige** California Polytechnic State University San Luis Obispo, California

Nan C. Schaller Rochester Institute of Technology Rochester Center, New York **Michaela Serra** University of Victoria Victoria, Canada

**Mostafa Hashem Sherif** AT&T Tinton Falls, New Jersey

**Solomon Sherr** Westland Electronics Old Chatham, New York

**Lynne A. Slivovsky** California Polytechnic State University San Luis Obispo, California

**John Staudhammer** University of Florida Gainesville, Florida

**Ronald J. Tallarida** Temple University Philadelphia, Pennsylvania

**Charles W. Therrien** Naval Postgraduate School Monterey, California

**Richard F. Tinder** Washington State University Pullman, Washington **Zvonko Vranesic** University of Toronto Toronto, Canada

**Larry F. Weber** The Society for Information Highland, New York

**D.G. Whitehead** University of Hull Hull, U.K.

**Phillip J. Windley** Brigham Young University Provo, Utah

**S.N. Yanushkevich** University of Calgary Calgary, Canada

**Safwat Zaky** University of Toronto Toronto, Canada

**Albert Y. Zomaya** University of Sydney Sydney, Australia

#### **SECTION I** Digital Devices

#### 1 Logic Elements

- 1.1 IC Logic Family Operation and Characteristics Gregory L. Moss

- 1.2 Logic Gates (IC) Peter Graham

- 1.3 Bistable Devices Richard S. Sandige and Lynne A. Slivovsky

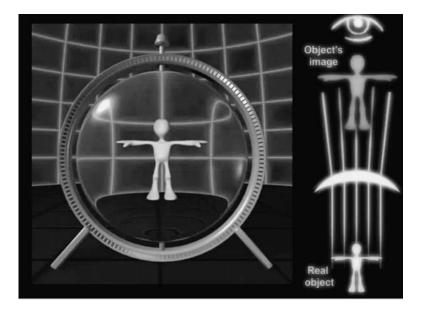

- 1.4 Optical Devices H.S. Hinton

#### 2 Memory Devices

- 2.1 Integrated Circuits (RAM, ROM) W. David Pricer

- 2.2 Magnetic Tape *Peter A. Lee*

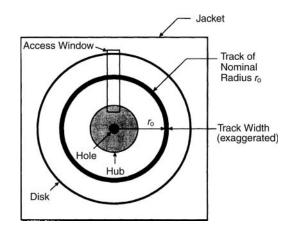

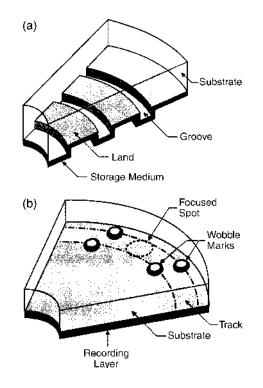

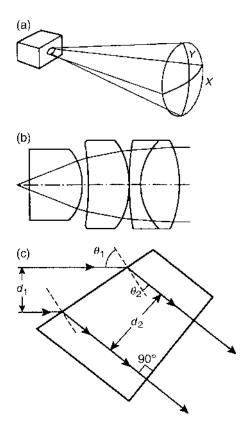

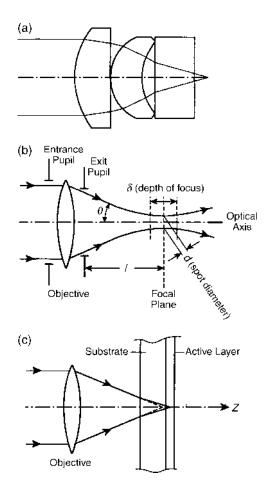

- 2.3 Magneto-Optical Disk Data Storage M. Mansuripur

#### 3 Logical Devices

- 3.1 Combinational Networks and Switching Algebra Franco P. Preparata

- 3.2 Logic Circuits Richard S. Sandige and Albert A. Liddicoat

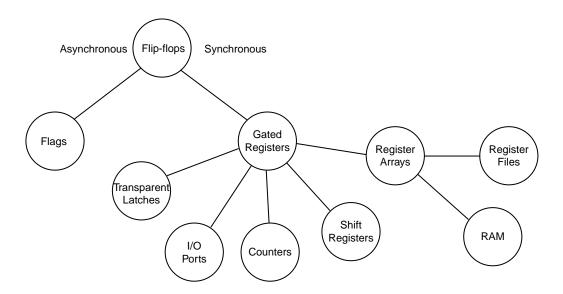

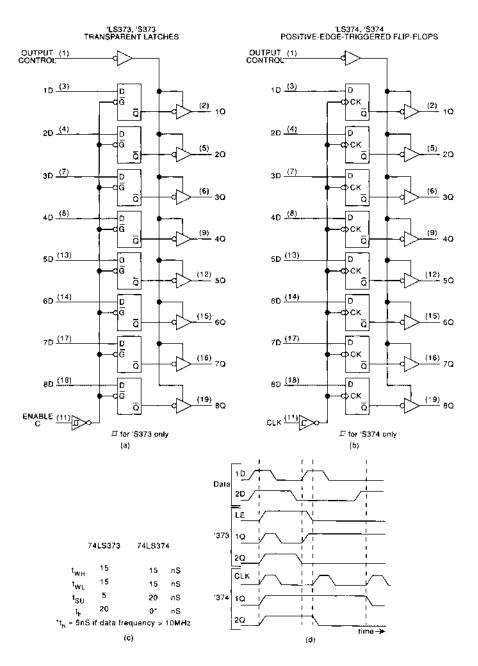

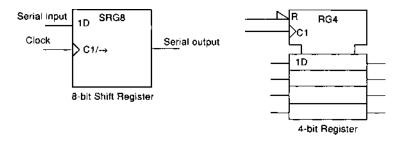

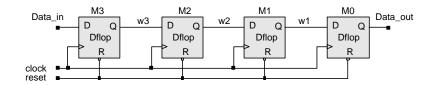

- 3.3 Registers and Their Applications B.R. Bannister, D.G. Whitehead, and James M. Gilbert

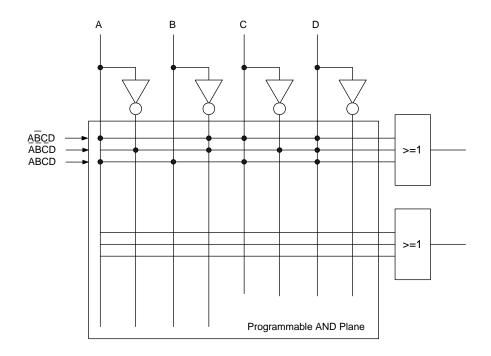

- 3.4 Programmable Arrays George A. Constantinides

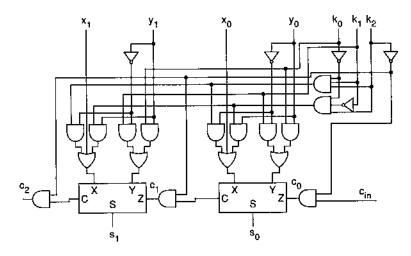

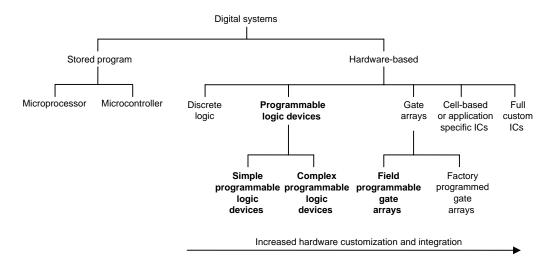

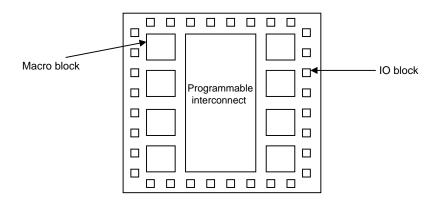

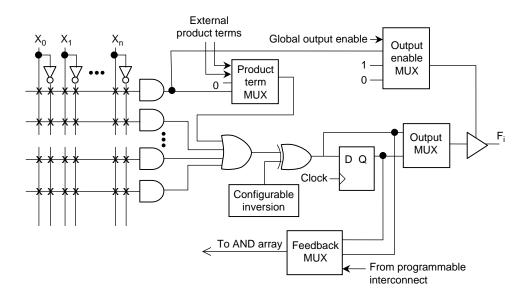

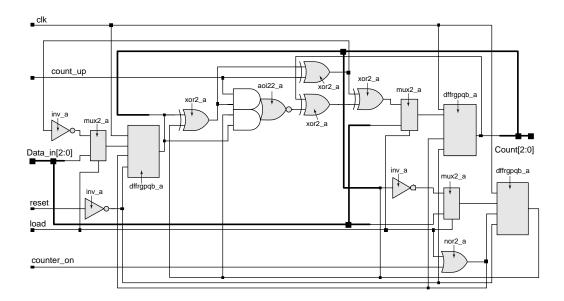

- 3.5 Arithmetic Logic Units Bill D. Carroll

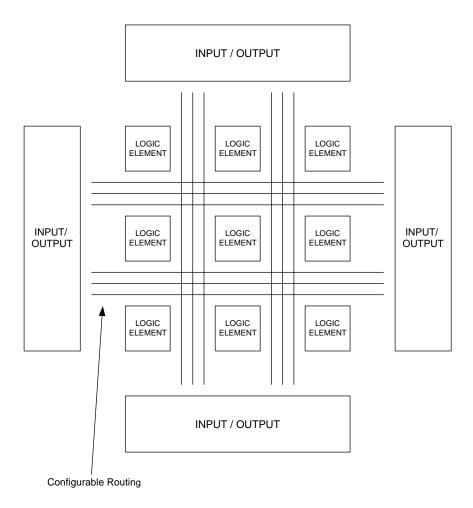

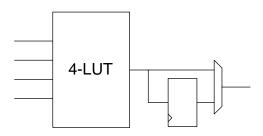

- 3.6 Programmable Logic Albert A. Liddicoat and Lynne A. Slivovsky

#### 4 Microprocessors

- 4.1 Practical Microprocessors John Staudhammer

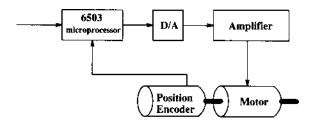

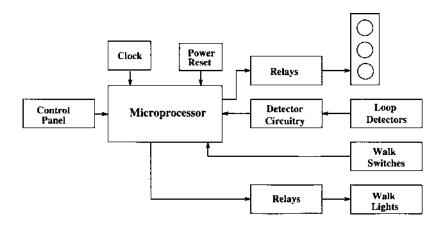

- 4.2 Applications Phillip J. Windley and James F. Frenzel

#### 5 Displays

- 5.1 Light-Emitting Diodes James E. Morris

- 5.2 Liquid-Crystal Displays James E. Morris

- 5.3 Plasma Displays Larry F. Weber

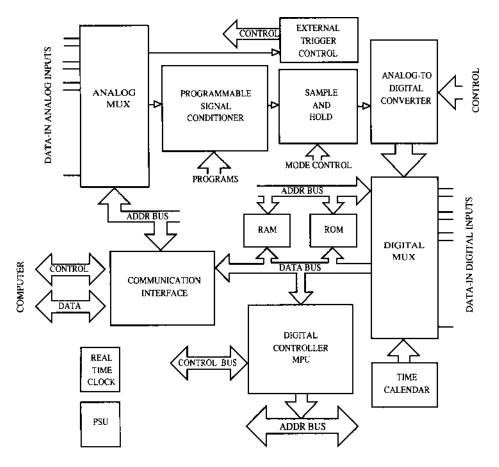

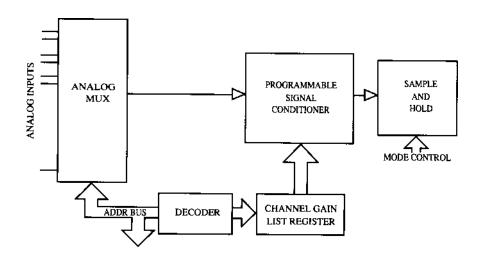

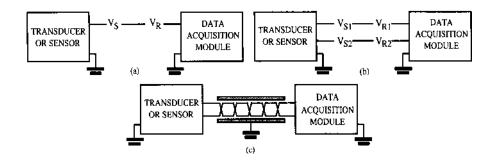

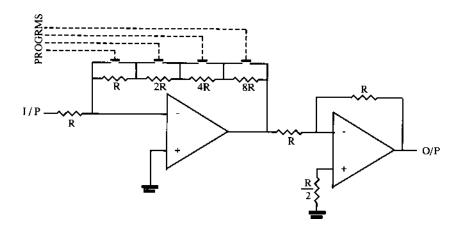

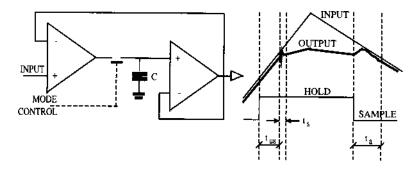

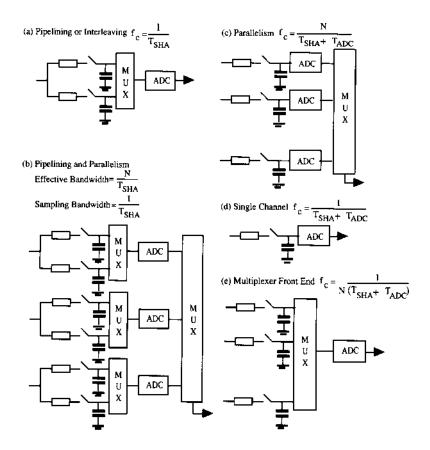

- 6 Data Acquisition Dhammika Kurumbalapitiya

#### 7 Testing

- 7.1 Digital IC Testing Michaela Serra

- 7.2 Design for Test Bulent I. Dervisoglu

- 8 Organization

- 8.1 Number Systems Richard F. Tinder

- 8.2 Computer Arithmetic S.N. Yanushkevich

- 8.3 Architecture Carl Hamacher, Zvonko Vranesic, and Safwat Zaky

- 8.4 Microprogramming Jacques Raymond

- 9 Programming

- 9.1 Assembly Language James M. Feldman and Edward W. Czeck

- 9.2 High-Level Languages Ted G. Lewis

- 9.3 Data Types and Data Structures Johannes J. Martin

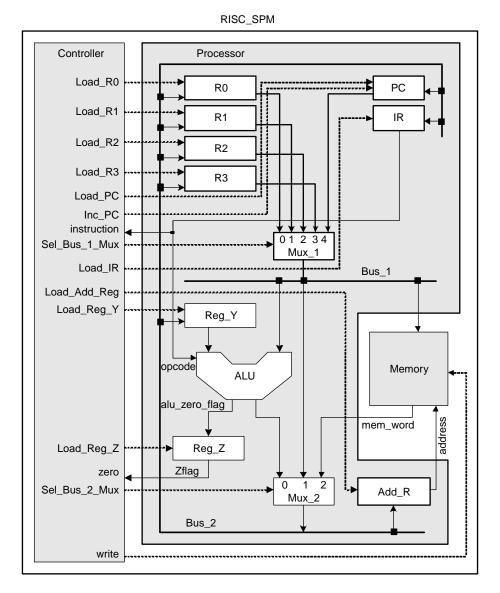

- 9.4 The Use of Hardware Description Languages in Computer Design Michael D. Ciletti

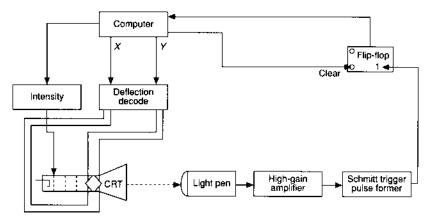

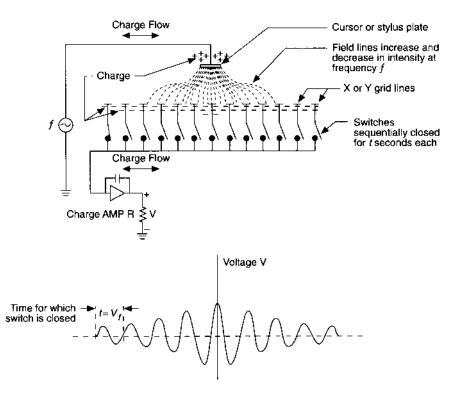

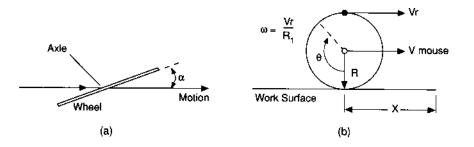

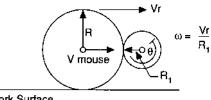

- 10 Input and Output Solomon Sherr

- 11 Secure Electronic Commerce Mostafa Hashem Sherif

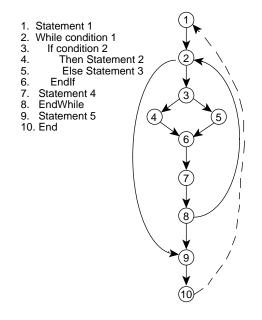

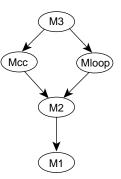

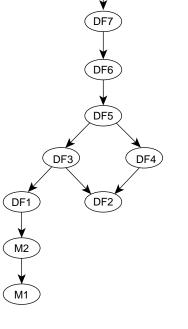

- 12 Software Engineering 12.1 Tools and Techniques Carl A. Argila 12.2 Software Testing Paul C. Jorgensen

- 13 Computer Graphics Nan C. Schaller and Evelyn P. Rozanski

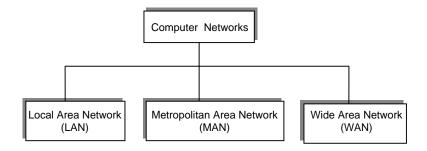

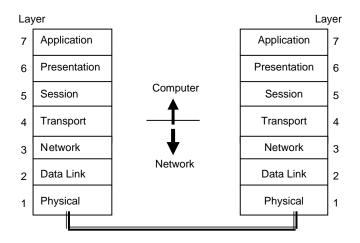

- 14 Computer Networks Matthew N.O. Sadiku and Cajetan M. Akujuobi

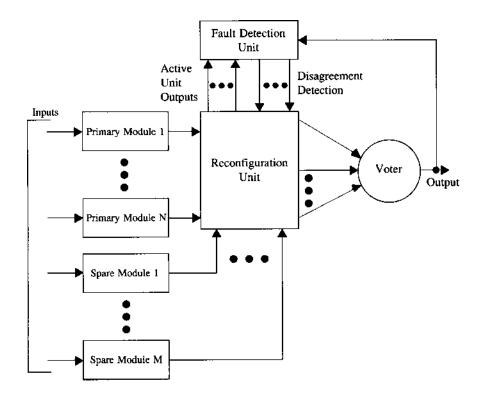

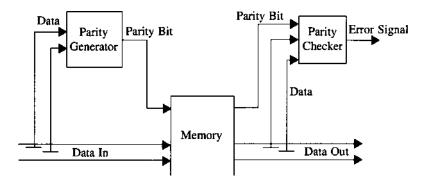

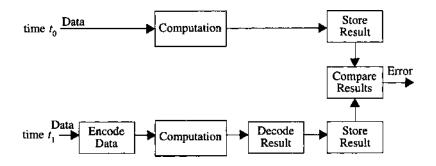

- 15 Fault Tolerance Barry W. Johnson

## Knowledge Engineering 16.1 Databases M. Abdelguerfi and R. Eskicioglu 16.2 Rule-Based Expert Systems Jay Liebowitz

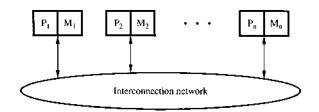

# Parallel Processors 17.1 Parallel Processors *Tse-yun Feng and Miro Kraetzl*17.2 Parallel Computing *Young Choon Lee and Albert Y. Zomaya*

- 18 Operating Systems Raphael Finkel

- 19 Computer and Communications Security J. Arlin Cooper and Anna M. Johnston

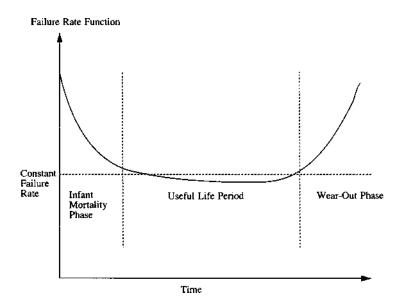

- 20 Computer Reliability Chris G. Guy

#### SECTION III Mathematics, Symbols, and Physical Constants

Introduction Ronald J. Tallarida

Greek Alphabet International System of Units (SI) Conversion Constants and Multipliers Physical Constants Symbols and Terminology for Physical and Chemical Quantities Credits Probability for Electrical and Computer Engineers *Charles W. Therrien*

#### Indexes

Author Index

Subject Index

# Ι

# Digital Devices

- 1 Logic Elements G.L. Moss, P. Graham, R.S. Sandige, L.A. Slivovsky, H.S. Hinton IC Logic Family Operation and Characteristics • Logic Gates (IC) • Bistable Devices • Optical Devices

- 2 Memory Devices W.D. Pricer, P.A. Lee, M. Mansuripur Integrated Circuits (RAM, ROM) • Magnetic Tape • Magneto-Optical Disk Data Storage

- Logical Devices F.P. Preparata, R.S. Sandige, A.A. Liddicoat, B.R. Bannister, D.G. Whitehead, J.M. Gilbert, G.A. Constantinides, B.D. Carroll, L.A. Slivovsky

Combinational Networks and Switching Algebra • Logic Circuits • Registers and Their Applications • Programmable Arrays • Arithmetic Logic Units • Programmable Logic

- **4 Microprocessors** J. Staudhammer, P.J. Windley, J.F. Frenzel Practical Microprocessors • Applications

- 5 Displays J.E. Morris, L.F. Weber Light-Emitting Diodes • Liquid-Crystal Displays • Plasma Displays

- 6 Data Acquisition D. Kurumbalapitiya

Introduction The Analog and Digital Signal Interface Analog Signal Conditioning •

Sample-and-Hold and A/D Techniques in Data Acquisition The Communication Interface of a

Data Acquisition System Data Recording Software Aspects

- 7 Testing M. Serra, B.I. Dervisoglu Digital IC Testing • Design for Test

# 1

### Logic Elements

| 1.1 | IC Logic Family Operation and Characteristics<br>IC Logic Families and Subfamilies • TTL Logic Family • CMOS<br>Logic Family • ECL Logic Family • Logic Family Circuit<br>Parameters • Interfacing between Logic Families |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2 | Logic Gates (IC)<br>Gate Specification Parameters • Bipolar Transistor Gates •<br>Complementary Metal-Oxide Semiconductor (CMOS) Logic •<br>CMOS Design Considerations • Choosing a Logic Family                          |

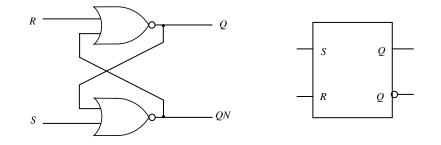

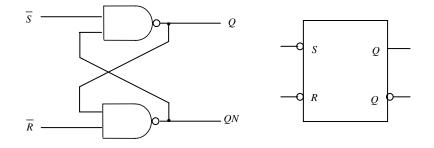

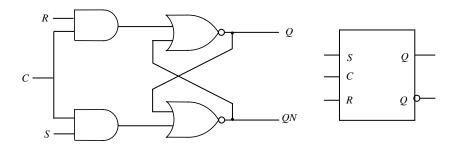

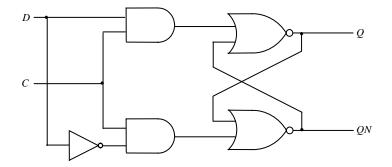

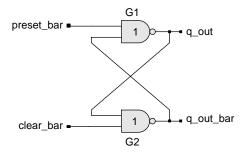

| 1.3 | Bistable Devices<br>Latches • Flip-Flops                                                                                                                                                                                  |

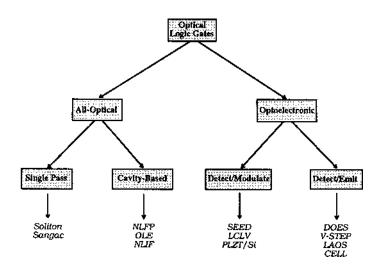

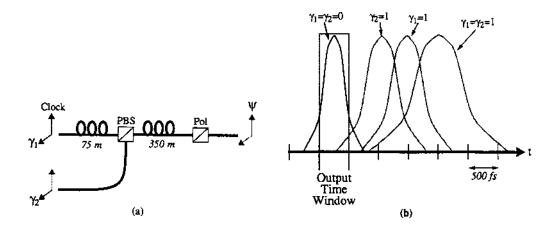

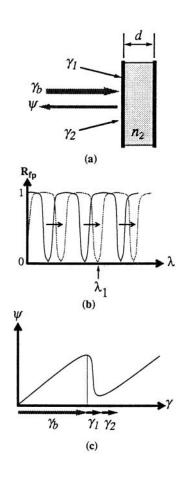

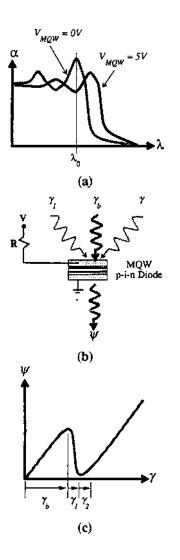

| 1.4 | Optical Devices<br>All-Optical Devices • Optoelectronic Devices                                                                                                                                                           |

|     |                                                                                                                                                                                                                           |

#### **1.1** IC Logic Family Operation and Characteristics

#### Gregory L. Moss

Gregory L. Moss Purdue University Peter Graham

University of Minnesota Richard S. Sandige California Polytechnic State

Lynne A. Slivovsky California Polytechnic State

University

University H.S. Hinton Utah State University

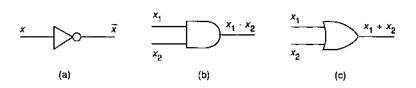

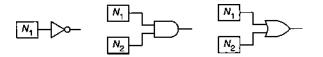

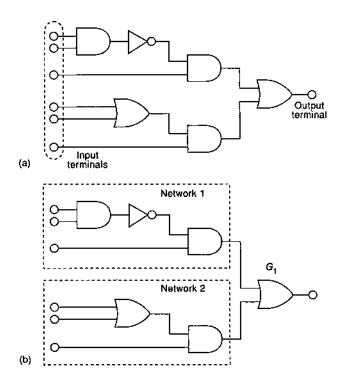

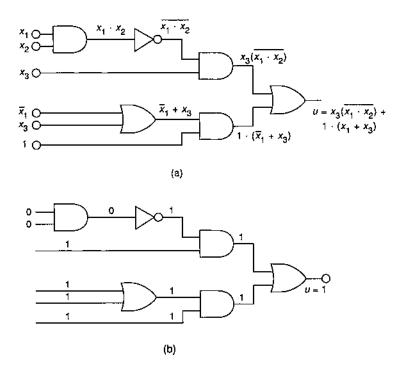

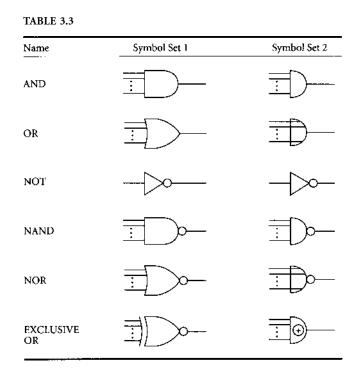

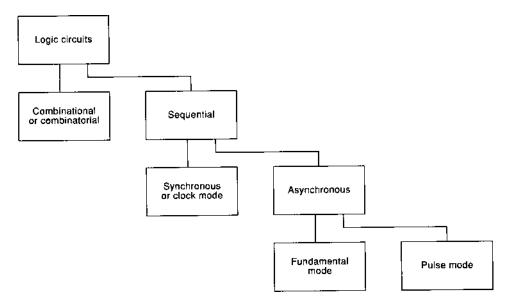

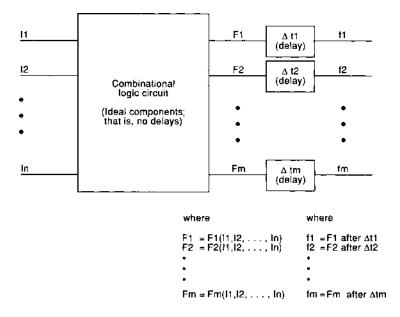

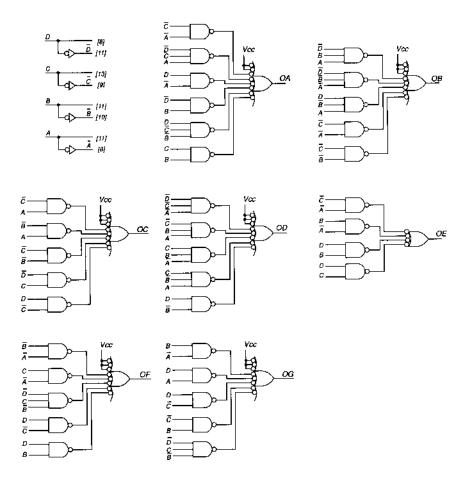

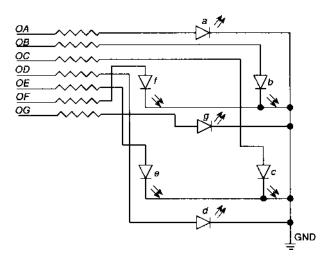

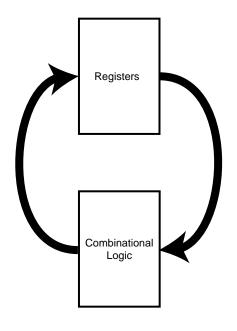

Digital logic circuits can be classified as belonging to one of two categories, either combinational (also called combinatorial) or sequential logic circuits. The output logic level of a combinational circuit depends only on the current logic levels at the circuit's inputs. Conversely, sequential logic circuits have a memory characteristic, making the sequential circuit's output dependent not only on current input conditions but also on the current output state of the circuit. The primary building block of combinational circuits is the logic gate. The three simplest logic gate functions are the inverter (or NOT), AND and OR. Other basic logic functions are derived from these three. See Table 1.1 for truth table definitions of the various types of logic gates. The memory elements used to construct sequential logic circuits are called latches and flip-flops.

The integrated circuit switching logic used in modern digital systems generally comes from one of three families: transistor-transistor logic (TTL), complementary metal oxide semiconductor logic (CMOS) or emitter coupled logic (ECL). Each logic family has its advantages and disadvantages. The three major families are divided into various subfamilies derived from performance improvements in IC design technology. Bipolar transistors provide switching action in both the TTL and ECL families, while enhancement-mode MOS transistors form the basis for the CMOS family. Recent improvements in switching-circuit performance are also attained using BiCMOS technology, the merging of bipolar and CMOS technologies on a single chip. A particular logic family is usually selected by digital designers based on criteria such as:

- 1. Switching speed

- 2. Power dissipation

- 3. PC board-area requirements (level of integration)

- 4. Output drive capability (fan-out)

- 5. Noise immunity characteristics

- 6. Product breadth

- 7. Sourcing of components

| 1-Input Function |        |     |      |     | 2-1 | input Functions |           |     |      |

|------------------|--------|-----|------|-----|-----|-----------------|-----------|-----|------|

| Input            | Output | Inp | outs |     |     | Output          | Functions |     |      |

| А                | NOT    | А   | В    | AND | OR  | NAND            | NOR       | XOR | XNOR |

| 0                | 1      | 0   | 0    | 0   | 0   | 1               | 1         | 0   | 1    |

| 1                | 0      | 0   | 1    | 0   | 1   | 1               | 0         | 1   | 0    |

|                  |        | 1   | 0    | 0   | 1   | 1               | 0         | 1   | 0    |

|                  |        | 1   | 1    | 1   | 1   | 0               | 0         | 0   | 1    |

TABLE 1.1 Defining Truth Tables for Logic Gates

#### **IC Logic Families and Subfamilies**

Integrated circuit logic families actually consist of several subfamilies of ICs that differ in performance characteristics. The TTL logic family has been the most widely used family type for applications employing small scale integration (SSI) or medium scale integration (MSI) integrated circuits. Lower power consumption and higher levels of integration are the principal advantages of the CMOS family. The ECL family is generally used in applications requiring high-speed switching logic. Today, the most common device-numbering system used in the TTL and CMOS families has a prefix of 54 (generally used in military applications and having an operating temperature range from -55 to  $125^{\circ}$ C) and 74 (generally used in industrial/commercial applications and having an operating temperature range from 0 to  $70^{\circ}$ C). Table 1.2 identifies various logic families and subfamilies.

#### **TTL Logic Family**

The TTL family has been the most widely used logic family for many years in applications employing SSI and MSI. It is moderately fast and offers a great variety of standard chips, but it is a mature technology that is generally no longer used in new circuit designs.

| Family (Subfamily) | Description                               |

|--------------------|-------------------------------------------|

| TTL                | Transistor-Transistor Logic               |

| 74xx               | Standard TTL                              |

| 74Lxx              | Low power TTL                             |

| 74Hxx              | High speed TTL                            |

| 74Sxx              | Schottky TTL                              |

| 74LSxx             | Low power Schottky TTL                    |

| 74Asxx             | Advanced Schottky TTL                     |

| 74ALSxx            | Advanced low power Schottky TTL           |

| 74Fxx              | Fast TTL                                  |

| CMOS               | Complementary Metal Oxide Semiconductor   |

| 4xxx               | Standard CMOS                             |

| 74Cxx              | Standard CMOS using TTL numbering system  |

| 74HCxx             | High speed CMOS                           |

| 74HCTxx            | High speed CMOS – TTL compatible          |

| 74FCTxx            | Fast CMOS – TTL compatible                |

| 74Acxx             | Advanced CMOS                             |

| 74ACTxx            | Advanced CMOS – TTL compatible            |

| 74AHCxx            | Advanced high speed CMOS                  |

| 74AHCTxx           | Advanced high speed CMOS - TTL compatible |

| ECL (or CML)       | Emitter Coupled (Current Mode) Logic      |

| 10xxx              | Standard ECL                              |

| 10Hxxx             | High speed ECL                            |

TABLE 1.2

Logic Families and Subfamilies

The active switching element used in all TTL family circuits is the NPN (not pointing in) bipolar junction transistor (BJT). The transistor is turned on when the base is approximately 0.7 volts more positive than the emitter and there is a sufficient flow of base current. The turned-on transistor (in non-Schottky subfamilies) is said to be in saturation and, ideally, acts like a closed switch between collector and emitter terminals. The transistor is turned off when the base is not biased with a high enough voltage with respect to the emitter. In this condition, the transistor acts like an open switch between the collector and emitter terminals.

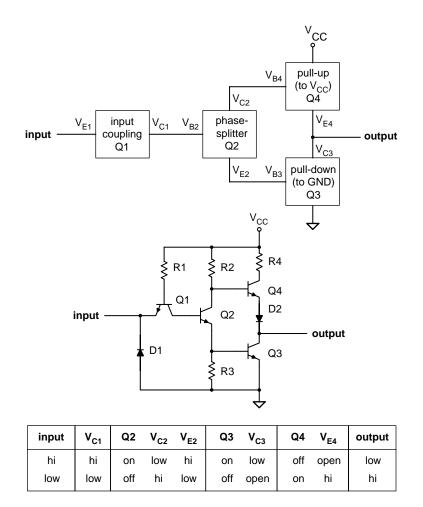

Figure 1.1 illustrates the transistor circuit blocks used in a standard TTL inverter. Four transistors are used to achieve the inverter function. The gate input connects to the emitter of transistor Q1, the input-coupling transistor. A clamping diode on the input prevents negative input-voltage spikes from damaging Q1. The collector voltage (and current) of Q1 controls Q2, the phase-splitter transistor. Q2 in turn controls the Q3 and Q4 transistors, forming the output circuit called a totem-pole arrangement. Q4 serves as a pull-up transistor, pulling the output high when it is turned on. Q3 does the opposite to the output, acting as a pull-down transistor. Q3 pulls the output low when it is turned on. Only one of the two transistors in the totem pole can be turned on at a time. This is the function of the phase-splitter transistor.

When a high-logic level is applied to the inverter's input, Q1's base-emitter junction will be reverse-biased and the base-collector junction will be forward-biased. This circuit condition will allow Q1 collector current to flow into the base of Q2, saturating Q2 and providing base current into Q3, and turning on Q3 as well.

FIGURE 1.1 TTL inverter circuit and operation.

The collector voltage of Q2 is too low to turn on Q4, so that it appears as an opening in the top part of the totem pole. A diode between the two totem-pole transistors provides an extra voltage drop, in series with the base-emitter junction of Q4, to ensure that Q4 will be turned off when Q2 is turned on. The saturated Q3 transistor brings the output near ground potential, producing a low-output result for a high input into the inverter.

When a low logic level is applied to the inverter's input, Q1's base-emitter junction will be forward-biased and the base-collector junction will be reverse-biased. This circuit condition will turn on Q1, shorting the collector terminal to the emitter and, therefore, to ground (low-level). This low voltage also acts on the base of Q2 and turns Q2 off. With Q2 off, insufficient base current flows into Q3, turning it off also. The Q2 leakage current is shunted to ground with a resistor to prevent the partial turning on of Q3. The collector voltage of Q2 is pulled to a high potential with another resistor and then turns on Q4, making it appear as a short in the top of the totem pole. The saturated Q4 transistor provides a low-resistance path from VCC to the output, producing high output for a low input into the inverter.

A TTL NAND gate is similar to the inverter circuit. The only exception is that the input-coupling transistor Q1 is constructed with multiple emitter-base junctions and each input to the NAND is connected to a separate emitter terminal. Any of the transistor's multiple emitters can turn on Q1. The TTL NAND gate thus functions in the same manner as the inverter, in that if any of the NAND gate inputs are low, the same circuit action will take place as with a low input to the inverter. Therefore, any time a low input is applied to the NAND gate, it will produce high output. Only if all the NAND gate inputs are simultaneously high, will it produce the same circuit action as the inverter, with its single input high and the resultant output low. Input coupling transistors with up to eight emitter-base junctions and, therefore, eight-input NAND gates are constructed.

Storage time (the time it takes for the transistor to come out of saturation) is a major factor of propagation delay for saturated BJT transistors. A long storage time limits switching speed of a standard TTL circuit. Propagation delay can be decreased and the switching speed increased by placing a Schottky diode between the base and collector of each transistor that might saturate. The resulting Schottky-clamped transistors then will not go into saturation, effectively eliminating storage time, since the diode shunts current from the base into the collector before the transistor can achieve saturation. Digital circuit designs implemented with TTL logic almost exclusively use one of the Schottky subfamilies to take advantage of a significant improvement in switching speed.

#### **CMOS Logic Family**

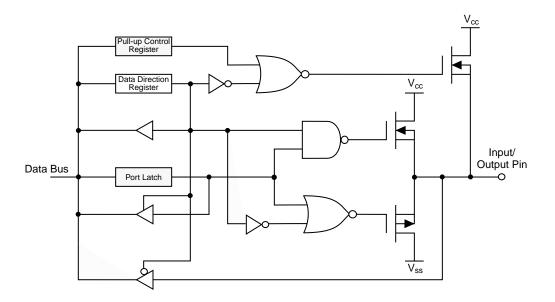

The vast majority of new circuit designs today utilize CMOS family devices. The active switching element in all CMOS family circuits is the metal-oxide semiconductor field-effect transistor (MOSFET). CMOS stands for complementary MOS transistors and refers to both types of MOSFET transistors, n-channel and p-channel, used to design this type of switching circuit. While the physical construction and internal physics of a MOSFET differ from the BJT, the circuit switching action of the two transistor types is quite similar. The MOSFET switch is essentially turned off and has a very high channel resistance by applying the same potential to the gate terminal as to the source. An n-channel MOSFET is turned on and has a very low channel resistance when a high voltage with respect to the source is applied to the gate. A p-channel MOSFET operates in the same fashion but with opposite polarities; the gate must be more negative than the source to turn on the transistor.

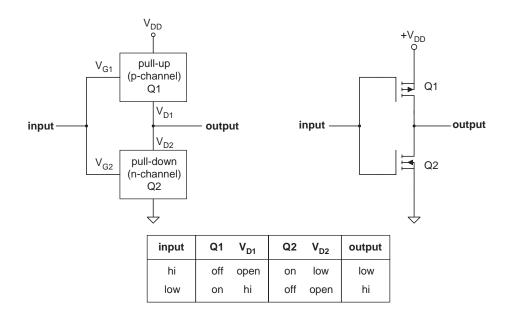

A block diagram and schematic for a CMOS inverter circuit is shown in Figure 1.2. Note that the circuit has a simpler and more compact design than that for the TTL inverter. That is a major reason why MOSFET integrated circuits have a higher circuit density than BJT integrated circuits and is one advantage that MOSFET ICs have over BJT ICs. As a result, CMOS is used in all levels of integration, from SSI through Very Large Scale Integration (VLSI).

When a high logic level is applied to the inverter's input, the p-channel MOSFET Q1 will be turned off and the n-channel MOSFET Q2 will be turned on. This causes the output to be shorted to ground through the low-resistance path of Q2's channel. The turned-off Q1 has a very high channel resistance and acts almost like an open channel.

FIGURE 1.2 CMOS inverter circuit and operation.

FIGURE 1.3 CMOS two-input NAND circuit and operation.

When a low logic level is applied to the inverter's input, the p-channel MOSFET Q1 will be turned on and the n-channel MOSFET Q2 will be turned off. This causes the output to be shorted to VDD through the low-resistance path of Q1's channel. The turned-off Q2 has a very high channel resistance and acts almost like an open channel.

CMOS NAND gates are constructed by paralleling p-channel MOSFETs, one for each input, and putting in series an n-channel MOSFET for each input, as shown in the block diagram and schematic of Figure 1.3.

The NAND gate will produce a low output only when both Q3 and Q4 are turned on, creating a low-resistance path from the output to ground through the two series channels. This can be achieved by having a high input on both A and B. This input condition will also turn off Q1 and Q2. If either input A or input B or both are low, the respective parallel MOSFET will be turned on, providing a low resistance path for the output to VDD. This will also turn off at least one of the series MOSFETs, resulting in a high resistance path for the output to ground.

#### **ECL Logic Family**

ECL is the highest-speed logic family available. While it does not offer as large a variety of IC chips as are available in the TTL or CMOS families, it has been popular for logic applications requiring high-speed switching, although its power consumption is also relatively high. ECL power consumption, however, does not increase as the switching frequency increases. At frequencies above 20 MHz, the dynamic power consumption of CMOS gates will continue to increase and exceed the per-gate consumption of ECL devices. Newer ECL family devices are available that can be switched at a rate faster than 3GHz.

The active switching element used in ECL family circuits is also the NPN BJT. But unlike the TTL family, which switches the transistors into saturation while turning them on, ECL switching is designed to prevent driving the transistors into saturation. Whenever bipolar transistors are driven into saturation, their switching speed will be limited by the charge-carrier storage delay, a transistor operational characteristic. Thus, the switching speed of ECL circuits will be significantly higher than that for TTL circuits. ECL operation is based on switching a fixed amount of bias current, which is less than the saturation amount between two different transistors. The basic circuit found in the ECL family is the differential amplifier. A bias circuit controls one side of the differential amplifier, while the other is controlled by the logic inputs to the gate. This logic family is also referred to as current-mode logic (CML), due to its current switching operation.

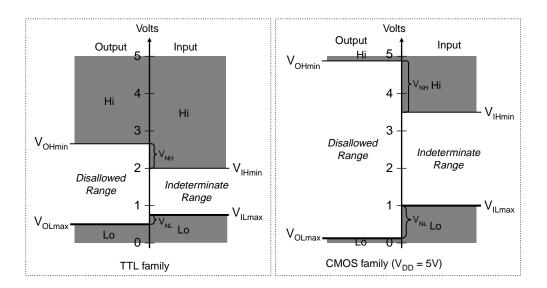

#### Logic Family Circuit Parameters

Digital circuits and systems operate in only two states, logic 1 and 0, usually represented by two different voltage levels, a HIGH and a LOW. The two logic levels consist of a range of values with numerical quantities dependent upon the specific family used. Minimum high-logic levels and maximum low-logic levels are established by specifications for each family. Minimum device output levels for a logic high are called  $V_{OH(min)}$ , and minimum input levels are called  $V_{IH(min)}$ . The abbreviations for maximum output and input

FIGURE 1.4 TTL and CMOS family logic levels.

| Subfamily | V <sub>OH(min)</sub> | V <sub>OL(max)</sub> | V <sub>IH(min)</sub> | V <sub>IL(max)</sub> |  |

|-----------|----------------------|----------------------|----------------------|----------------------|--|

| 74xx      | 2.4                  | 0.4                  | 2.0                  | 0.8                  |  |

| 74LSxx    | 2.7                  | 0.5                  | 2.0                  | 0.8                  |  |

| 74ASxx    | 2.5                  | 0.5                  | 2.0                  | 0.8                  |  |

| 74ALSxx   | 2.5                  | 0.4                  | 2.0                  | 0.8                  |  |

| 74Fxx     | 2.5                  | 0.5                  | 2.0                  | 0.8                  |  |

| 74HCxx    | 4.9                  | 0.1                  | 3.15                 | 0.9                  |  |

| 74HCTxx   | 4.9                  | 0.1                  | 2.0                  | 0.8                  |  |

| 74ACxx    | 3.8                  | 0.4                  | 3.15                 | 1.35                 |  |

| 74ACTxx   | 3.8                  | 0.4                  | 2.0                  | 0.8                  |  |

| 74AHCxx   | 4.5                  | 0.1                  | 3.85                 | 1.65                 |  |

| 74AHCTxx  | 3.65                 | 0.1                  | 2.0                  | 0.8                  |  |

| 10xxx     | -0.96                | -1.65                | -1.105               | -1.475               |  |

| 10Hxxx    | -0.98                | -1.63                | -1.13                | -1.48                |  |

TABLE 1.3 Logic Signal Voltage Parameters for Selected Logic Subfamilies (in Volts)

low-logic levels are  $V_{OL(max)}$  and  $V_{IL(max)}$ . Figure 1.4 shows the relationships between these parameters. Logic voltage-level parameters for selected prominent logic subfamilies are illustrated in Table 1.3. As seen in this illustration, there are many operational incompatibilities between major logic family types.

Noise margin is a quantitative measure of a device's **noise immunity**. High-level noise margin  $(V_{\rm NH})$  and low-level noise margin  $(V_{\rm NL})$  are defined in Equation (1.1) and Equation (1.2).

$$V_{\rm NH} = V_{\rm OH(min)} - V_{\rm IH(min)} \tag{1.1}$$

$$V_{\rm NL} = V_{\rm IL(max)} - V_{\rm OL(max)} \tag{1.2}$$

Using the logic voltage values in Table 1.3 for the selected subfamilies reveals that the highest noise immunity is obtained with logic devices in the CMOS family while the lowest noise immunity is endemic to the ECL family.

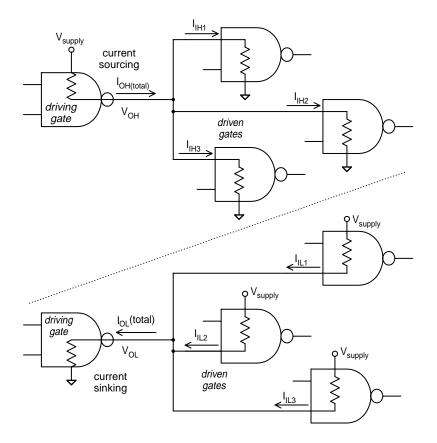

Switching circuit outputs are loaded by the inputs of the devices they are driving, as illustrated in Figure 1.5. Worst-case input loading current levels and output driving current capabilities are listed in Table 1.4 for various logic subfamilies. The **fan-out** of a driving device is the ratio between its output current capabilities at each logic level and the corresponding gate-input current loading value.

Switching circuits based on bipolar transistors have fan-out that is limited primarily by the current-sinking and current-sourcing capabilities of the driving device.

CMOS switching circuits are limited by the charging and discharging times associated with the output resistance of the driving gate and the input capacitance of the load gates. Thus, CMOS fan-out depends on switching frequency. With fewer capacitive loading inputs to drive, the maximum switching frequency of CMOS devices will increase.

The switching speed of logic devices depends on the device's **propagation delay time**. The propagation delay of a logic device limits the frequency at which it can be operated. There are two propagation delay times specified for logic gates:  $t_{PHL}$ , delay time for the output to change from high to low, and  $t_{PLH}$ , delay time for the output to change from low to high. Average typical propagation delay times for a single gate are listed in Table 1.5 for several logic subfamilies. The ECL family has the fastest switching speed.

The amount of power required by an IC is normally specified in terms of the amount of current  $I_{CC}$  (TTL family),  $I_{DD}$  (CMOS family) or  $I_{EE}$  (ECL family) drawn from the power supply. For complex IC devices, the required supply current is given under specified test conditions. For TTL chips containing simple gates, the average power dissipation  $P_{D(ave)}$  is normally calculated from two measurements,  $I_{CCH}$  (when all gate outputs are high) and  $I_{CCL}$  (when all gate outputs are low). Table 1.5 compares the static power dissipation of several logic subfamilies. The ECL family has the highest power dissipation for switching frequencies below about

FIGURE 1.5 Current loading of driving gates.

| Subfamily | I <sub>OH(max)</sub> | I <sub>OL(max)</sub> | I <sub>IH(max)</sub> | I <sub>IL(max)</sub> |  |

|-----------|----------------------|----------------------|----------------------|----------------------|--|

| 74xx      | -400 μA              | 16 mA                | 40 µA                | -1.6 mA              |  |

| 74LSxx    | -400 μA              | 8 mA                 | 20 µA                | $-400 \ \mu A$       |  |

| 74ASxx    | -2 mA                | 20 mA                | 20 µA                | -0.5 mA              |  |

| 74ALSxx   | -400 μA              | 8 mA                 | 20 µA                | $-100 \ \mu A$       |  |

| 74Fxx     | -1 mA                | 20 mA                | 20 µA                | -0.6 mA              |  |

| 74HCxx    | -4 mA                | 4 mA                 | 1 μA                 | $-1 \mu A$           |  |

| 74HCTxx   | -4 mA                | 4 mA                 | 1 μA                 | $-1 \mu A$           |  |

| 74ACxx    | -24 mA               | 24 mA                | 1 μA                 | $-1 \mu A$           |  |

| 74ACTxx   | -24 mA               | 24 mA                | 1 μA                 | $-1 \mu A$           |  |

| 74AHCxx   | -8 mA                | 8 mA                 | 1 μA                 | $-1 \mu A$           |  |

| 74AHCTxx  | -8 mA                | 8 mA                 | 1 μA                 | $-1 \mu A$           |  |

| 10xxx     | 50 mA                | -50 mA               | -265 μA              | 0.5 μA               |  |

| 10Hxxx    | 50 mA                | -50 mA               | -265 μA              | 0.5 μA               |  |

TABLE 1.4 Worst Case Current Parameters for Selected Logic Subfamilies

20 MHz, while the lowest dissipation is found in the CMOS family. Power dissipation for the CMOS family is directly proportional to gate-input signal frequency. For example, typically, the power dissipation for a CMOS logic circuit will increase by a factor of 100 if input signal frequency is increased from 1 kHz to 100 kHz.

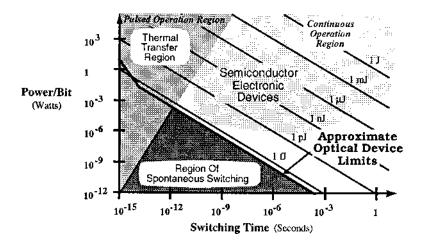

It is desirable to implement high speed (and, therefore, low propagation delay time) switching devices that consume low amounts of power. Because of the nature of transistor switching circuits, it is difficult to attain

| Subfamily | Propagation Delay<br>Time, ns (ave.) | Static Power Dissipation,<br>mW (per gate) |

|-----------|--------------------------------------|--------------------------------------------|

| 74xx      | 10                                   | 10                                         |

| 74LSxx    | 9.5                                  | 2                                          |

| 74Asxx    | 1.5                                  | 8.5                                        |

| 74ALSxx   | 4                                    | 1.2                                        |

| 74Fxx     | 3                                    | 6                                          |

| 74HCxx    | 8                                    | 0.003                                      |

| 74HCTxx   | 14                                   | 0.003                                      |

| 74Acxx    | 5                                    | 0.010                                      |

| 74ACTxx   | 5                                    | 0.010                                      |

| 74AHCxx   | 5.5                                  | 0.003                                      |

| 74AHCTxx  | 5                                    | 0.003                                      |

| 10xxx     | 2                                    | 25                                         |

| 10Hxxx    | 1                                    | 25                                         |

**TABLE 1.5** Speed-Power Comparison for a Single Gate in

Selected Logic Subfamilies

FIGURE 1.6 Circuit interfacing requirements.

high-speed switching with low power dissipation. The continued development of new IC logic families and subfamilies is due largely to the trade-offs between these two device-switching parameters.

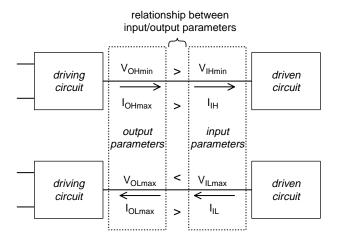

#### **Interfacing between Logic Families**

The interconnection of logic chips requires that input and output specifications be satisfied. Figure 1.6 illustrates voltage and current requirements. The driving chip's  $V_{OHmin}$  must be greater than the driven circuit's  $V_{IHmin}$ , and the driver's  $V_{OLmax}$  must be less than  $V_{ILmax}$  for the loading circuit. Voltage level shifters must be used to interface the circuits if these voltage requirements are not met. Of course, a driving circuit's output must not exceed the maximum- and minimum-allowable input voltages for the driven circuit. The current sinking and sourcing ability of the driver circuit's output must be greater than the total current requirements for the loading circuit. Buffer gates or stages must be used if current requirements are not satisfied. All chips within a single logic family are designed to be compatible with other chips in that family. Mixing chips from multiple subfamilies together within a single digital circuit can have adverse effects on the overall circuit's switching speed and noise immunity.

#### **Defining Terms**

- **Fan-out:** The specification used to identify the limit to the number of loading inputs that can be reliably driven by a driving device's output.

- Logic Level: The high or low value of a voltage variable, assigned as a 1 or a 0 state.

- **Noise Immunity:** A logic device's ability to tolerate input voltage fluctuation caused by noise without changing its output state.

- **Propagation Delay Time:** The time delay from when the input logic level to a device is changed until that device produces the resultant output change.

- **Truth Table:** A listing of the relationship of a circuit's output produced for various combinations of logic levels at the inputs.

#### References

- N.P. Cook, Practical Digital Electronics, Upper Saddle River, NJ: Pearson Prentice-Hall, 2004.

- R.K. Dueck, *Digital Design with CPLD Applications and VHDL*, 2nd ed., Albany, NY: Delmar Thomson Learning, 2005.

- T.L. Floyd, Digital Fundamentals, 8th ed., Upper Saddle River, NJ: Pearson Prentice-Hall, 2003.

- D.D. Givone, Digital Principles and Design, New York, NY: McGraw-Hill, 2003.

- W. Kleitz, *Digital Electronics: A Practical Approach*, 7th ed., Upper Saddle River, NJ: Pearson Prentice-Hall, 2005.

- M.M. Mano, Digital Design, 3rd ed., Upper Saddle River, NJ: Pearson Prentice-Hall, 2002.

- R.J. Tocci, N.S. Widmer, and G.L. Moss, *Digital Systems: Principles and Applications*, 9th ed., Upper Saddle River, NJ: Pearson Prentice-Hall, 2004.

- J.F. Wakerly, *Digital Design: Principles and Practices*, 3rd ed., Upper Saddle River, NJ: Pearson Prentice-Hall, 2001.

#### **Further Information**

Journals & Trade Magazines:

EDN, Highlands Ranch, CO: Reed Business Information. Electronic Design, Cleveland, OH: Penton Media. Electronic Engineering Times, Manhasset, NY: CMP Publications.

Internet Addresses for Digital Device Data Sheets:

Texas Instruments, Inc.: <a href="http://focus.ti.com/general/docs/scproducts.jsp">http://focus.ti.com/general/docs/scproducts.jsp</a>.

ON Semiconductor: <a href="http://www.onsemi.com/site/products/taxonomy/">http://www.onsemi.com/site/products/taxonomy/</a>>.

#### 1.2 Logic Gates (IC)<sup>1</sup>

#### Peter Graham

This section introduces and analyzes the electronic circuit realizations of the basic gates of the three technologies: transistor-transistor logic (TTL), emitter-coupled logic (ECL), and complementary metal-oxide semiconductor (CMOS) logic. These circuits are commercially available on small-scale integration chips and are also the building blocks for more elaborate logic systems. The three technologies are compared with regard to speed, power consumption, and noise immunity, and parameters are defined which facilitate these comparisons. Also included are recommendations which are useful in choosing and using these technologies.

<sup>&</sup>lt;sup>1</sup>Based on P. Graham, "Gates," in *Handbook of Modern Electronics and Electrical Engineering*, C. Belove, Ed., New York: Wiley-Interscience, 1986, pp. 864–876. With permission.

#### **Gate Specification Parameters**

Theoretically almost any logic device or system could be constructed by wiring together the appropriate configuration of the basic gates of the selected technology. In practice, however, the gates are interconnected during the fabrication process to produce a desired system on a single chip. The circuit complexity of a given chip is described by one of the following four rather broad classifications:

- **Small-Scale Integration (SSI).** The inputs and outputs of every gate are available for external connection at the chip pins (with the exception that exclusive OR and AND-OR gates are considered SSI).

- Medium-Scale Integration (MSI). Several gates are interconnected to perform somewhat more elaborate logic functions such as flip-flops, counters, multiplexers, etc.

- Large-Scale Integration (LSI). Several of the more elaborate circuits associated with MSI are interconnected within the integrated circuit to form a logic system on a single chip. Chips such as calculators, digital clocks, and small microprocessors are examples of LSI.

- Very-Large-Scale Integration (VLSI). This designation is usually reserved for chips having a very high density, 1000 or more gates per chip. These include the large single-chip memories, gate arrays, and microcomputers.

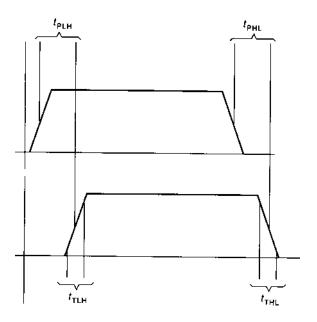

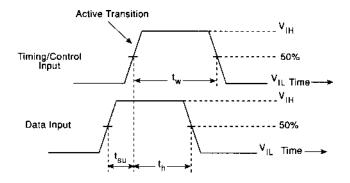

Specifications of logic speed require definitions of switching times. These definitions can be found in the introductory pages of most data manuals. Four of them pertain directly to gate circuits. These are (see also Figure 1.7):

- LOW-to-HIGH Propagation Delay Time ( $t_{PLH}$ ). The time between specified reference points on the input and output voltage waveforms when the output is changing from low to high.

- HIGH-to-LOW Propagation Delay Tune ( $t_{PHL}$ ). The time between specified reference points on the input and output voltage waveforms when the output is changing from high to low.

- **Propagation Delay Time** ( $t_{PD}$ ). The average of the two propagation delay times:  $t_{PD} = (t_{PD} + t_{PHL})/2$ .

- LOW-to-HIGH Transition Time ( $t_{TLH}$ ). The rise time between specified reference points on the LOW-to-HIGH shift of the output waveform.

FIGURE 1.7 Definitions of switching times. (Source: P. Graham, "Gates," in Handbook of Modern Electronics and Electrical Engineering, C. Belove, Ed., New York: Wiley-Interscience, 1986, p. 865. With permission.)

• HIGH-to-LOW Transition Time ( $t_{THL}$ ). The fall time between specified reference points on the HIGH-to-LOW shift of the output waveform. The reference points usually are 10 and 90% of the voltage level difference in each case.

Power consumption, driving capability, and effective loading of gates are defined in terms of currents.

- Supply Current, Outputs High  $(I_{xxH})$ . The current delivered to the chip by the power supply when all outputs are open and at the logical 1 level. The xx subscript depends on the technology.

- Supply Current, Outputs Low ( $I_{xxL}$ ). The current delivered to the chip by the supply when all outputs are open and at the logical 0 level.

- Supply Current, Worst Case  $(I_{xx})$ . When the output level is unspecified, the input conditions are assumed to correspond to maximum supply current.

- Input HIGH Current (I<sub>IH</sub>). The current flowing into an input when the specified HIGH voltage is applied.

- Input LOW Current (IIL). The current flowing into an input when the specified LOW voltage is applied.

- Output HIGH Current ( $I_{OH}$ ). The current flowing into the output when it is in the HIGH state.  $I_{OHmax}$  is the largest  $I_{OH}$  for which  $V_{OH} \ge V_{OHmin}$  is guaranteed.

- Output LOW Current ( $I_{OL}$ ). The current flowing into the output when it is in the LOW state.  $I_{OLmax}$  is the largest  $I_{OL}$  for which  $V_{OL} \ge V_{OLmax}$  is guaranteed.

The most important voltage definitions are concerned with establishing ranges on the logical 1 (HIGH) and logical 0 (LOW) voltage levels.

- Minimum High-Level Input Voltage ( $V_{IHmin}$ ). The least positive value of input voltage guaranteed to result in the output voltage level specified for a logical 1 input.

- Maximum Low-Level Input Voltage ( $V_{ILmax}$ ). The most positive value of input voltage guaranteed to result in the output voltage level specified for a logical 0 input.

- Minimum High-Level Output Voltage ( $V_{OHmin}$ ). The guaranteed least positive output voltage when the input is properly driven to produce a logical 1 at the output.

- Maximum Low-Level Output Voltage ( $V_{OLmax}$ ). The guaranteed most positive output voltage when the input is properly driven to produce a logical 0 at the output.

- Noise Margins.  $NM_H = V_{OHmin} V_{IHmin}$  is how much larger the guaranteed least positive output logical 1 level is than the least positive input level that will be interpreted as a logical 1. It represents how large a negative-going glitch on an input 1 can be before it affects the output of the driven device. Similarly,  $NM_L = V_{ILmax} V_{OLmax}$  is the amplitude of the largest positive-going glitch on an input 0 that will not affect the output of the driven device.

Finally, three important definitions are associated with specifying the load that can be driven by a gate. Since in most cases the load on a gate output will be the sum of inputs of other gates, the first definition characterizes the relative current requirements of gate inputs.

- Load Factor (LF). Each logic family has a reference gate, each of whose inputs is defined to be a unit load in both the HIGH and the LOW conditions. The respective ratios of the input currents  $I_{IH}$  and  $I_{IL}$  of a given input to the corresponding  $I_{IH}$  and  $I_{IL}$  of the reference gate define the HIGH and LOW load factors of that input.

- Drive Factor (DF). A device output has drive factors for both the HIGH and the LOW output conditions. These factors are defined as the respective ratios of  $I_{OHmax}$  and  $I_{OLmax}$  of the gate to  $I_{OHmax}$  and  $I_{OLmax}$  of the reference gate.

- **Fan-Out.** For a given gate the fan-out is defined as the maximum number of inputs of the same type of gate that can be properly driven by that gate output. When gates of different load and drive factors are interconnected, fan-out must be adjusted accordingly.

#### **Bipolar Transistor Gates**

A logic circuit using bipolar junction transistors (BJTs) can be classified either as saturated or as nonsaturated logic. A saturated logic circuit contains at least one BJT that is saturated in one of the stable modes of the circuit.

In nonsaturated logic circuits none of the transistors is allowed to saturate. Since bringing a BJT out of saturation requires a few additional nanoseconds (called the storage time), nonsaturated logic is faster. The fastest circuits available at this time are emitter-coupled logic (ECL), with transistor-transistor logic (TTL) having Schottky diodes connected to prevent the transistors from saturating (Schottky TTL) being a fairly close second. Both of these families are nonsaturated logic. All TTL families other than Schottky are saturated logic.

#### **Transistor-Transistor Logic**

TTL evolved from resistor-transistor logic (RTL) through the intermediate step of diode-transistor logic (DTL). All three families are catalogued in data books published in 1968, but of the three only TTL is still available.

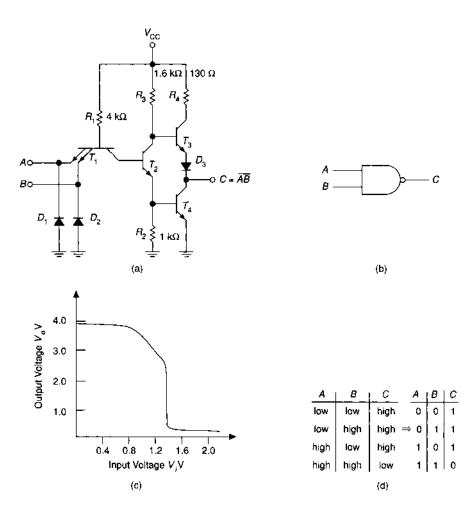

The basic circuit of the standard TTL family is typified by the two-input NAND gate shown in Figure 1.8(a). To estimate the operating levels of voltage and current in this circuit, assume that any transistor in saturation has  $V_{CE} = 0.2$  and  $V_{BE} = 0.75$  V. Let drops across conducting diodes also be 0.75 V and transistor current gains (when nonsaturated) be about 50. As a starting point, let the voltage levels at both inputs A and B be high enough that  $T_1$  operates in the reversed mode. In this case the emitter currents of  $T_1$  are negligible, and

**FIGURE 1.8** Two-input transistor-transistor logic (TTL) NAND gate type 7400: (a) circuit, (b) symbol, (c) voltage transfer characteristic ( $V_i$  to both inputs), (d) truth table. (*Source:* P. Graham, "Gates," in *Handbook of Modern Electronics and Electrical Engineering*, C. Belove, Ed., New York: Wiley-Interscience, 1986, p. 867. With permission.)

the current into the base of  $T_1$  goes out the collector to become the base current of  $T_2$ . This current is readily calculated by observing that the base of  $T_1$  is at  $3 \times 0.75 = 2.25$  V so there is a 2.75-V drop across the 4-k $\Omega$ resistor. Thus  $I_{BI} = I_{B2} = 0.7$  mA, and it follows that  $T_2$  is saturated. With  $T_2$  saturated, the base of  $T_3$  is at  $V_C + V_{BE4} = 0.95$  V. If  $T_4$  is also saturated, the emitter of  $T_3$  will be at  $V_{D3} + V_{CE4} = 0.95$  V, and  $T_3$  will be cut off. The voltage across the 1.6-k $\Omega$  resistor is 5 - 0.95 = 4.05 V, so the collector current of  $T_2$  is about 2.5 mA. This means the emitter current of  $T_2$  is 3.2 mA. Of this, 0.75 mA goes through the 1-k $\Omega$  resistor, leaving 2.45 mA as the base current of  $T_4$ . Since the current gain of  $T_4$  is about 50, it will be well into saturation for any collector current less than 100 mA, and the output at C is a logic 0. The corresponding minimum voltage levels required at the inputs are estimated from  $V_{BE4} + V_{ECI}$ , or about 1.7 V.

Now let either or both of the inputs be dropped to 0.2 V.  $T_1$  is then biased to saturation in the normal mode, so the collector current of  $T_1$  extracts the charge from the base region of  $T_2$ . With  $T_2$  cut off, the base of  $T_4$  is at 0 V and  $T_4$  is cut off.  $T_3$  will be biased by the current through the 1.6-k $\Omega$  resistor ( $R_3$ ) to a degree regulated by the current demand at the output C. The drop across  $R_3$  is quite small for light loads, so the output level at C will be  $V_{\rm CC} - V_{\rm BE3} - V_{\rm D3}$ , which will be about 3.5 V corresponding to the logical 1.

The operation is summarized in the truth table in Figure 1.8(d), identifying the circuit as a two-input NAND gate. The derivation of the input-output voltage transfer characteristic [Figure 1.8(c)], where  $V_i$  is applied to inputs *A* and *B* simultaneously, can be found in most digital circuit textbooks. The sloping portion of the characteristic between  $V_i = 0.55$  and 1.2 V corresponds to  $T_2$  passing through the active region in going from cutoff to saturation.

Diodes  $D_1$  and  $D_2$  are present to damp out "ringing" that can occur, for example, when fast voltage level shifts are propagated down an appreciable length (20 cm or more) of microstripline formed by printed circuit board interconnections. Negative overshoots are clamped to the 0.7 V across the diode.

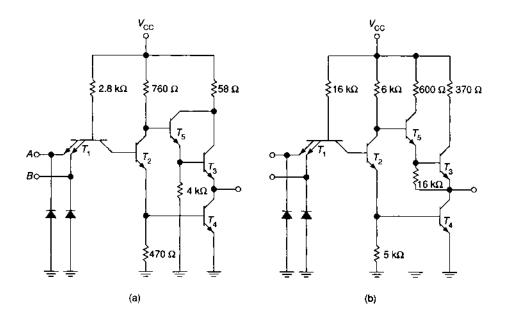

The series combination of the 130- $\Omega$  resistor,  $T_3$ ,  $D_3$ , and  $T_4$  in the circuit of Figure 1.8(a), forming what is called the totem-pole output circuit, provides a low impedance drive in both the source (output C = 1) and sink (output C = 0) modes and contributes significantly to the relatively high speed of TTL. The available source and sink currents, which are well above the normal requirements for steady state, come into play during the charging and discharging of capacitive loads. Ideally  $T_3$  should have a very large current gain and the 130- $\Omega$  resistor should be reduced to 0. The latter, however, would cause a short-circuit load current which would overheat  $T_3$ , since  $T_3$  would be unable to saturate. All TTL families other than the standard shown in Figure 1.8(a) use some form of Darlington connection for  $T_3$ , providing increased current gain and eliminating the need for diode  $D_3$ . The drop across  $D_3$  is replaced by the base emitter voltage of the added transistor  $T_5$ . This connection appears in Figure 1.9(a), an example of the 74Hxx series of TTL gates that increases speed at the expense of increased power consumption, and in Figure 1.9(b), a gate from the 74Lxx series that sacrifices speed to lower power dissipation.

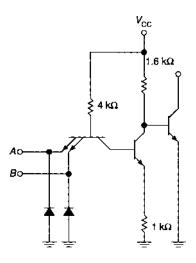

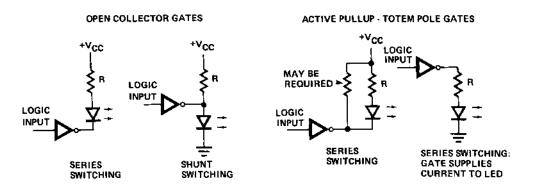

A number of TTL logic function implementations are available with open collector outputs. For example, the 7403 two-input NAND gate shown in Figure 1.10 is the open collector version of Figure 1.8(a). The open collector output has some useful applications. The current in an external load connected between the open collector and  $V_{CC}$  can be switched on and off in response to the input combinations. This load, for example, might be a relay, an indicator light, or an LED display. Also, two or more open collector gates can share a common load, resulting in the anding together of the individual gate functions. This is called a "wired-AND connection." In any application, there must be some form of load or the device will not function. There is a lower limit to the resistance of this load which is determined by the current rating of the open collector transistor. For wired-AND applications the resistance range depends on how many outputs are being wired and on the load being driven by the wired outputs. Formulas are given in the data books. Since the open collector configuration does not have the speed enhancement associated with an active pull-up, the low to high propagation delay ( $t_{PLH}$ ) is about double that of the totem-pole output. It should be observed that totem-pole outputs should not be wired, since excessive currents in the active pull-up circuit could result.

**Nonsaturated TTL.** Two TTL families, the Schottky (74Sxx) and the low-power Schottky (74LSxx), can be classified as nonsaturating logic. The transistors in these circuits are kept out of saturation by the connection of Schottky diodes, with the anode to the base and the cathode to the collector.

FIGURE 1.9 Modified transistor-transistor logic (TTL) two-input NAND states: (a) type 74Hxx, (b) type 74L00. (*Source:* P. Graham, "Gates," in *Handbook of Modern Electronics and Electrical Engineering*, C. Belove, Ed., New York: Wiley-Interscience, 1986, p. 868. With permission.)

FIGURE 1.10 Open collector two-input NAND gate. (*Source:* P. Graham, "Gates," in *Handbook of Modern Electronics and Electrical Engineering,* C. Belove, Ed., New York: Wiley-Interscience, 1986, p. 868. With permission.)

Schottky diodes are formed from junctions of metal and an n-type semiconductor, the metal fulfilling the role of the p-region. Since there are thus no minority carriers in the region of the forward-biased junction, the storage time required to bring a pn junction out of saturation is eliminated. The forward-biased drop across a Schottky diode is around 0.3 V. This clamps the collector at 0.3 V less than the base, thus maintaining  $V_{CE}$  above the 0.3-V saturation threshold. Circuits for the two-input NAND gates 74LS00 and 74S00 are given in Figure 1.11(a) and (b). The special transistor symbol is a short-form notation indicating the presence of the Schottky diode, as illustrated in Figure 1.11(c).

**FIGURE 1.11** Transistor-transistor logic (TTL) nonsaturated logic. (a) Type 74LS00 two-input NAND gate, (b) type 74S00 two-input NAND gate, (c) significance of the Schottky transistor symbol. (*Source:* P. Graham, "Gates," in *Handbook of Modern Electronics and Electrical Engineering,* C. Belove, Ed., New York: Wiley-Interscience, 1986, p. 870. With permission.)

Note that both of these circuits have an active pull-down transistor  $T_6$  replacing the pull-down resistance connected to the emitter of  $T_2$  in Figure 1.9. The addition of  $T_6$  decreases the turn-on and turn-off times of  $T_4$ . In addition, the transfer characteristic for these devices is improved by the squaring off of the sloping region between  $V_i = 0.55$  and 1.2 V [see Figure 1.8(c)]. This happens because  $T_2$  cannot become active until  $T_6$  turns on, which requires at least 1.2 V at the input.

TABLE 1.6 Comparison of TTL Two-Input NAND Gates

|             | Supply Current                        |                          | Propagation<br>Delay Time |                          | Noise<br>Margins       |                        |                     |                      |             |

|-------------|---------------------------------------|--------------------------|---------------------------|--------------------------|------------------------|------------------------|---------------------|----------------------|-------------|

| TTL<br>Type | I <sub>CCH</sub> <sup>a</sup><br>(mA) | I <sub>CCL</sub><br>(mA) | t <sub>PLH</sub><br>(ns)  | t <sub>PHL</sub><br>(ns) | NM <sub>H</sub><br>(V) | NM <sub>L</sub><br>(V) | Load<br>Factor, H/L | Drive<br>Factor, H/L | Fan-<br>Out |

| 74F00       | 2.8                                   | 10.2                     | 2.9                       | 2.6                      | 0.7                    | 0.3                    | 0.5/0.375           | 25/12.5              | 33          |

| 74S00       | 10                                    | 20                       | 3                         | 3                        | 0.7                    | 0.3                    | 1.25/1.25           | 25/12.5              | 10          |

| 74H00       | 10                                    | 26                       | 5.9                       | 6.2                      | 0.4                    | 0.4                    | 1.25/1.25           | 12.5/12.5            | 10          |

| 74LS00      | 0.8                                   | 2.4                      | 9                         | 10                       | 0.7                    | 0.3                    | 0.5/0.25            | 10/5                 | 20          |

| 7400        | 4                                     | 12                       | 11                        | 7                        | 0.4                    | 0.4                    | 1/1                 | 20/10                | 10          |

| 74L00       | 0.44                                  | 1.16                     | 31                        | 31                       | 0.4                    | 0.5                    | 0.24/0.1125         | 5/2.25               | 20          |

<sup>a</sup>See text for explanation of abbreviations.

Source: P. Graham, "Gates," in Handbook of Modern Electronics and Electrical Engineering, C. Belove, Ed., New York: Wiley-Interscience, 1986, p. 871. With permission.

The diode AND circuit of the 74LS00 in place of the multi-emitter transistor will permit maximum input levels substantially higher than the 5.5-V limit set for all other TTL families. Input leakage currents for 74LSxx are specified at  $V_i = 10$  V, and input voltage levels up to 15 V are allowed. The 74LSxx has the additional feature of the Schottky diode  $D_1$  in series with the 100- $\Omega$  output resistor. This allows the output to be pulled up to 10 V without causing a reverse breakdown of  $T_5$ . The relative characteristics of the several versions of the TTL two-input NAND gate are compared in Table 1.6. The 74F00 represents one of the new technologies that have introduced improved Schottky TTL in recent years.

**TTL Design Considerations.** Before undertaking construction of a logic system, the wise designer consults the information and recommendations provided in the data books of most manufacturers. Some of the more significant tips are provided here for easy reference.

- 1. **Power supply, decoupling, and grounding.** The power supply voltage should be 5 V with less than 5% ripple factor and better than 5% regulation. When packages on the same printed circuit board are supplied by a bus there should be a  $0.05-\mu$ F decoupling capacitor between the bus and the ground for every five to ten packages. If a ground bus is used, it should be as wide as possible, and should surround all the packages on the board. Whenever possible, use a ground plane. If a long ground bus is used, both ends must be tied to the common system ground point.

- 2. Unused gates and inputs. If a gate on a package is not used, its inputs should be tied either high or low, whichever results in the least supply current. For example, the 7400 draws three times the current with the output low as with the output high, so the inputs of an unused 7400 gate should be grounded. An unused input of a gate, however, must be connected so as not to affect the function of the active inputs. For a 7400 NAND gate, such an input must either be tied high or paralleled with a used input. It must be recognized that paralleled inputs count as two when determining the fan-out. Inputs that are tied high can be connected either to  $V_{\rm CC}$  through a 1-k $\Omega$  or more resistance (for protection from supply voltage surges) or to the output of an unused gate whose input will establish a permanent output high. Several inputs can share a common protective resistance. Unused inputs of low-power Schottky TTL can be tied directly to  $V_{\rm CC}$ , since 74LSxx inputs tolerate up to 15 V without breakdown. If inputs of low-power Schottky are connected in parallel and driven as a single input, the switching speed is decreased, in contrast to the situation with other TTL families.

- 3. Interconnection. Use of line lengths of up to 10 in. (5 in. for 74S) requires no particular precautions, except that in some critical situations lines cannot run side by side for an appreciable distance without causing cross talk due to capacitive coupling between them. For transmission line connections, a gate should drive only one line, and a line should be terminated in only one gate input. If overshoots are a problem, a 25- to  $50-\Omega$  resistor should be used in series with the driving gate input and the receiving gate input should be pulled up to 5 V through a 1-k $\Omega$  resistor. Driving and receiving gates should

have their own decoupling capacitors between the  $V_{\rm CC}$  and ground pins. Parallel lines should have a grounded line separating them to avoid cross talk.

4. **Mixing TTL subfamilies.** Even synchronous sequential systems often have asynchronous features such as reset, preset, load, and so on. Mixing high-speed 74S TTL with lower speed TTL (74LS for example) in some applications can cause timing problems resulting in anomalous behavior. Such mixing is to be avoided, with rare exceptions which must be carefully analyzed.

#### **Emitter-Coupled Logic**

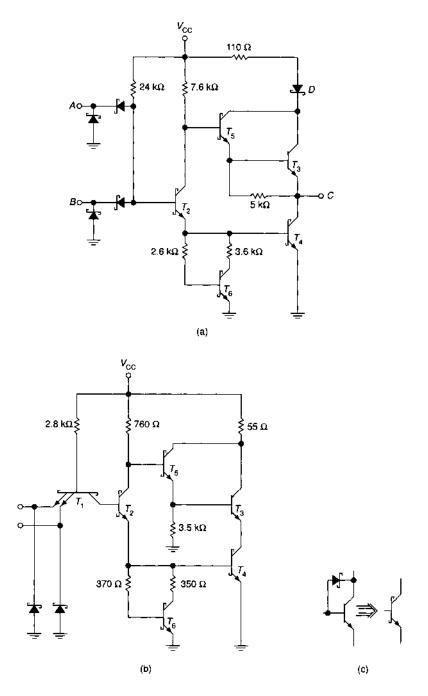

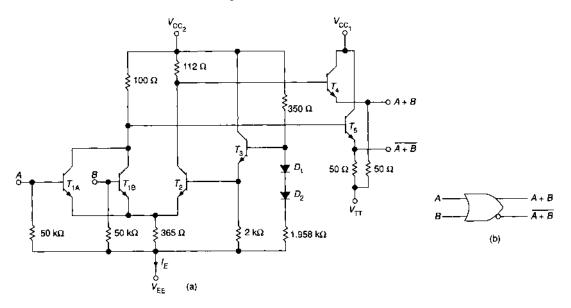

ECL is a nonsaturated logic family where saturation is avoided by operating the transistors in the common collector configuration. This feature, in combination with a smaller difference between the HIGH and LOW voltage levels (less than 1 V) than other logic families, makes ECL the fastest logic available at this time. The circuit diagram of a widely used version of the basic two-input ECL gate is given in Figure 1.12. The power supply terminals  $V_{CC1}$ ,  $V_{CC2}$ ,  $V_{EE}$ , and  $V_{TT}$  are available for flexibility in biasing. In normal operation,  $V_{CC1}$  and  $V_{CC2}$  are connected to a common ground,  $V_{EE}$  is biased to -5.2 V, and  $V_{TT}$  is biased to -2 V. With these values the nominal voltage for the logical 0 and 1 are, respectively, -1.75 and -0.9 V. Operation with the  $V_{CC}$  terminals grounded maximizes the immunity from noise interference.

A brief description of the operation of the circuit will verify that none of the transistors saturates. For the following discussion,  $V_{CC1}$  and  $V_{CC2}$  are grounded,  $V_{EE}$  is -5.2 V, and  $V_{TT}$  is -2 V. Diode drops and base-emitter voltages of active transistors are 0.8 V.

First, observe that the resistor-diode  $(D_1 \text{ and } D_2)$  voltage divider establishes a reference voltage of -0.55 V at the base of  $T_3$ , which translates to -1.35 V at the base of  $T_2$ . When either or both of the inputs A and B are at the logical 1 level of -0.9 V, the emitters of  $T_{1A}$ ,  $T_{1B}$ , and  $T_2$  will be 0.8 V lower, at -1.7 V. This establishes the base-emitter voltage of  $T_2$  at -1.35-(-1.7) = 0.35 V, so  $T_2$  is cut off. With  $T_2$  off,  $T_4$  is biased into the active region, and its emitter will be at about -0.9 V, corresponding to a logical 1 at the (A + B) output. Most of the current through the 365- $\Omega$  emitter resistor, which is [-1.7-(-5.2)]/0.365 = 9.6 mA, flows through the 100- $\Omega$  collector resistor, dropping the base voltage of  $T_5$  to -0.96 V. Thus the voltage level at the output terminal designated (A + B) is -1.76 V, corresponding to a logical 0.

When both A and B inputs are at the LOW level of -1.75 V,  $T_2$  will be active, with its emitter voltage at -1.35-0.8 = -2.15 V. The current through the 365- $\Omega$  resistor becomes [-2.15-(-5.2)]/0.365 = 8.2 mA.

**FIGURE 1.12** Emitter-coupled logic basic gate (ECL 10102): (a) circuit, (b) symbol. (*Source:* P. Graham, "Gates," in *Handbook of Modern Electronics and Electrical Engineering*, C. Belove, Ed., New York: Wiley-Interscience, 1986, p. 872. With permission.)

This current flows through the 112- $\Omega$  resistor pulling the base of  $T_4$  down to -0.94 V, so that the (A + B) output will be at the LOW level of -1.75 V. With  $T_{1A}$  and  $T_{1B}$  cut off, the base of  $T_5$  is close to 0.0 V, and the (A + B) output will therefore be at the nominal HIGH level of -0.9 V.

Observe that the output transistors  $T_4$  and  $T_5$  are always active and function as emitter followers, providing the low-output impedances required for driving capacitive loads. As  $T_{1A}$  and/or  $T_{1B}$  turn on, and  $T_2$  turns off as a consequence, the transition is accomplished with very little current change in the 365- $\Omega$  emitter resistor. It follows that the supply current from  $V_{EE}$  does not undergo the sudden increases and decreases prevalent in TTL, thus eliminating the need for decoupling capacitors. This is a major reason why ECL can be operated successfully with the low noise margins which are inherent in logic having a relatively small voltage difference between the HIGH and LOW voltage levels (see Table 1.7). The small level shifts between LOW and HIGH also permit low propagation times without excessively fast rise and fall times. This reduces the effects of residual capacitive coupling between gates, thereby lessening the required noise margin. For this reason the faster ECL (100xxx) should not be used where the speed of the 10xxx series is sufficient. A comparison of three ECL series is given in Table 1.7. The propagation times  $t_{PLH}$  and  $t_{PHL}$  and transition times  $t_{TLH}$  and  $t_{THL}$  are defined in Figure 1.7. Transitions are between the 20 and 80% levels.

The 50- $\Omega$  pull-down resistors shown in Figure 1.12 are connected externally. The outputs of several gates can therefore share a common pull-down resistor to form a wired-OR connection. The open emitter outputs also provide flexibility for driving transmission lines, the use of which in most cases is mandatory for interconnecting this high-speed logic. A twisted pair interconnection can be driven using the complementary outputs (A + B) and (A + B) as a differential output. Such a line should be terminated in an ECL line receiver (10114).

Since ECL is used in high-speed applications, special techniques must be applied in the layout and interconnection of chips on circuit boards. Users should consult design handbooks published by the suppliers before undertaking the construction of an ECL logic system.

While ECL is not compatible with any other logic family, interfacing buffers, called translators, are available. In particular, the 10124 converts TTL output levels to ECL complementary levels, and the 10125 converts either single-ended or differential ECL outputs to TTL levels. Among other applications of these translators, they allow the use of ECL for the highest speed requirements of a system while the rest of the system uses the more rugged TTL. Another translator is the 10177, which converts the ECL output levels to *n*-channel metal-oxide semiconductor (NMOS) levels. This is designed for interfacing ECL with *n*-channel memory systems.

|              | Power Supply<br>Terminal | Power Supply<br>Current | 1                         | gation<br>Time           | Transition<br>Time        |                           | Noise<br>Margins       |                        |              |

|--------------|--------------------------|-------------------------|---------------------------|--------------------------|---------------------------|---------------------------|------------------------|------------------------|--------------|

| ECL<br>Type  | $V_{ m EE}$ (V)          | I <sub>E</sub><br>(mA)  | $t_{\rm PLH}^{}^{a}$ (ns) | t <sub>PHL</sub><br>(ns) | $t_{\text{TLH}}^{b}$ (ns) | $t_{\text{THL}}^{b}$ (ns) | NM <sub>H</sub><br>(V) | NM <sub>L</sub><br>(V) | Test<br>Load |

| ECL II       |                          |                         |                           |                          |                           |                           |                        |                        |              |

| 1012         | -5.2                     | 18 <sup>c</sup>         | 5                         | 4.5                      | 4                         | 6                         | 0.175                  | 0.175                  | Fan-out of 3 |

| 95102        | -5.2                     | 11                      | 2                         | 2                        | 2                         | 2                         | 0.14                   | 0.145                  | 50 Ω         |

| 10102        | -5.2                     | 20                      | 2                         | 2                        | 2.2                       | 2.2                       | 0.135                  | 0.175                  | 50 <b>Ω</b>  |

| ECL III      |                          |                         |                           |                          |                           |                           |                        |                        |              |

| 1662         | -5.2                     | 56 <sup>c</sup>         | 1                         | 1.1                      | 1.4                       | 1.2                       | 0.125                  | 0.125                  | 50 <b>Ω</b>  |

| $100102^{d}$ | -4.5                     | 55                      | 0.75                      | 0.75                     | 0.7                       | 0.7                       | 0.14                   | 0.145                  | 50 Ω         |

| $11001^{e}$  | -5.2                     | 24                      | 0.7                       | 0.7                      | 0.7                       | 0.7                       | 0.145                  | 0.175                  | 50 Ω         |

**TABLE 1.7** Comparison of ECL Quad Two-Input NOR Gates ( $V_{TT} = V_{EE} = 5.2$  V,  $V_{CC1} = 0$  V)

<sup>a</sup>See text for explanation of abbreviations.

<sup>b</sup>20 to 80% levels.

<sup>c</sup>Maximum value (all other typical).

<sup>d</sup>Quint 2-input NOR/OR gate.

<sup>e</sup>Dual 5/4-input NOR/OR gate.

Source: P. Graham, "Gates," in Handbook of Modern Electronics and Electrical Engineering, C. Belove, Ed., New York: Wiley-Interscience, 1986, p. 873. With permission.

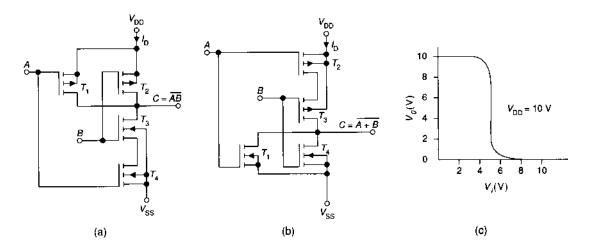

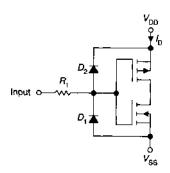

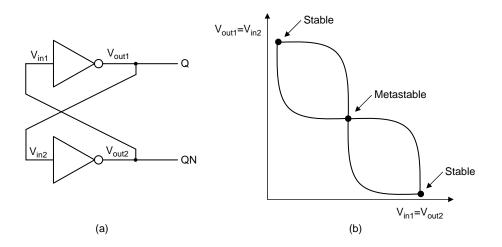

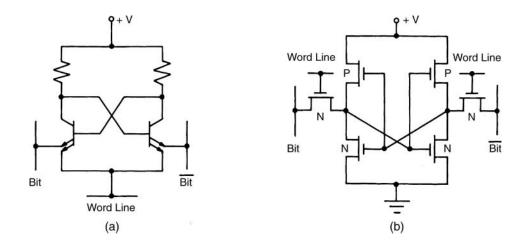

#### Complementary Metal-Oxide Semiconductor (CMOS) Logic

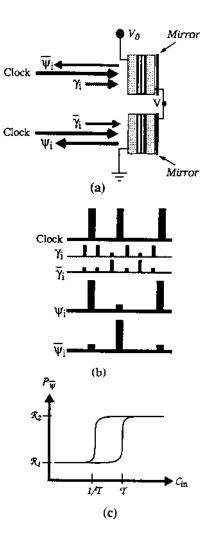

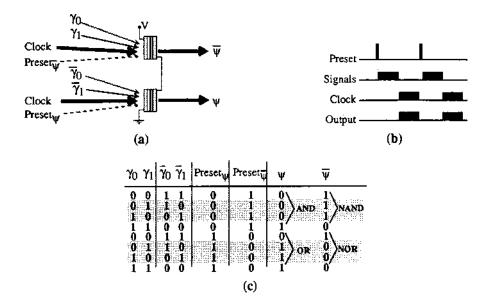

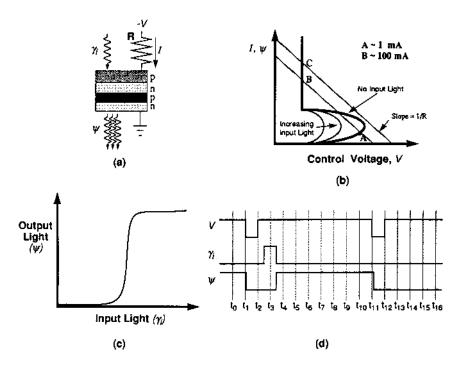

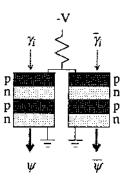

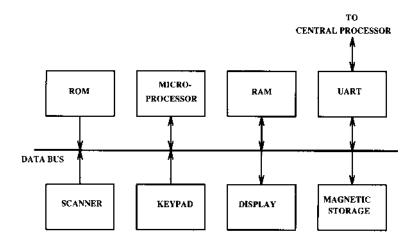

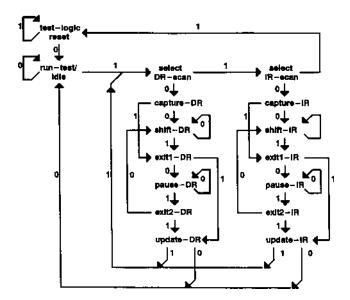

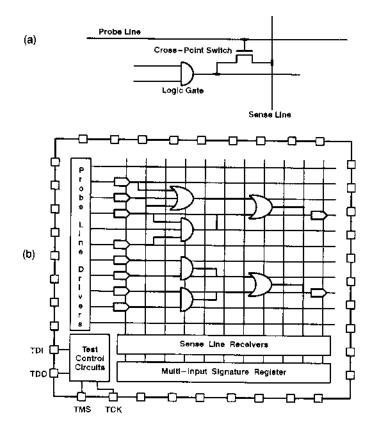

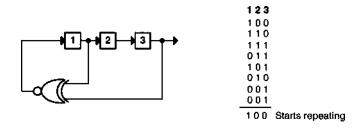

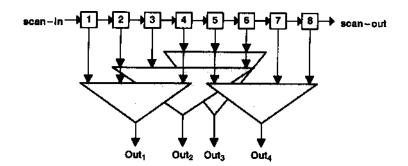

Metal-oxide semiconductor (MOS) technology is prevalent in LSI systems due to the high circuit densities possible with these devices. *p*-Channel MOS was used in the first LSI systems, and it still is the cheapest to produce because of the higher yields achieved due to the longer experience with PMOS technology. PMOS, however, is largely being replaced by NMOS (*n*-channel MOS), which has the advantages of being faster (since electrons have greater mobility than holes) and having TTL compatibility. In addition, NMOS has a higher function/chip area density than PMOS, the highest density in fact of any of the current technologies. Use of NMOS and PMOS, however, is limited to LSI and VLSI fabrications. The only MOS logic available as SSI and MSI is CMOS (complementary MOS).