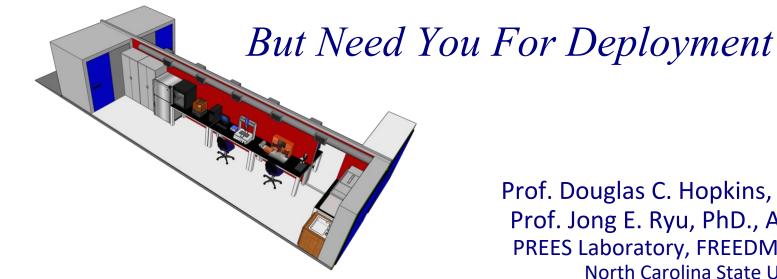

An Electronic Packaging Lab In A Box (for YOUR Community College)

Prof. Douglas C. Hopkins, Ph.D., Director Prof. Jong E. Ryu, PhD., Assoc. Director PREES Laboratory, FREEDM System Center North Carolina State University 1791 Varsity Dr., Suite 100 Raleigh, NC 27606-7571 dchopkins@ncsu.edu, jryu@ncsu.edu

DCHopkins@ncsu.edu JRyu@ncsu.edu ©2024 NC State University

U.S. Department of Commerce, NIST, National Advanced Packaging Manufacturing Program (NAPMP) Advanced Packaging Research and Development (R&D) NOFO: 2025-NIST-CHIPS-NAPMP-01

Credit: Adobe Stock

- The NAPMP seeks to drive U.S. leadership in advanced packaging and provide the technology and skilled workforce needed for packaging manufacturing in the United States.

- Within a decade, NAPMP-funded activities, coupled with CHIPS manufacturing incentives, will establish a vibrant, self- sustaining, profitable, domestic advanced packaging industry where advanced-node chips manufactured in the United States and abroad can be packaged in appropriate volumes within the United States and innovative designs and architectures are enabled through leading-edge packaging capabilities.

- In combination with other CHIPS for America education and workforce efforts, NAPMP-funded activities will produce the diverse and capable workforce needed for the success of the domestic packaging sector.

- The objective of this NOFO is to enable, through R&D, innovative new advanced packaging flows suitable for adoption by U.S. industry.

CHIPS R&D anticipates making available up to approximately \$1,550,000,000 for funding Anticipated amounts ranging from ~\$10M to ~\$150M <u>over a five (5) year period</u> of performance.

#### This NOFO envisions projects in five (5) R&D Areas:

| R&D Area                                              | Total<br>Funding | Anticipated<br>Max Award |

|-------------------------------------------------------|------------------|--------------------------|

| (1) Equip., Tools, Processes, and Process Integration | \$450M           | \$150M                   |

| (2) Power Delivery and Thermal Management             | \$250M           | \$50M                    |

| (3) Connector Technology, Incl. Photonics and RF      | \$250M           | \$100M                   |

| (4) Chiplets Ecosystem                                | \$300M           | \$75M                    |

| (5) Co-Design / EDA                                   | \$250M           | \$100M                   |

DCHopkins@ncsu.edu JRyu@ncsu.edu ©2024 NC State University

## Where do you fit in?

What can you do? What can your company do? What can this do for your Company?

### **1.7 Project Level Non-Technical Plans**

1.7.1 Education and Workforce Development (EWD) Plans

- NAPMP investments are intended to create innovation-driven domestic manufacturing capability, which requires fostering a diverse and capable domestic workforce with access to good jobs, such as those consistent with the Good Jobs Principles.

- The combination of expertise, facilities, and equipment required to meet the technical targets described in Section 1.4 provide *exceptional opportunities for tailored EWD programs*.

- In developing an EWD plan, CHIPS R&D encourages applicants to consult the

- CHIPS R&D Education and Workforce Development (EWD) Plan Guidebook and

- Department of Commerce Workforce Development Strategy Principles.

... describe any efforts to **attract and retain a diverse student and trainee population** and to demonstrate that the EWD efforts are worker-centered, industry-aligned, and promote high-quality jobs.

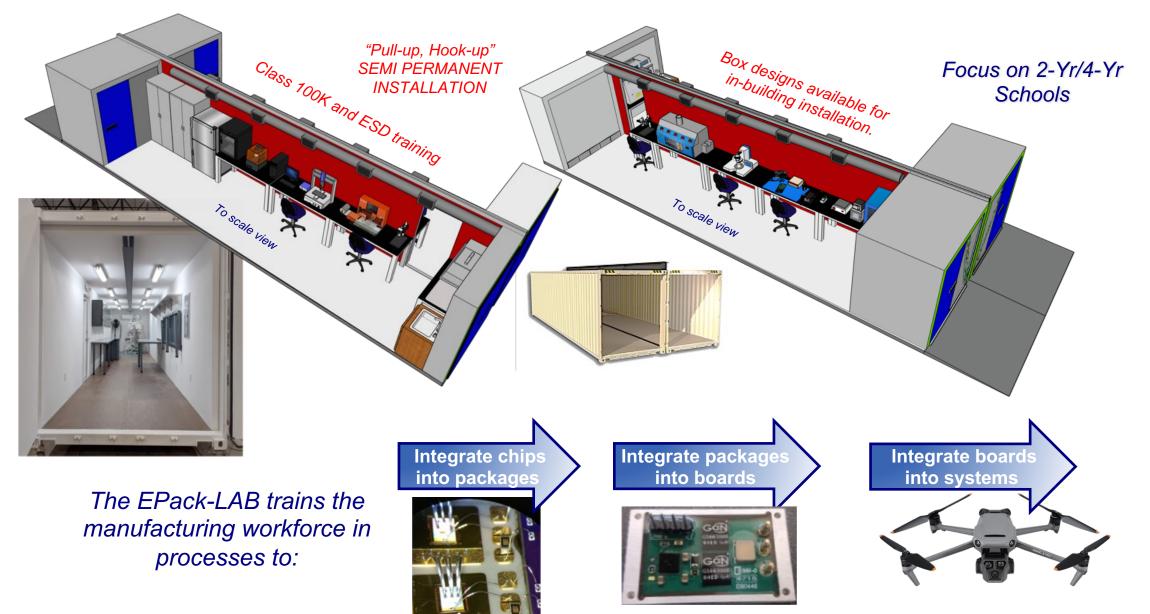

## Electronic Packaging Lab in A Box (EPACK-LAB) Program

#### Formal Edu driven by professional educators:

- Engineering science learning modules

- Training modules for the physical lab

#### **Personnel additions & support:**

- Electronics Manufacturing Technology Educator

- 2<sup>nd</sup>/3<sup>rd</sup> Career technical support Instructors

- Curriculum integration and collaboration

### Infrastructure coordination for student:

- Full tuition waiver

- Childcare

- Incentive stipends

### Industry-Wide sustainability support

- Empower small business two-way partnership

- Expand the 'BOX' to be a prototyping business

**Example Project Outcomes:** Audio amplifier, PV phone charger, Drone propulsion, LED light show, etc.

DCHopkins@ncsu.edu JRyu@ncsu.edu ©2024 NC State University

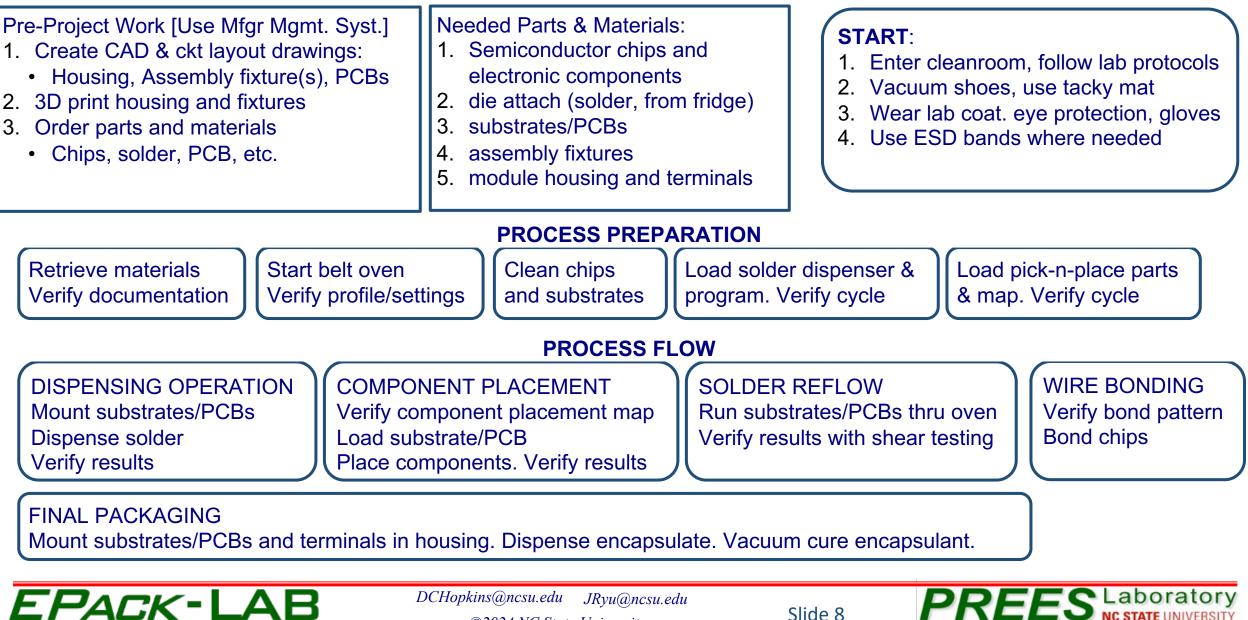

# Example: Process Flow for Students

PACKAGING RESEARCH IN ELECTRONIC ENERGY SYSTEMS

©2024 NC State University

### PREES: PROCESS FLOW

DISPENSING OPERATION Mount substrates/PCBs Dispense solder Verify results

COMPONENT PLACEMENT Verify component placement map Load substrate/PCB Place components. Verify results

SOLDER REFLOW Run substrates/PCBs thru oven Verify results with shear testing

DCHopkins@ncsu.edu JRyu@ncsu.edu ©2024 NC State University

# INFORMATION TECHNOLOGY FOR MANUFACTURING:

Computer Aided Design

WIRE BONDING

Bond chips

Verify bond pattern

Slide 9

- Statistical Process Control (SPC)

- Manufacturing Execution Systems (MES)

- Process Management [e.g. Simul8]

- Supply Chain Management [e.g. Simul8]

PREES Laboratory PACKAGING RESEARCH IN ELECTRONIC ENERGY SYSTEMS

## WE NEED TO CREATE A SEED "PROPOSAL" FOR FUNDING

### WHAT OUR PROPOSAL WILL DO:

Identify and Organize Infrastructure Teams To:

- Contact 2Yr/4Yr college administrators to define the rural needs

- Contact small rural businesses to define their workforce needs

- Advertise and solicit potential "2<sup>nd</sup>/3<sup>rd</sup> Career" technical training staff

- Contact large equipment manufacturers to define human/machine interface needs (AR/VR)

- Contact national technology development HUBs to synergize with their WFD/EWD programs Create metrics and a preliminary business plan to identify potential business(es) to design, build, transport, install & warrant an EPack-LAB fabrication facility

Develop a National Proposal Team bringing together the above Teams, MEC Hubs, and identify the key metrics and budget for national deployment of the EPack-LAB program

### SIGN UP TO MAKE A DIFFERENCE

### https://go.ncsu.edu/epack-lab-partners

DCHopkins@ncsu.edu JRyu@ncsu.edu ©2024 NC State University

#### Prof. Douglas C. Hopkins, Ph.D., Director Prof. Jong E. Ryu, PhD., Assoc. Director Laboratory for Packaging Research in Electronic Energy Systems (PREES) FREEDM System Center North Carolina State University 1791 Varsity Dr., Suite 100; Raleigh, NC 27606-7571

dchopkins@ncsu.edu, jryu@ncsu.edu

DCHopkins@ncsu.edu JRyu@ncsu.edu ©2024 NC State University

### 3D Heterogeneous Power Integration Incorporating ANN ML and Genetic Algorithms for TSV/TGV Optimization

#### Presenter and Co-Author: Prof. Douglas C. Hopkins

Pouria Zaghari, Sourish S. Sinha, Prof. Jong E. Ryu

North Carolina State University

Raleigh, NC, USA

jryu@ncsu.edu, dchopkins@ncsu.eduSlide 12

A portion of his work was sponsored by the United States Defense Advanced Research Projects Agency under grant D23AP00062-00, part of their "Next Generation Microelectronics Manufacturing" (NGMM) initiative. The content of the information does not necessarily reflect the position or the policy of the Government, and no official

JRvu@ncsu.edu

©2024 NC State University

DCHopkins@ncsu.edu

Slide 12 of 25