### Outline

- What is IDA (In Design Analysis)

- (5) How can IDA improve you designs and speed up time to market

- Optimality how can this optimize your design with AI

# Why IDA To Constrain or Not To Constrain

- Constraint driven design is the backbone of any solid design methodology

- ► Focus is on finding and resolving violations

- Traditionally involves Constraint Manager and DRC Markers

- Existing options for Impedance, Coupling and Return Path

- Rules are required

- ▶ But may be a hinderance to starting any kind of analysis

- Screening Analysis also has a place

- Rules are not required

- Easier to get a snapshot of the entire design or any portion

- ► Focus is on result viewing

- New Analysis Workflows offer new methodologies to enhance existing design flows

### Problem Statement

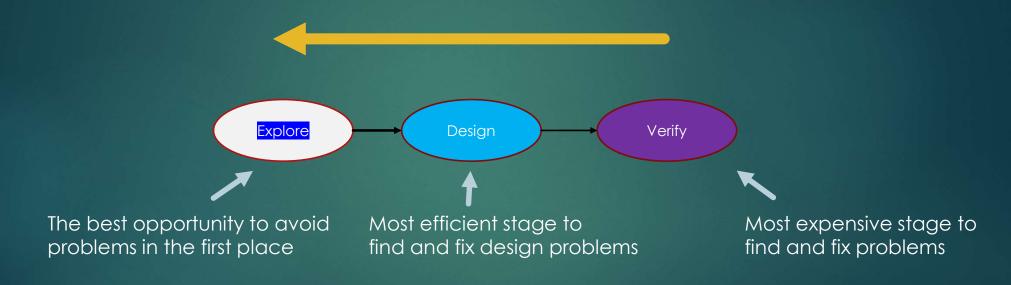

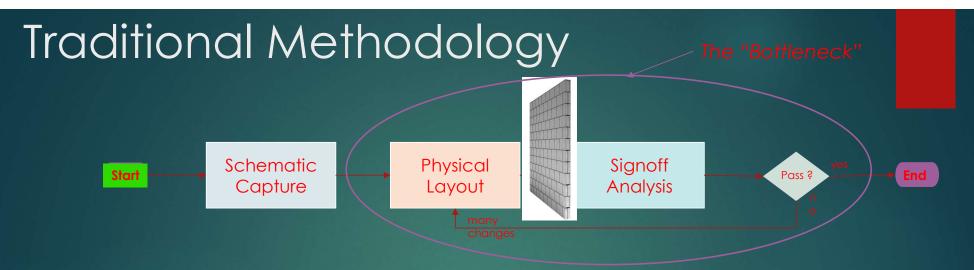

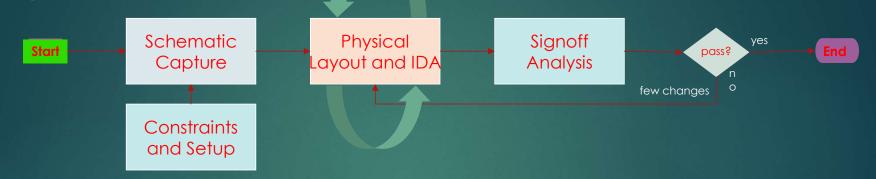

With time-to-market, cost, and performance pressures, system designers are seeking a "shift left" to streamline their methodologies

Must move beyond just post-layout verification

Accomplishing this involves tools, methodology, and some re-thinking of organizational roles

- Physical layout goes "over the wall" to analysis expert

- Eventually some requested changes go back to layout designer

- Changes get manually implemented; issues resolved?

- Back over the wall the layout goes

- Inefficient:

- ▶ Multiple iterative loops, disrupting schedule

- Manual changes

- Across organizations

- ▶ Bottlenecked by Analysis Expert resources

Design Engineer

Layout Designer

**Analysis Expert**

Introduction and Agenda

# Methodology with In-Design Analysis (IDA)

- The design engineer and analysis expert provide constraints and analysis setup before the physical layout

- ► Layout designer empowered with actionable, real-time analysis feedback in their native environment, where they can quickly make edits and re-analyze independently

- ► Fewer issues at the signoff stage

- Efficiency goes up and schedule compresses

Design Engineer

Layout Designer

**Analysis Expert**

Introduction and Agenda

### Collaboration and Workflow

## Collaborative Design Environment

#### **Multi-Stakeholder Participation**

Allegro IDA enables multiple stakeholders to actively participate in the collaborative design process.

#### Real-Time Feedback

Real-time feedback and shared analysis results enhance communication and decision-making among team members.

#### **Integrated Communication Tools**

Integrated communication tools streamline teamwork and ensure alignment for higher quality designs.

#### **Seamless Workflow Integration**

The workflow supports seamless integration with other platforms, boosting overall project efficiency.

Collaboration and Workflow

# Workflow Integration and Benefits

### **Seamless Workflow Integration**

Integration facilitates smooth transitions between design, analysis, and optimization phases, streamlining the overall process.

### **Error Reduction and Efficiency**

Reducing manual effort and errors accelerates the design cycle and improves overall productivity and accuracy.

### **Comprehensive EDA Solution**

Supports schematic capture, layout design, and system-level optimization for a complete electronic design automation workflow.

## Why Use IDA

### **Real-Time Analysis**

IDA provides real-time analysis, allowing designers to detect and solve issues during the design process promptly.

### **Integrated Checking**

The tool offers integrated checking capabilities that improve design quality by identifying problems early.

### **Enhanced Collaboration**

IDA enhances team collaboration by seamlessly integrating with other design tools and supporting communication.

### **Supports Various Analyses**

It supports multiple analysis types like signal and power integrity, ensuring comprehensive design validation.

**IDA Features and Flows**

### **IDA** Features and Flows

## Aurora IDA workflows

### **IDA Features and Flows**

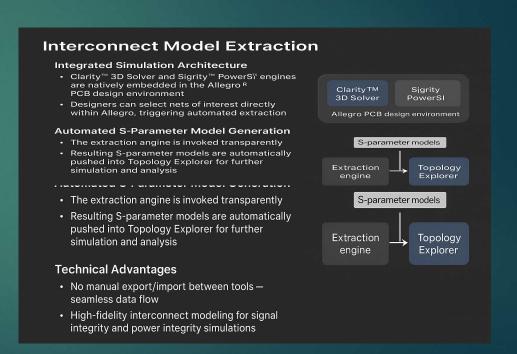

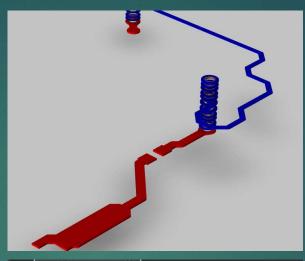

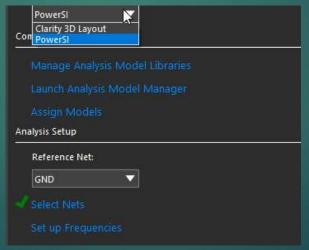

### Interconnect Model Extraction

- Integrated Simulation Architecture

- ► Clarity<sup>™</sup> 3D Solver and Sigrity<sup>™</sup> PowerSI® engines embedded in Allegro® PCB design environment

- Direct net selection within Allegro triggers automated extraction

- Automated S-Parameter Model Generation

- Transparent invocation of extraction engine

- S-parameter models pushed into Topology Explorer for simulation

- ▶ Technical Advantages

- Seamless data flow between design and analysis tools

- High-fidelity interconnect modeling

- ▶ Accelerated design validation

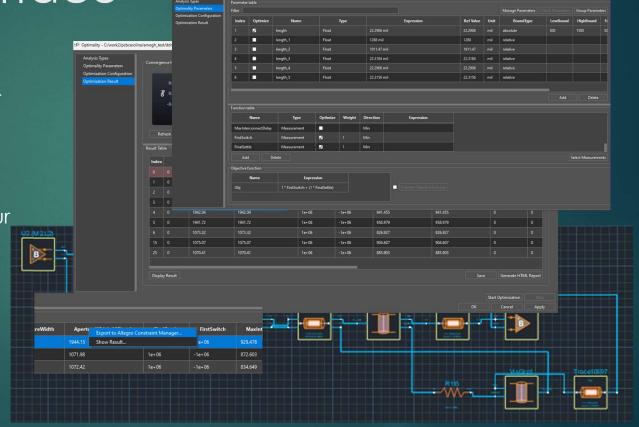

Optimization Workflows and System Strategy

Topology Workbench and Optimality interface

Optimized simulation based upon defined criteria. Using an Al agent to help pick most optimum simulation and results

This could help predict and produce constraints based up your extracted nets in simulation.

Cut detailed simulation sweeps down by 100x

### Optimization Workflows and System Strategy

# Optimization Workflows

### **Comprehensive System Design**

Optimization workflows address thermal management, signal integrity, and mechanical constraints in system design.

### **Guided Problem Solving**

Workflows assist users in identifying issues, evaluating alternatives, and implementing effective solutions.

### **Iterative Optimization**

The tool supports continuous improvement through iterative optimization and refinement processes.

### **Enhanced Performance and Reliability**

Following optimization workflows leads to optimal product performance and enhanced reliability.

### Optimization Workflows and System Strategy

## System Design Strategy

### Strategic Planning in Design

System design strategy involves careful planning and execution to meet defined project goals effectively.

### **Optimality Explorer Benefits**

Optimality Explorer aids in strategic decisions by revealing design tradeoffs and key performance metrics.

### **Alignment with Objectives**

The tool helps align design choices with project goals to ensure all requirements are fulfilled.

### **Improved Outcomes**

A well-defined strategy increases efficiency, reduces risks, and improves overall design results.

# Overview of Optimality Explorer

### **Advanced Algorithm Optimization**

Optimality Explorer uses cutting-edge algorithms to enhance system design strategies efficiently.

### **Multi-Discipline Support**

Supports optimization workflows across thermal, mechanical, and electrical system analyses.

### **Actionable Insights and Recommendations**

Provides clear insights and design recommendations to guide informed decision-making.

### **User-Friendly Interface**

Features an intuitive interface that enhances user experience and accessibility in design workflows.

Optimality Explorer and Future Directions

# Future Directions and Innovations

### **Al Integration Enhancement**

Enhanced AI integration aims to improve analysis and design optimization in Allegro IDA and Optimality Explorer.

### **Expanded Analysis Capabilities**

Expanding analysis capabilities enables deeper insights into design performance and problem-solving.

### **Improved User Interfaces**

Improved user interfaces streamline workflows and enhance user experience for designers.

### **Automation and Workflow Streamlining**

Innovations focus on increasing automation to speed up processes and improve product delivery time.

Optimality Explorer and Future Directions

# cadence®

© 2025 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <a href="https://www.cadence.com/go/trademarks">https://www.cadence.com/go/trademarks</a> are trademarks or registered trademarks or service marks or leader trademarks or service marks of Accellera Systems Inc. Accellera and SystemC are trademarks of Accellera Systems Initiative Inc. All Arm products are registered trademarks or trademarks or Arm Limited (or its subsidiaries) in the US and/or elsewhere. All MIPI specifications are registered trademarks or trademarks or PCI-SIG. All other trademarks are the property of their respective owners.

### Overview of Allegro IDA & Optimality Explorer

### **Integrated Analysis**

Real-time SI/PI checks within PCB design

### **Correct-by-Design**

Embedded verification reduces errors early

### Collaboration

Multi-stakeholder workflows with real-time feedback

### **Optimization**

Intelligent algoritons for thermal, mechanical, electrical design

### **Benefits**

Faster cycles, fewer errors Improved design quality

### **Future**

Al integration Expanded analysis

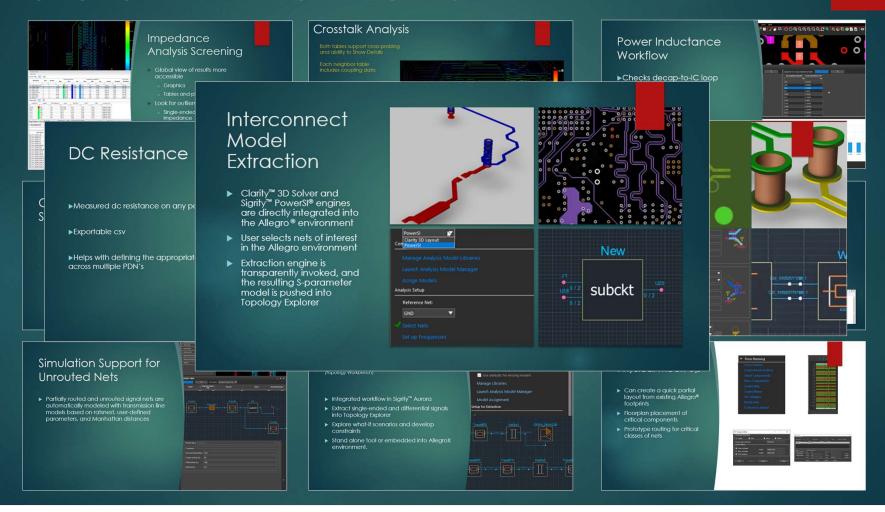

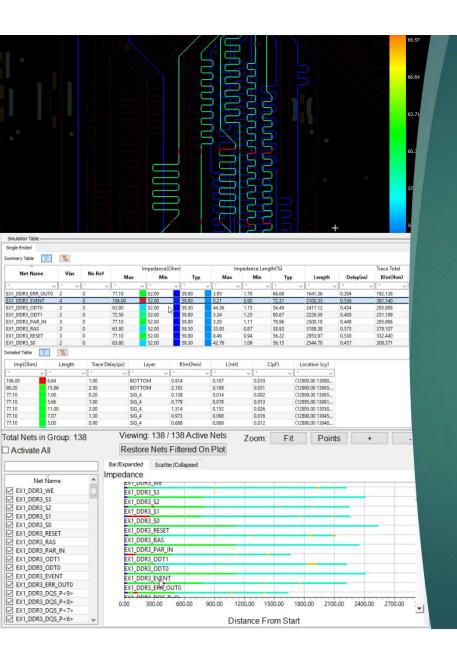

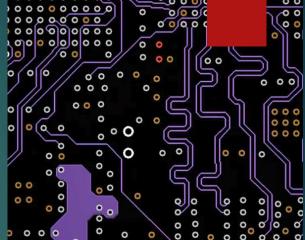

## Impedance Analysis Screening

- Global view of results more accessible

- Graphics

- Tables and plots

- Look for outliers

- Single-ended and differential impedance

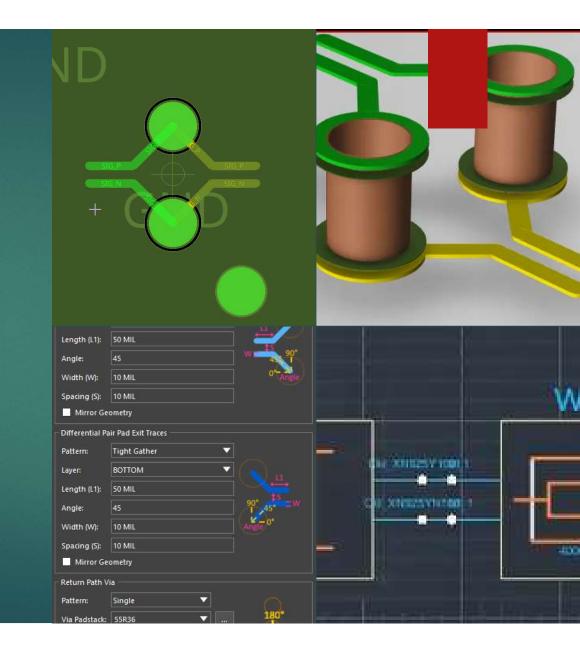

## Easily Create a Physical Mock-Up

- Can create a quick partial layout from existing Allegro® footprints

- Floorplan placement of critical components

- Prototype routing for critical classes of nets

- ► Topology Explorer via block

- ▶ Allegro® Via Generation

- ▶ Clarity<sup>™</sup> Solver

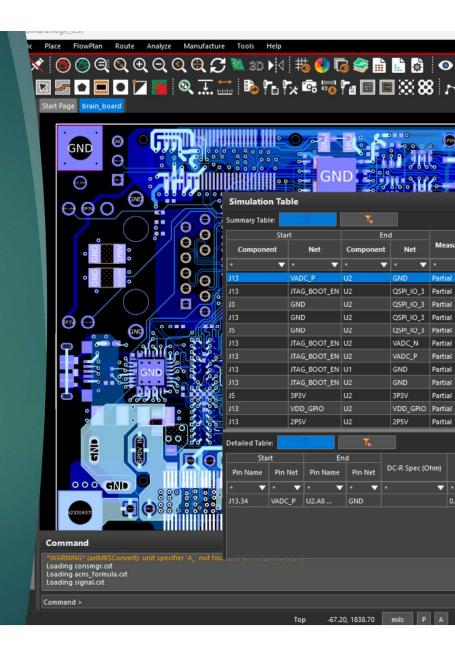

### DC Resistance

- ▶ Measured dc resistance on any power net/plane

- ▶Exportable csv

- ▶ Helps with defining the appropriate power delivery across multiple PDN's

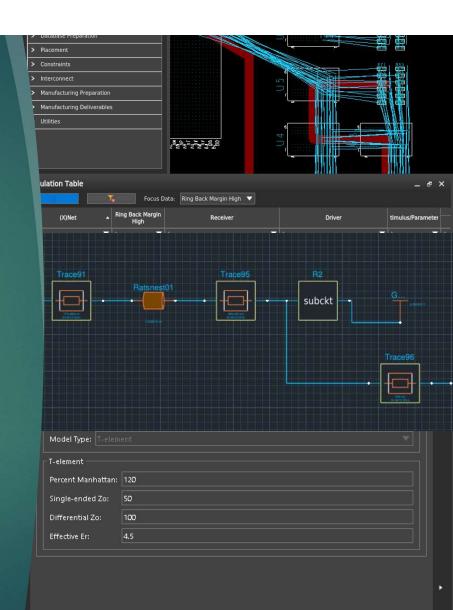

### Interconnect Model Extraction

- Clarity<sup>™</sup> 3D Solver and Sigrity<sup>™</sup> PowerSl<sup>®</sup> engines are directly integrated into the Allegro <sup>®</sup> environment

- User selects nets of interest in the Allegro environment

- Extraction engine is transparently invoked, and the resulting S-parameter model is pushed into Topology Explorer

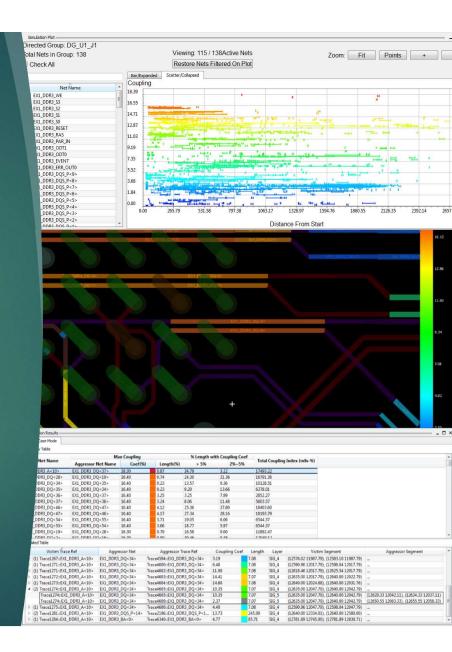

# Coupling Analysis Screening

- No SI models required

- Electrical coupling is more accurate than geometrical methods

- Global view of results

- Graphics

- Tables and plots

## Crosstalk Analysis

Both tables support cross-probing and ability to Show Details

Each neighbor table includes coupling data Victim net/Xnet Aggressor net/X Result/Waveforr Victim Receiver Simulation Type CDS\_IN\_GEN\_3... EACH; LS; ODD;... CDS\_IN\_GEN\_3... EACH; LS; ODD;... CDS\_IN\_GEN\_3... EACH; LS; ODD;... CDS\_IN\_GEN\_3... EACH; LS; ODD;...

CDS\_IN\_GEN\_3... EACH; LS; ODD;...

CDS\_IN\_GEN\_3... EACH; LS; ODD,...

CDS\_IN\_GEN\_3... EACH; HS; ODD... PP CLK3 CDS IN GEN 3... EACH: HS: ODD... Victim Trace Ref Coupling Coef (474.1654 -100.1496), (... (474.1654 -108.4252), (139... (474.1654 -100.1496), (... (474.1654 -98.4252), (1399... Crosstalk Result: 148.20 mV Victim Driver: CDS\_BI\_GEN\_2P5V\_10\_10PF U2 R1 Victim: PP\_A<0> All Neighbor Each Neighbor Crosstalk on Victim: 148.2 mV Zoom: Fit Points + -Victim net/Xnet Result/Waveforr Victim Receiver Simulation Typ 148.2 mV CDS\_IN\_Victim Net:

108.7 mV CDS\_IN\_PP\_A-C0>

108.7 mV CDS\_IN\_PP\_A-C0>

108.4 mV CDS\_IN\_CDS\_BI\_GEN\_285V\_10\_10PF U2 R14 PP\_A<0> PP\_A<10> Simulation: ALL; LS; ODD; TYP Voltage (V) PP\_A<6> 77.8 mV 48.9 mV 0.037 38.3 mV PP A<12> 33.7 mV 0.000

> -0.075 -0.113 -0.129

27.3 mV 24.6 mV 24.3 mV 0.0 mV

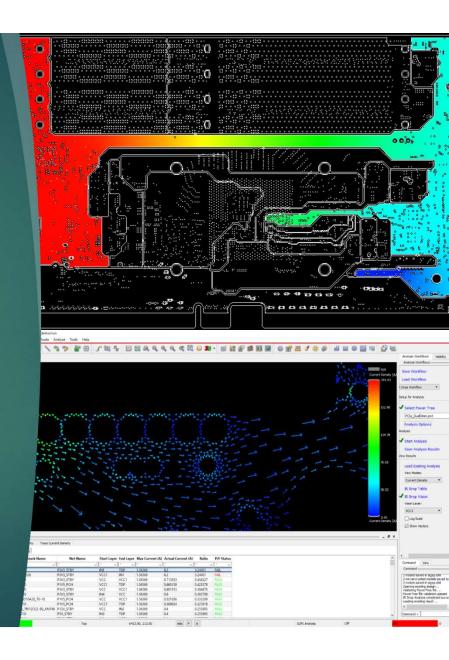

## IR Drop Analysis

- IR drop vision can be displayed as voltage or IR drop

- Voltage drop

- Static voltage measurements

- Current flow and measured drops

- Graphical representation of individual or all power rails

- PowerDC engine

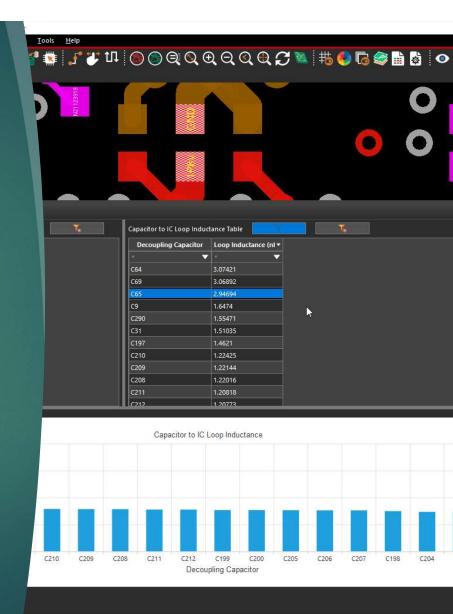

## Power Inductance Workflow

► Checks decap-to-IC loop inductance

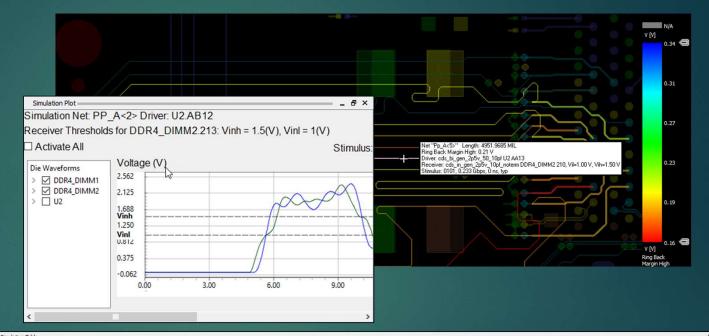

## Reflection Analysis

Vision is selected Focus Data Measurement in Table

Table supports crossprobing, ability to Show Details, and CSV output

| Simulation Table | Focus Data: Ring Bad | c Margin High ▼ |                            |                 |                  |        |                 |     |                  |                  |         |                  |         |   |

|------------------|----------------------|-----------------|----------------------------|-----------------|------------------|--------|-----------------|-----|------------------|------------------|---------|------------------|---------|---|

| (X)Net           | Ring Back Margir     | Receiver        |                            | imulus/Paramete | Ring Back Margin |        | JEDEC Overshoot |     | 'ropagation Dela | Min First Switch |         | Max Final Settle |         |   |

|                  | High                 |                 |                            |                 | High<br>*        | Low    | High            | Low | v = v            | Kise             | Fall ×  | Rise             | Fall    | Л |

| PP A<0>          | 0.18 V               | cds_in_gen_2p5  | cds bi gen 2p5             | 0101, 0.233 Gbp | 0.18 V           | 0.21 V | N/A             | N/A | 0.90 ns          | 1.44 ns          | 1.65 ns | 1.62 ns          | 1.83 ns | 1 |

| PP_A<1>          | 0.16 V               |                 |                            | 0101, 0.233 Gbp |                  | 0.20 V | N/A             | N/A | 0.77 ns          | 1.30 ns          | 1.46 ns | 1.45 ns          | 1.64 ns |   |

| PP_A<2>          | 0.19 V               | cds_in_gen_2n5  | ede hi den 2n5             | 0101, 0.233 Gbp | 0.19 V           | 0.22 V | N/A             | N/A | 0.82 ns          | 1.35 ns          | 1.51 ns | 1.51 ns          | 1.70 ns | 1 |

| PP_A<3>          | 0.18 V               | cds_in_gen_     | Show Details               | 0101, 0.233 Gbp | 0.18 V           | 0.25 V | N/A             | N/A | 0.92 ns          | 1.46 ns          | 1.69 ns | 1.59 ns          | 1.87 ns |   |

| PP_A<4>          | 0.18 V               |                 | Output to csv <sub>N</sub> | 010 0.233 01    | 040 V            | 0.20 V | N/A             | N/A | 0.90 ns          | 1.44 ns          | 1.65 ns | 1.63 ns          | 1.83 ns |   |

| PP_A<5>          | 0.21 V               | cds_in_gen_cpow | cus_ur_yen_chas            | 0101, 0.233 Gbp | 0.21 V           | 0.30 V | N/A             | N/A | 0.91 ns          | 1.45 ns          | 1.68 ns | 1.58 ns          | 1.87 ns |   |

| PP_A<6>          | 0.20 V               |                 |                            | 0101, 0.233 Gbp | 0.20 V           | 0.28 V | N/A             | N/A | 0.91 ns          | 1.45 ns          | 1.68 ns | 1.59 ns          | 1.86 ns |   |

| PP_A<7>          | 0.20 V               | cds_in_gen_2p5  | cds_bi_gen_2p5             | 0101, 0.233 Gbp | 0.20 V           | 0.25 V | N/A             | N/A | 0.90 ns          | 1.44 ns          | 1.66 ns | 1.61 ns          | 1.84 ns |   |

| PP_A<8>          | 0.21 V               | cds_in_gen_2p5  | cds_bi_gen_2p5             | 0101, 0.233 Gbp | 0.21 V           | 0.28 V | N/A             | N/A | 0.91 ns          | 1.45 ns          | 1.68 ns | 1.58 ns          | 1.86 ns |   |

| PP A<9>          | 0.19 V               | cds in gen 2p5  | cds bi gen 2p5             | 0101, 0.233 Gbp | 0.19 V           | 0.25 V | N/A             | N/A | 0.91 ns          | 1.44 ns          | 1.66 ns | 1.60 ns          | 1.84 ns | 4 |

## Simulation Support for Unrouted Nets

▶ Partially routed and unrouted signal nets are automatically modeled with transmission line models based on ratsnest, user-defined parameters, and Manhattan distances

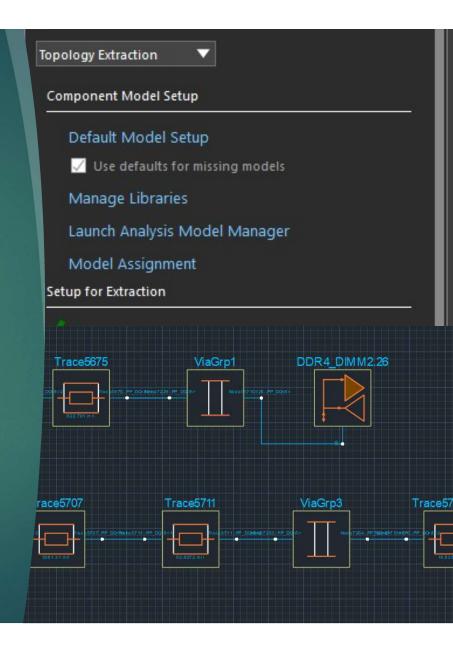

## Topology Extraction

(Topology Workbench)

- Integrated workflow in Sigrity™ Aurora

- Extract single-ended and differential signals into Topology Explorer

- Explore what-if scenarios and develop constraints

- Stand alone tool or embedded into AllegroX environment.