## FreeRange Digital Design Foundation Modeling

# Lab Activity Manual

©copyright 2019 by james mealy v4.00

## **Table of Contents**

| Table of C | Contents                                                     | 2 -  |

|------------|--------------------------------------------------------------|------|

| Lab Activ  | ity Report Guidelines                                        | 3 -  |

| Lab Work   | Submission Guidelines                                        | 5 -  |

| Note on A  | ny Lab Activity Submission                                   | 7 -  |

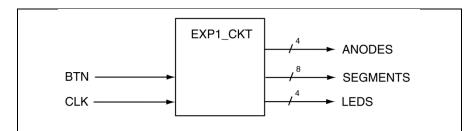

| Exp 1:     | Half Adder (HA) & Full Adder (FA): Standard SOP Form         | 8 -  |

| Exp 2:     | Half Adder (HA) & Full Adder (FA): Standard POS Form         | 10 - |

| Exp 3:     | 5-Bit Ripple Carry Adder (RCA)                               | 12 - |

| Exp 4:     | BCD-to-Seven-Segment Decoder                                 |      |

| Exp 5:     | 8-Bit Comparator with 4-Bit Comparator Modules               | 17 - |

| Exp 6:     | Five-Bit Magnitude Comparator                                |      |

| Exp 7:     | Signed Binary 5-Bit Adder/Subtractor with Validity Detection |      |

| Exp 8:     | Basic FSM Design: Multi Output 4-Bit Up/Down Counter         |      |

| Exp 9:     | 4-Bit Up/Down Counter w/ Multiplexed 7-Segment Display       | 31 - |

| Exp 10:    | Full-Feature 3-Bit Up/Down Counter                           | 33 - |

| Exp 11:    | Sequence Detector FSMs                                       |      |

| Exp 12:    | Four 4-Bit Number Sort                                       | 38 - |

| Exp 13:    | Serial Parity Generator                                      |      |

| Exp 14:    | FSM-Based 5-Bit Multiplier                                   | 43 - |

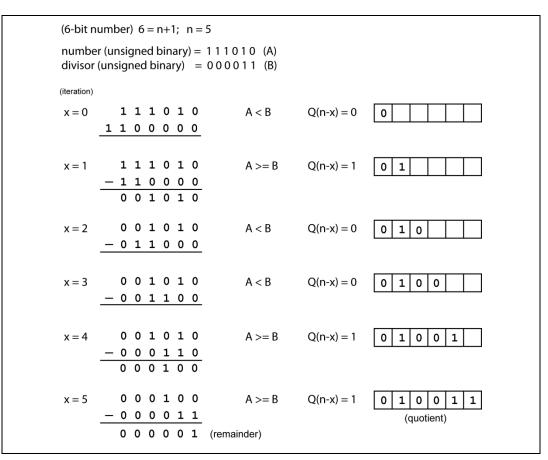

| Exp 15:    | FSM-Based 6-Bit Divider                                      | 46 - |

| Exp 16:    | RAM/ROM Bubble Sort                                          |      |

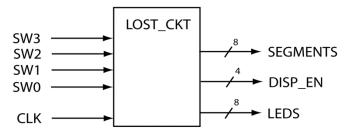

| Exp 17:    | Lost HDL Model Analysis and Synthesis                        |      |

| Exp 18:    | Static Logic Hazards (B2Spice Simulator)                     |      |

| Troublesh  | ooter's Guide to Vivado                                      | 57 - |

|            | Golden Rules                                                 |      |

| XDC Fi     | le Issues                                                    | 57 - |

|            | Quirks and Common Errors                                     |      |

| Lab Gradi  | ng Acronyms                                                  | 58 - |

| Verilog St | yle File                                                     | 59 - |

| Verilog Te | estbenches                                                   | 60 - |

## Lab Activity Report Guidelines

Lab reports provide a description of your work in the lab. There are two basic forms of information in the lab report: an objective portion and a subjective portion. The objective portion of the lab report documents what you did in the lab (designed stuff, took data points, etc.) while the subjective portion provides your interpretation of the results you obtained during the lab (namely the conclusion).

Each instructor has their own set of rules and expectations regarding lab reports. Generally speaking, lab reports are graded on how well you follow those rules and meet those expectations. The goal of the following comments is to help you generate a quality lab report while minimizing the amount of time you spend writing the report. Please do not hesitate to ask questions. Lab write-ups are not exams so feel free to ask me to look over your report before you submit it.

#### **General Rules:**

- Lab reports should be written using a word processor and submitted in hard copy form.

- Each lab group should submit one lab report. Each member of the lab group should write their own conclusion independently from other group members and submit it with the lab report.

- Reports should not have a title page. The lab activity title should be boldly centered on the first page. The course and section number, and the names of group members should also appear on the first page.

- Wording in the lab report should be brief but concise. Longer lab reports rarely correlate to higher quality lab reports. Moreover, using concise wording save you time writing the report and saves someone else time reading it.

- Wording in the lab report should use "good English" and appropriate technical style. Correct spelling, appropriate use of technical terms, and appropriate technical style allows you to create a professional document that highlights your lab activities. If you are new to technical report writing, strongly consider having someone else read over your report before you submit it. There are also many features in MS Word that can help you with the grammar.

- Lab reports should be neat and intelligently organized. Hand-written and hand-drawn items such as circuit diagrams should be neat (use appropriate drawing software if necessary).

- All figures and diagrams should contain captions and/or titles and should be referenced directly from the body of the report (do not say things like "in the figure below"). Plan on using the cross-referencing feature of your word processor (ask someone if you don't know how to use it).

- Different sections and diagrams in the lab report should be well delineated from each other. Using extra space to in the lab report generally creates a more professional looking document.

#### **Report Format:**

Each lab report should at least contain the following clearly indicated sections. More sections are permissible but the document should remain concise and well organized.

• <u>Objectives (Say why you're bothering)</u>: This section states that point of performing the lab activity. This section is generally a rewording of the stated activities objectives in such a way as to show that understood what you're attempting to do with in the lab activity. Don't just copy the state lab activity's objectives; use your own words instead.

- <u>**Procedures** (Say what you did)</u>: Describe what you did during the lab activity.

- The use of words in this section should be minimized in favor of more expressive items such as truth tables, equations, circuit diagrams, block diagrams, timing diagrams.

- Someone should be able to read though this section and know exactly where you started, where you ended, and the steps you used to arrive at your destination. The flow of this section should match the flow of tasks during the lab activity. This section should not depend on the description of the lab. In other words, assume that the person reading your lab report does not have a copy of the lab description.

- This section should be written using normal English sentences and paragraphs as opposed to bulleted or numbered lists of tasks and/or commands.

- <u>**Testing** (Say why you think you did it correctly)</u>: Describe the testing procedures you used to verify your circuitry met the design criteria.

- <u>Conclusion (Sum up the experience)</u>: See comments below.

- <u>Questions (Say what you're supposed to say)</u>: Be sure to include the answers to any questions that may appear at the end of lab activity description in your lab report.

- Answer the questions in such a way as to re-state the original question.

- If the question requires that you perform some non-trivial calculations, include those with the lab report.

#### The Conclusion:

- Conclusions should contain the following information:

- A brief description of what was done in the lab activity (2-3 sentences).

- Wording that implies you understand the concepts presented in the lab activity.

- Wording that describes how the lab activity relates to other lab activities and/or topics discussed in lecture or in the world in general.

- Wording that indicates the objectives of the lab activity were met. Don't simply state that the lab activity's objectives were met; support the assertion indirectly with your wording.

- Conclusions should *not* contain the following:

- Detailed descriptions of the procedure followed during the lab activity.

- Detailed descriptions of the circuits designed or used during the lab activity.

- Comments regarding whether you liked the lab activity or not.

- Comments regarding how much you learned during the lab activity.

- Comments that state directly that the lab activity's objectives were met.

### Lab Work Submission Guidelines

This document contains the guidelines of how your submitted lab work ("lab work" is different from a lab report) documentation should appear. Adhering to these guidelines strongly indicate that you put the time and effort into understanding the lab material. Moreover, properly formatted submissions are easier to verify that your work is correct. Because the EE Department bean counters continue to overschedule the digital labs, you need to submit quality reports. You can find more formatting-related information in the appropriate HDL Style File and RAT Assembly Style File documents (CPE 233). Most importantly, if you have questions, ask your instructor before you submit sub-par work.

#### The Guiding Question: Would I submit this work to my supervisor?

If the answer is no, then consider quality improvements before submission.

#### Submission Ordering:

- 1) Cover sheet with course names & sections, group member names, executive summary of experiment

- 2) Diagrams (schematics, state diagrams, etc. from experiment assignment)

- 3) Source code (Verilog, VHDL, assembly code, etc. from experiment assignment)

- 4) Answers to question set (include question with answer)

- 5) Design Problem solutions (if any: HW & SW problems: code and/or diagrams)

#### **General Comments:**

- Only submit one lab submission per lab group, unless directed otherwise

- Lab reports should be stapled high in the upper-upper-left corner

- Lab work submissions should be "stand alone", which means that anyone can pick up the submission and know what they're looking at. This means:

- All problem-type questions include the problem statement in an appropriate location

- Answers to questions should include the question

- Your writing need to be terse and concise. Save the verbosity and schmooze for other courses where lazy professors don't read your work or have student graders do their work for them.

- Lab submissions should be neat; use whitespace make submissions neat, organized, and readable

- All diagrams (timing, state, circuit diagrams, etc.) should include a title and/or caption

- Do not break tables or diagrams across pages

- Use hex notation for all signal values wider than four bits

- Use engineering notation for all numbers

- Do not put source code in the body of a report; attach it to the back of report instead

- Do not include source code for anything you did not write

#### Lab Activity Questions:

- Include the question you're answering before you write the answer to the question

- Use white-space to delineate questions and answers to make them more readable

#### Hardware (Schematic) Diagrams:

- Must be neat; can be hand drawn or drawn using drawing program

- Do not route control and status signals to and from FSMs, but clearly label both ends of signals

- Do not route clock signals, but clearly label at clock inputs and outputs

- Do not use "hump notation"

#### Simulator Printouts:

- Timing diagrams should be annotated (handwritten is fine, but must be neat)

- Timing diagrams should be outputs from the simulator and never cut-and-paste screen shots

- Timing diagrams should primarily include the "things of interest" by using the correct amount of magnification

- Timing diagram annotations should generally show the causality of signals changes and/or values

#### FSM State Diagrams:

- State diagrams can be handwritten but must be neat

- FSM state bubbles should have symbolic names that roughly indicate purpose of state

- FSM input and output signals should have symbolic names that roughly indicate their purpose

- FSM states should only list outputs that are critical to that state; do not include output signals associated with a state if they are a "don't care" relative to that state

- State diagrams should include legends indicating inputs, output, and state name

#### General Source Code (HDL Assembly)

- Each separate file of code should begin on a new page

- Source code files should have header that include names of group member, lab activity number, and a brief but complete description of the file's content

- Never use the tab key for any reason when writing source code

- Use "courier new" font for all submitted source code (VHDL, Verilog, assembly, C, etc.)

- Each file of code should have header describing what the code does and who wrote the code

- Do not allow lines of source code to wrap

- Code should be properly indented (see appropriate style files)

- Code should use white space to increase readability of code

- Code should be sufficiently commented

- Code should use self-commenting labels (labels, signal, variable, entity, architecture names, directives, constants, etc.)

- Code should make no more than one assignment per line

- Code should be printed using separate files and included with report

#### HDL Source Code Specific:

- Code should define only one item (signal, variable, etc.) per line

- Code should use "s\_", "v\_", or "r\_" prefix for signals, variable, or registers, respectively

- Structural models use direct mapping only

- Code should declare no more than one variable per line (entities & declarations)

#### RAT Assembly Source Code Specific (CPE 233 only):

- All subroutines should have proper headers describing what the subroutine does which registers are permanently modified by the subroutine

- All instructions & directives, the left-most instruction operands, and comments should be aligned

As indicated in the lab activity reporting guidelines, there is some stuff you must always place in your lab reports. In case you didn't really read those guidelines, a short list of this stuff includes the following. Keep in mind that you every report should also include sections of Objective, Procedures, Testing, and Conclusion.

- Boolean equations you may have used in the lab activity

- Derivations you may have needed to do in the lab activity

- Any non-trivial calculation you performed in order to complete the lab activity

- All source code (HDL and/or assembly language) generated in the lab activity: properly formatted, well commented and with a really nice header

- All pertinent timing diagrams from the lab activity

- All circuit diagrams from the lab activity

- Any state diagram used in the lab activity

- Questions and their answers that appear at the end of the lab activity

- Solutions to any design problems that are part of the lab activity

- To be exposed to the Xilinx Design Methodology

- To design, implement, and two arithmetic-based digital circuits

- To obtain an introduction to Verilog

- To get a feel for instructor expectations for each experiment procedures and write-ups

<u>Somewhat Meaningful Comments:</u> Designing circuits that perform arithmetic operations is one of the more common pursuits in digital design-land. The half adder (HA) and full adder (FA) are probably the most basic digital circuits that just about everyone who is anyone must design at one time or another in their digital design careers. Both of these circuits are known as 1-bit adders; they only differ in that the FA has a carry-in input while the HA does not. The outputs of both circuits are the same: the SUM output indicates the result of the addition operation while the carry-out (CO) indicates whether the operation generates a carry (CO).

This experiment is primarily an introduction to both the Xilinx Design Methodology as it pertains to the Vivado software, and Verilog. This experiment has you design and implement two arithmetic circuits on the development boards. You'll find every lab instructor has different expectations of proper lab "conduct" and subsequent lab write-ups, thus this experiment also gives you an idea of what the instructor expects in both of these areas.

<u>Assignment: Part A:</u> Design a half adder and implement your design on the development board. Table 1 shows the input and output assignment for the devices on the development board. Use standard SOP form for you implementation.

| Inj              | out                        | Output        |                |  |

|------------------|----------------------------|---------------|----------------|--|

| OP_A OP_B        |                            | SUM           | СО             |  |

| left-most switch | second switch<br>from left | left-most LED | right-most LED |  |

Table 1: Input/Output (I/O) specification for the HA

<u>Assignment: Part B:</u> Design a full adder and implement your design on the development board. Table 2 shows the input and output assignment for the devices on the development board. Use standard SOP form for you implementation.

|                   | Input                       | Output                     |               |                |

|-------------------|-----------------------------|----------------------------|---------------|----------------|

| OP_A              | OP_B                        | Cin                        | SUM           | СО             |

| right-most switch | second switch<br>from right | third switch from<br>right | left-most LED | right-most LED |

Table 2: Input/Output (I/O) specification for the FA

#### Special Deliverables:

None

#### **Questions:**

- 1. In your own words, what is meant by the term "methodology".

- 2. Briefly describe the purpose of the "constraints file", which is another name for the file with the ".xdc" extension.

- 3. Briefly describe what you're doing when you "synthesize" your HDL model.

- 4. There is a programmable logic device (PLD) on the development board used for this class. What particular type of PLD is on the dev board?

- 5. How many assignment statements did you use in your HDL model for the HA and FA?

- 6. Briefly describe the basic limitation of the HA (relative to the FA) in the context of a mathematical digital circuit.

- 7. Briefly described how you verified your circuit in this experiment was working properly.

- 8. Briefly describe the main purpose of a "gate" in the context of this course.

#### **Design Problems:**

1. Design a 1-bit subtractor. This circuit has two inputs (A, B) and two outputs (SUB for the subtraction result of A -B, Bo for a "borrow" where appropriate). For this problem, show the equations for the outputs in standard SOP form.

#### **Deliverables:**

This section describes the special deliverables. This is the only experiment that lists all of the deliverables; see the list in the "Lab Work Submission Guidelines".

- 1. Top-level black-box models for all circuits

- 2. Lower-level circuit diagrams for all circuits

- 3. Tables and Equations associated with circuits

- 4. HDL source code for all circuit models

- To be exposed to the Xilinx Design Methodology

- To gain more experience working with Xilinx design environment

- To demonstrate functional equivalence of SOP and POS forms

**Somewhat Meaningful Comments:** This experiment entails the design of two circuits you previously designed: the HA &FA. In this experiment, we'll demonstrate the notion of *functional equivalence* by designing these same two circuits using a different but equivalent form of Boolean equations, namely the standard POS form.

<u>Assignment: Part A:</u> Design a half adder and implement your design on the development board. Table 3 shows the input and output assignment for the devices on the development board. The output of your circuit should show both standard SOP and POS forms both the SUM and CO signals.

| Input               |                         |                | Outp                          | ut                             |                |

|---------------------|-------------------------|----------------|-------------------------------|--------------------------------|----------------|

| OP_A                | OP_B                    | SUM_SOP        | CO_SOP                        | SUM_POS                        | CO_POS         |

| left-most<br>switch | second switch from left | left-most LEDs | second from left-<br>most LED | second from right-<br>most LED | right-most LED |

| Table 3: Input/Output (I/O) | specification for the HA |

|-----------------------------|--------------------------|

|-----------------------------|--------------------------|

<u>Assignment: Part B:</u> Design a full adder and implement your design on the development board. Table 4 shows the input and output assignment for the devices on the development board. The output of your circuit should show both standard SOP and POS forms both the SUM and CO signals.

| Input                      |                          |                      | Output            |                              |                               |                   |

|----------------------------|--------------------------|----------------------|-------------------|------------------------------|-------------------------------|-------------------|

| Cin                        | OP_A                     | OP_B                 | CO_SOP            | SUM_SOP                      | CO_POS                        | SUM_POS           |

| third switch<br>from right | second switch from right | right-most<br>switch | left-most<br>LEDs | second from<br>left-most LED | second from<br>right-most LED | right-most<br>LED |

#### Table 4: Input/Output (I/O) specification for the FA

#### Special Deliverables:

• none

#### **Questions:**

- 1. Since you now know there are many ways to implement digital circuits, describe some possible parameters involved in ascertaining the "best" way.

- 2. Briefly comment on which form (SOP or POS) of the HA &FA was easier to design and implement. Provide a brief justification for your answer.

- 3. Briefly describe how the full adder is somewhat limited in doing math operations.

- 4. Briefly describe how you could configure the two full adders to become a two-bit adder.

- 5. Generate a table the compares the number of AND gates, OR gates, and inverters to implement the FA in both SOP and POS forms. Show your equations for this problem, meaning you should have a total of four equations. Draw the final circuit for these two functions also.

- 6. Briefly described how you verified your circuit in this experiment was working properly.

- 7. Write a "conclusion" for this experiment. Note that a conclusion describes what the point of the experiment was.

#### **Design Problems:**

- 1. Design a 2-bit "modulo-2" adder. This adder has two 2-bit inputs and one 2-bit output. The output of each individual bit is "0" when adding 0+0 and 1+1; otherwise the output is "1". Show only a truth table for this design. Be sure to include a black box diagram for your solution.

- 2. How would you use the circuit (not necessarily a single circuit) from the previous problem to create an 8-bit modulo-2 adder. Be sure to include a black box diagram for your solution at both a high-level and the "next lower level".

- To use a HDL structural model to support notion of hierarchical digital design

- To use HDL structural model to support the notion of modular design and code reuse in HDL

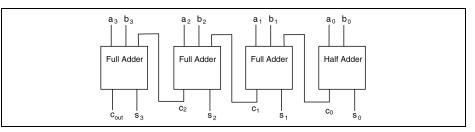

**Somewhat Meaningful Comments:** Arithmetic circuits are massively common out there in digital designland. One of the most basic and useful circuits the Ripple Carry Adder (RCA). For the purpose of this activity, the RCA comprises of a HA for the LSB and FAs for all the other bits. Figure 1 shows a schematic diagram of a 4-bit RCA.

Figure 1: Schematic diagram for a 4-bit Ripple Carry Adder (RCA).

**Assignment:** Using your previous half adder and full adder modules, design a 5-bit RCA, similar to the 4-bit RCA shown in Figure 1. Implement your RCA on the development board using the pin assignments in Table 5. Additionally:

- Use HDL structural modeling for your implementation using both the HA and FA models you previously designed.

- Use bundle notation in your HDL code wherever possible.

| Inp                                        | uts                                      | Outputs                                  |                 |  |

|--------------------------------------------|------------------------------------------|------------------------------------------|-----------------|--|

| A B                                        |                                          | SUM                                      | Carry-out       |  |

| a <sub>4</sub> -a <sub>0</sub> : SW15-SW11 | b <sub>4</sub> -b <sub>0</sub> : SW4-SW0 | s <sub>4</sub> -s <sub>0</sub> : LD4-LD0 | $C_{out} = LD7$ |  |

#### Table 5: Pin assignments for the RCA.

#### **Deliverables:**

- 1. HDL models for all modules you wrote in this lab activity. This experiment is a hierarchical design, so include both the higher and lower-level modules.

- 2. Black-box models for the circuits you modeled in this lab activity

- 3. Answers to the "questions"

- 4. Solution for design problems

#### **Questions:**

- 1. Briefly describe the two main attributes of modern digital design.

- 2. Briefly describe why is it a good idea to avoid modifying previously designed modules in your new design?

- 3. In your own words, briefly but completely explain why we refer to the circuit in this lab activity to as a "ripple carry adder".

- 4. If you needed to extend the RCA from this lab activity to a 10-bit RCA by using a structural model with two 5-bit RCAs, what changes would you need to apply to the 5-bit RCA?

- 5. How many rows were there be in a truth table for a 32-bit RCA? Would it be feasible to design a 32-bit RCA using a truth table?

- 6. How many logic gates would it require to implement the 5-bit RCA using discrete logic? For this problem assume the logic is in standard SOP and the LSB uses a HA.

- 7. Write a formula in closed for that describes the number of gates in a RCA as a function of the bitwidth of the RCA. Recall that the LSB of the RCA is a HA. For this question, assume the FA and HA are in reduced form (not in standard SOP form). Feel free to ask the instructor for the "reduced" form of both the HA and FA.

- 8. For a RCA, the result could be available immediately, or the result could be delayed. Describe a case where the result is available immediately and also describe a case where the delay is the "worst case". State how long the worst case is in terms of "gate delays".

- 9. Briefly describe the notion of concurrency in digital circuit design.

- 10. Do the various module instantiations in a HDL model operate in a concurrent manner? Briefly explain why or why not.

- 11. Consider two different HDL models that are functionally equivalent; in particular, they are mostly the same except for the notion that one used structural modeling and the other implemented a similar set of modules but did not use structural modeling. Would expect the synthesized circuit based on these models to use the equivalent amount of resources or will one approach use more or less resources. Support your answer with intelligent commentary.

#### **Design Problems:**

Design a circuit that adds four 10-bit unsigned binary values and outputs an unsigned binary 10-bit result. The circuit also has a VALID output that indicates when the 10-bit unsigned binary result is valid. Note that when you add two 10-bit numbers, you will generate a 11-bit result (in some cases). Show the top two levels for this solution, meaning a top-level BBD, and the next lower level which is RCAs and some gates. There is no need to show the next lower level, which would be the gate-level view of the RCAs. State how the circuit is controlled.

## Exp 4: BCD-to-Seven-Segment Decoder

#### **Objectives:**

- To design the circuitry to drive an external 7-segment display.

- To design, implement, and test three digital circuits

#### Somewhat Meaningful Comments:

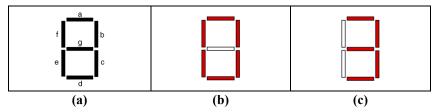

The 7-segment display is one of the most common display devices in the universe; we generally use these devices to display decimal numbers. These devices as also capable of displaying the full gamut of hex numbers (although the case of the alpha characters is not consistent). The 7-segment displays on the development board consist of seven LEDs (light emitting diodes). There are actually eight LEDs, one is for a decimal point. The LEDs are the small button-like colored devices that light up occasionally during your experimentation. The LEDs in this lab activity were elongated by using small stretching racks and configured in such a manner as to easily represent decimal numbers.

The LED is a two-terminal polarity-sensitive device that turns-on when the voltage conditions across the two terminals are at the correct levels. We refer to the two LED terminals as the *anode* and the *cathode*. To make the LED emit light, the anode must be have a 0.7V higher potential than the cathode. What this means to you in digital design-land is that you must either provide the LED with a '1' or a '0' depending on how the LED is wired in the circuit. To find out exactly how the LED works on your dev board, read the specification of the development board (RTFM).

We represent individual decimal numbers by turning on specific sets of the segments. Referencing the seven segments is done by assigning unique letters to each of the segments. Figure 2(a) shows the most common listing of these segments is. Figure 2(b) shows a 7-segment display creating the illusion of a '0' by lighting all the segments except segment 'g'. Figure 2 (c) shows segments a, b, c, d, and g lit to simulate the number '3'. Once again, there are two types of 7-segment displays and two ways to connect ways to control the anodes associated with the 7-segment displays. Every development board uses different parts and wires them as required. Check the dev board's user's manual.

Most importantly, making an LED emit light is a two-step process on a 7-segment display. You need to both turn-on the LED and also actuate the individual 7-segment display. Both of these actuation steps involve sending a logical '1' or '0' to the device. Consult the reference manual for the development board for the details (and then ask a bunch of questions).

Figure 2: The amazing 7-segment display (a), and '0' (b), and a '3' (c).

Assignment: Design a BCD to 7-segment decoder using an HDL to model the circuit.

- The 4-bit input of this circuit is a BCD number. The eight outputs are the various segments of the display (including the decimal point). Use all the seven-segment displays and make them selectable using one switch for each display.

- When the input BCD value exceeds the range of decimal digits, turn off the display. Table 6 lists the input and output assignments for you development board.

- Connect the four anodes to the four left-most switches. The switches in the UP position generate a logic '1'. See Table 7 for even more details.

- Verify your design works properly visually using the pin assignments in Table 6. Choose your test vectors such that you test the major functionality of your circuit, but fit the entire simulation onto one page.

| Input                    | Output                       |  |

|--------------------------|------------------------------|--|

| SW3,SW2,SW1,SW0          | CA,CB,CC,CD,CE,CF,CG,CDP     |  |

| four right-most switches | right-most 7-segment display |  |

Table 6: Input/Output specification for the BCD to 7-Segment decoder.

| Input                    | Output                       |  |

|--------------------------|------------------------------|--|

| SW15, SW14, SW13, SW12   | AN3, AN2, AN1, AN0           |  |

| four right-most switches | right-most 7-segment display |  |

#### Table 7: Input/Output specification for the anodes.

#### Special Deliverables:

• none

#### Questions:

- 1. If you were not able to use a decoder in this experiment, who many concurrent signal assignments would you have needed to implement the segments portion of the seven segment display? Briefly explain.

- 2. Draw a black box diagram showing the anodes, LEDs, segments, switches, and buttons on the development board. Be sure to carefully labeled inputs and outputs on your diagram.

- 3. Similar to 7-segment displays, there are also 14-segment displays out there in the real world. Briefly describe the main purposed served by 14-segment displays.

- 4. This lab activity required that you use a generic decoder. You could have modeled this decoder using one of two possible types of procedural blocks. Provide the code for a generic decoder using one of the statements you did not use in this lab activity.

- 5. One of the important design approaches in modeling digital circuits is to use a LUT (decoder) whenever possible. Briefly describe why this is a good approach.

- 6. How can a the set of seven segment displays ever display a number such as "3948" if you can only ever display one number at a time on the set of displays?

7. A four-digit seven-segment display has 32 LEDs, which seems to indicate we needs 32 outputs to control it. But... a four-digit seven-segment display is typically driven by 12 signals. Briefly explain the main reason this is done.

#### **Design Problems:**

1. Non-standard decoders are essentially LUTs. As you know from computer programming, often times using a LUT for calculations is a great idea. For this problem, show the BBD and code for a 4-input decoder that outputs the square of the input. Consider both input and output to be unsigned binary numbers. Use as few signals for the output as possible but still be able to represent the largest possible value for the output.

#### **Deliverables:**

- 1. HDL models for all modules you wrote in this lab activity

- 2. Black-box models for the circuits you modeled in this lab activity

- 3. Answers to the "questions"

- 4. Solution for design problems

- To design and implement one of the basic digital logic circuits

- To discover the power of HDL behavioral modeling

- To gain more experience and practice with structural modeling

- To write a HDL testbench to simulate your circuit

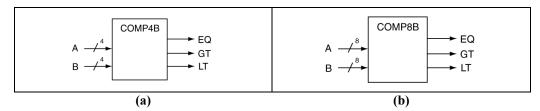

**Somewhat Meaningful Comments:** This lab activity introduces the notion of HDL behavioral modeling in the context of n-bit comparators. While you'll quickly find that a designing a simple comparator is no big deal using behavioral modeling, this lab activity becomes more meaningful by asking you to connect two 4-bit comparators in such a way as to form a single 8-bit comparator. While it would be easier to model an 8-bit comparator directly, using two 4-bit comparators builds character and provides practice with structural modeling and general digital design concepts.

Simulating your HDL models is massively important for two reasons. First, it allows you to verify your circuit is operating properly before you actually implement the circuit. Secondly, it provides a way to debug your circuit if your circuit does not work.

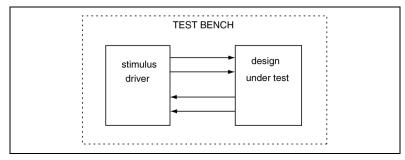

The notion of simulating in HDL is a matter of generating a "testbench". The testbench is simply a special form of a HDL module; it's only function is to provide "stimulus" to the circuit you design (feed the inputs with a meaningful signal). We generally refer to this stimulus as "test vectors". You the circuit designer are responsible for generating what you feel are enough test vectors to give you the warm and fuzzy notion that your circuit is operating properly. Once again, you the designer will be asked if your circuit works; you base your answer on how well you tested your circuit. In a perfect world, you would spend a lifetime testing your circuit; in reality, you're only going to have time to test a reasonable portion of your circuit, and then you need to justify why your limited test vectors prove your circuit is working. Be sure to check out the appendix for the full smear of comments on testbenches.

<u>Assignment: Part A</u> Design an 8-bit comparator using two 4-bit comparator modules. Figure 3 shows the two high-level black box diagrams for this lab activity. Figure 3(a) shows the 4-bit comparator module you'll use to build the 8-bit comparator module in Figure 3(b). The inputs to 8-bit comparator are both 8-bit unsigned numbers.

- Use the provided n-bit comparator model in you design

- Implement your design on the dev board using the 16 switches as inputs (A & B) and three LED as outputs (EQ, GT, LT).

- Simulate your design using a testbench. Annotate your simulation output to draw the reader's eyes to what you are testing.

- Your final black box diagram will have three modules: two 4-bit comparator modules and an extra "logic" module. Implement the logic module as a behavioral model.

- Use only two files for this design: one for the n-bit comparator module and one for the top-level module that contains the two 4-bit comparator instantiations and the behavioral model for the extra logic referenced in the previous bullet.

Figure 3: Black box diagrams for this lab activity: the underlying component comparator (a), and the final top-level BBD (b).

**Assignment: Part B** Write a testbench and simulate your comparator model using the development environment's simulator. Use the provided cheatsheet for a guide. Once you have your waveforms displayed on the screen, call over the instructor of a TA and ask them to show you the "important stuff".

- Choose your testbench test vectors such that you adequately test the major functionality of your circuit, but fit the entire simulation onto one page.

- Print out then annotate the resulting timing diagram (hand annotations is fine)

- Use hexadecimal for all bundled input and output signals.

#### **Constraints:**

- Minimize your use of hardware in your design

- Use a procedural block (an **always** block) for the "logic" portion of your design

#### **Deliverables:**

- 1. HDL models for all modules you wrote in this lab activity

- 2. Black-box models for the circuits you modeled in this lab activity

- 3. Answers to the "questions"

- 4. Solution for design problems

- 5. Well annotated waveforms from the simulator.

#### **Questions:**

- 1. Briefly describe whether you could have used a decoder for the "logic box" portion of this lab? Also, provide a justification as to why you would not and/or did not use a decoder for this part of the circuit.

- 2. In your own words, briefly describe the advantage(s) of using a behavioral model as opposed to a gate-level implementation of the comparator.

- 3. Based on the previous question, you probably see that modeling comparators of any size is no big deal using an HDL. Why then did this lab activity ask that you model a larger comparator using two smaller comparators?

- 4. We all know that the well-known hallmark of a comparator is that it uses EXOR-type gates in its implementation. Does the development board you're using actually use EXOR-type gates in your design? Briefly but completely explain.

- 5. The **always** block is one of Verilog's concurrent statements. But, the **always** block contains only sequential statements in the body of the always block. Describe how this seemingly oxymoron is actually possible.

- 6. The **always** block contains a "sensitivity list". Briefly describe what this is. Also, state what you should generally place in the sensitivity list.

- 7. In your own words, what is a test vector and what entity generates the vectors for your testbench in this experiment?

- 8. Briefly explain what it would mean if the output of your simulation did not match the outputs on hardware for the same inputs?

- 9. Humans primarily use decimal while computer hardware uses binary. Briefly explain what the point of having hexadecimal in the fray also.

- 10. We often use hexadecimal notation in digital-land. Can you use hex notation to represent signed binary numbers in RC format? Briefly explain.

#### **Design Problems:**

Design a circuit that has four 10-bit unsigned binary inputs A, B, C, D. The output of the circuit has the same three outputs as a normal comparator. If the sum of A+C is valid (10-bit result) and the sum of B+D is value (10-bit result), then the output of the circuit reflects the result the comparison of A+C & B+D. If either addition operation generates a carry, all of the three circuit outputs (EQ, LT, & GT) should be zero. Don't use any MUXes in your solution. Draw the BBD for this circuit as well as the lower-level schematic. Minimize your use of hardware in your design.

## Exp 6: Five-Bit Magnitude Comparator

#### **Objectives:**

- To gain more skills using standard digital devices, block-level design, and structural modeling

- To gain yet more experience designing and using arithmetic circuits

**Somewhat Meaningful Comments:** Arithmetic circuits are massively important in digital design. Understanding the meaning of binary number representations is one of the keys to being able to design and implement arithmetic circuits that deal with binary numbers. This lab activity provides you with more experience in several of the main areas associated the design and implementation of digital circuits. This circuit is somewhat complicated; you'll need to start out with a block diagram to map out your design before you start writing HDL models.

**Assignment:** Design and implement a 5-bit magnitude comparator on the development board. This circuit inputs two 5-bit RC values (RC format) and displays information about these two values according the description that follows.

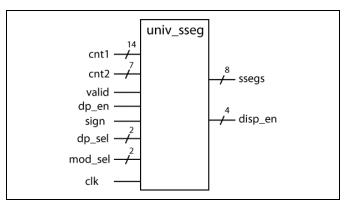

- Use the provided univ\_sseg.v module to drive the 7-segment display with the required output values.

- Use the left-most and right-most switches to represent the two 5-bit signed binary inputs, where the sign-bit should always be the left-most bit of the input.

- If the magnitudes are not equivalent, have the 7-segment display show all dashes (be sure to read the header of the univ\_sseg.v module).

- If the magnitudes are equivalent and the numbers are equivalent, display the input value; otherwise, display the magnitude.

#### **Constraints:**

• Minimize your use of hardware in your design.

#### Hints:

- Use the provided RCA in this design; instantiate appropriately for this experiment

- You don't need to implement this entire design using structural modeling.

- This is your first experiment that includes a clock input. This means that your top-level module contains a clock input. You then connect this input to the clk input on the univ\_sseg module. Keep in mind that the development board provides the clock signal to the FPGA. The clk is a true input, which means you must uncomment the clock oriented lines in the constraints file.

#### The univ sseg.v Module:

The module is provided for you; you can find the instructions for using the device by reading the instructional notes in the module's header. Figure 4 show the black box diagram for the univ\_sseg.v module.

Figure 4: univ\_sseg.v black box diagram.

| Signal Name                                                                                                                                                                                                                                                | Mode | Description                                                                                                                                                                                                                                                                                                                                                                                   |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| cnt1 in                                                                                                                                                                                                                                                    |      | <ul> <li>This is a 14-bit unsigned binary input that operates differently for different modes.</li> <li>mod_sel = 00: lower 8-bits used for [0,255]</li> <li>mod_sel = 01: lower 7-bits used for [0,99]</li> <li>mod_sel = 10: lower 14-bits used for [0,9999]</li> </ul>                                                                                                                     |  |

| cnt2                                                                                                                                                                                                                                                       | in   | This is a 7-bit input used in $mod_sel = 01 [0,99]$                                                                                                                                                                                                                                                                                                                                           |  |

| valid                                                                                                                                                                                                                                                      | in   | If this input is a '0', all the displays show a '-'; otherwise the display acts according to other selections.                                                                                                                                                                                                                                                                                |  |

| sign                                                                                                                                                                                                                                                       | in   | If this input is a '1', all the displays show a '-'(minus sign) in mod_sel = 00.                                                                                                                                                                                                                                                                                                              |  |

| dp_en                                                                                                                                                                                                                                                      | in   | This is input turns on a decimal point according to the <b>dp_sel</b> input.                                                                                                                                                                                                                                                                                                                  |  |

| dp_sel                                                                                                                                                                                                                                                     | in   | <ul> <li>This input controls decimal point display; the dp_en input must be on for this input to work. Only one decimal point can be active at any time.</li> <li>00: dp displayed on right-most 7-seg display</li> <li>01: dp displayed on middle-right 7-seg display</li> <li>10: dp displayed on middle-left 7-seg display</li> <li>11: dp displayed on left-most 7-seg display</li> </ul> |  |

| mod_selInThis input selects the display mode:<br>00: displays one count [0,255] with optional '-' signmod_selIn01: displays two counts [0,99] (no sign)<br>• 10: displays one count [0,9999] (no sign)<br>• 11: displays average academic administrator IQ |      | <ul> <li>00: displays one count [0,255] with optional '-' sign</li> <li>01: displays two counts [0,99] (no sign)</li> <li>10: displays one count [0,9999] (no sign)</li> </ul>                                                                                                                                                                                                                |  |

| ssegs                                                                                                                                                                                                                                                      | out  | These are the $a \rightarrow dp$ outputs for the 7-segment displays. These are officially the cathodes.                                                                                                                                                                                                                                                                                       |  |

| disp_en                                                                                                                                                                                                                                                    | out  | These are the anodes for the 7-segment display.                                                                                                                                                                                                                                                                                                                                               |  |

#### Table 8: Brief description of univ\_sseg.vhd module inputs & outputs.

**HDL Notes**: The RCA in this experiment is provided for you. With external modules, you don't always need to use all the inputs and outputs of the module in your designs. For HDL to be happy, you must do the following for inputs and outputs:

<u>INPUTS:</u> All inputs require values, so you must assign them a '0' or '1'. The value you assign is typically the "don't do anything value" for that input as you're not going to use it and you don't want it to affect the module. The common vernacular is that you "hard-code" the input values.

<u>OUTPUTS:</u> If you're not using an output, you still include the output in the instantiation listing, but you don't associate it with anything. This approach serves as a note that you intentionally are not using that particular output. If this approach generates a warning, you can ignore it.

One key item in Verilog that you use all the time is the append operator  $(\{,\})$ . For example, this experiment works with 5-bit numbers, which you'll need to expand to for the univ\_sseg.v module. In words, you'll want to bit stuff it with zero. Here's the Verilog code for the operation:

Signal\_8bit = {3'b000, signal\_5\_bit}; -- convert signal from 5 to 8 bits

#### **Deliverables:**

- 1. HDL models for all modules you wrote in this lab activity

- 2. Black-box models for the circuits you modeled in this lab activity

- 3. Answers to the "questions"

- 4. Solution for design problems

#### **Questions:**

- 1. Show a closed form formula that relates the data width the number range for an unsigned binary number. Make sure you use an accepted format for specifying number ranges.

- 2. Show a closed form formula that relates the data width the number range for a signed binary number in RC format. Make sure you use an accepted format for specifying number ranges.

- 3. For a given bit-width, does the number of unique numbers in an unsigned binary and signed binary number in RC format differ? Briefly explain.

- 4. Can an 8-bit binary number in unsigned format ever be an odd number but have even parity? Briefly explain.

- 5. Can signed binary numbers in RC format have the notion of parity associated with them? Briefly explain your answer.

- 6. In computer programming, briefly describe why it is the best idea to use an unsigned integer type when it is known that the value will never be negative.

- 7. In computer programming, briefly describe what happens when a mathematical operation exceeds the ranges for the data types associated with that operation? Does the programmer typically know the range has been exceeded?

- 8. Often we refer to a design as a "flat" design. In terms of HDL modeling, briefly but fully describe what that term refers to.

- 9. In general, does the number of levels of a particular design affect the resources required to implement that design using an HDL and implementing that circuit on an FPGA? Briefly but fully explain.

#### **Design Problem:**

1. Design a circuit that four 10-bit inputs; two of the inputs are in RC format while the other two inputs are in unsigned binary format. The circuit has two outputs; one output indicates when all four inputs have equivalent decimal equivalents. The other output indicates when all four values have equivalent magnitudes. Use foundation modules when possible; minimize your use of hardware. State how the circuit is controlled.

- To design a basic arithmetic circuit with output validity feature

- To gain more practice in block-level modeling and HDL structural modeling

- To gain more experience designing and using arithmetic circuits

**Somewhat Meaningful Comments:** This activity is similar to a previous lab activity in many ways. First, it should be designed on a block diagram level. Secondly, it should use the univ\_sseg.v you used in a previous design. In other words, a good starting point for this circuit would be the final design in the previous lab activity. For this activity, you'll be designing circuit that adds two 5-bit signed binary numbers (four bits plus the sign bit) in RC format. As you know, the results of such operations are sometimes not valid so this circuit must clearly indicate this condition by using the VALID input of the univ\_sseg.v module.

Assignment: Design 5-bit signed binary number adder/subtractor circuit.

- If the button is pressed, the circuit displays the results of A + B; otherwise, the circuit displays the results of A B.

- Use the switches on the development board for the two 5-bit inputs (RC format) by considering the left five switches to be the A operand and the right five switches to be the B operand.

- Because the result of the mathematical operation may overflow the given range, you must use the VALID input on the univ\_sseg.v module to indicate if the result of the operation is valid or not.

- Keep in mind that this circuit is required to perform indirect subtraction by addition. Be sure to use the provided RCA module (modify as you need to) for your implementation.

- Simulate your final design; make sure you include enough test vectors to adequately test your design.

- You don't need to check for that "special case" of validity in your design.

**Simulation Notes:** The required simulation for this experiment has some issues. The univ\_sseg.vhd module is responsible for multiplexing the four 7-segment displays.

• Part of the univ\_sseg.v module includes a clock divider, which the module requires to properly multiplex the displays. Because of this delay, your simulation output will rarely see a change in the univ\_sseg.v's segment output (it changes about once every 2<sup>13</sup> input clock cycles). This then requires some cleverness in testing.

There are several ways to get around this, but there is one fairly simple approach for this experiment. When you run the simulation, the simulator automatically provides you with inputs and outputs on the highest level of the device under test. These provided values will not prove that your circuit is working for a long simulation time. The solution is to include the cnt1, sign, and valid output on the timing diagram. These signals are not directly involved with the univ\_sseg.v module's output, so they are not subject to the delays associated with the multiplexing operation of the module. This means that you can see the desired changes in the cnt1, sign, and valid signals that prove your test vectors generate the correct outputs of the univ\_sseg.v, but you won't see the segment and anode outputs of the module change. Be sure to annotate the cnt1, sign, and valid signal in your submitted simulation output.

#### Constraints:

- Don't use mathematical operators in this experiment other than provided modules.

- Minimize your use of hardware in your design.

#### **Deliverables:**

- 1. HDL models for all modules you wrote in this lab activity

- 2. Black-box models for the circuits you modeled in this lab activity

- 3. Answers to the "questions"

- 4. Solution for design problems

- 5. Annotated timing diagram output for your design; don't include the HDL testbench file.

#### **Questions:**

- 1. What is a really good reason that I don't put in the effort to design a subtractor in addition to my RCA?

- 2. The univ\_sseg.v module you used in this lab activity seemed to do a great job of simultaneously displaying more than one number at a time on the development board's seven-segment displays. But you were previously told that the displays could only show no more than one number at a time. Briefly explain what is going on.

- 3. Briefly describe the steps necessary in order to extend this design to 8-bit signed binary numbers (once again, assume your development board and provided modules are not limiting factors).

- 4. The output of this circuit arbitrarily showed dashes when the number was not valid. Speculate on why the designer of the module chose that particular output.

- 5. Using the development board under the conditions stated in this lab activity, would it have been possible to design an adder/subtractor unit based on 9-bit signed binary numbers (RC format)? The problem here is that you run out of switches to support 18-bit number. Consider all possibilities and fully explain your answer.

- 6. Quite often in digital design, there are boundary condition issues you need to deal with. What this means to me is that 98% of the errors I make in a design are with a boundary condition. This lab activity also has a boundary condition that essentially renders the result invalid even though it passes our simple validity checker. Briefly describe this boundary condition. HINT: the notion that it is a boundary condition roughly means that is has something to do with the far end of the given number range for the RC numbers.

- 7. Describe the modifications you would need to make to the circuit in this lab activity is you needed a 2\*A or A-B circuit instead of the A+B or A-B. Do not use a shift register in your solution.

- 8. Briefly state why you feel the number of test vectors you used in testing this design was sufficient to justify stating your design was working properly.

#### **Design Problems:**

- 1. Design a circuit that converts a three-digit decimal number to an 8-bit unsigned binary number. This circuit has three BCD inputs, which means four bits for the 100's, 10's, and 1's digit. The 8-bit output will always be sufficient to encode the three digital input value. State how the circuit is controlled.

- 2. Show a modification to your design in this experiment to support that also supports that "special case of validity. You only need to modify the BBD for this problem.

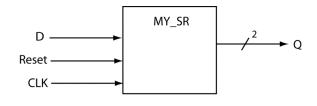

- To design a basic finite state machine from its basic underlying modules

- To design a basic counter that includes multiple controllable outputs

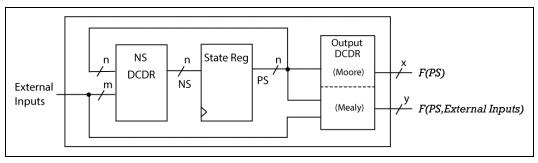

**Somewhat Meaningful Comments:** We typically model finite state machines (FSMs) as having three distinct underlying modules: the Next State Decoder, the State Registers, and the Output Decoder. The Output Decoder is special for several reasons. First, a FSM may not have an Output Decoder. Second, the Output Decoder can have one of two types of outputs. If the output is strictly a function of the FSM's state, the output is a Moore-type output. If the output Decoder that contains both types of outputs.

The basic module you'll design in this experiment is a counter, which is a sequential circuit that outputs a repeatable sequence of values (the "count"). Counters typically synchronize their count output with the active edge of a periodic input such as a clock signal. The counter in this experiment is a 4-bit counter, which inherently means it counts with binary count sequence spanning [0,15], or ["0000", "1111"]. The counter in this experiment can count both up  $(0\rightarrow 15)$  or down  $(15\rightarrow 0)$ .

Assignment: Design 4-bit up/down counter to the following specification.

- The counter is synchronous, which means changes in the count outputs are synchronized with the rising edge of the clock input. The counter counts up when the single button input (left-most button) is pressed; otherwise the counter counts down with the button is not pressed.

- The counter has two outputs as follows:

- ✤ 15-bit stoneage unary output, which you display on the 15 LEDs.

- Decimal output, which is displayed on the seven-segment displays (use the univ\_sseg.v device).

#### Supporting Information:

Your counter will need a clock divider module (provided for you) in order to slow down the system clock from 100MHz to something us humans can see on the dev board. Configure the clock divider so that the count frequency is about 2Hz. Keep in mind that the univ\_sseg.v module requires a fast clock such as the dev board's clock. Figure 5 shows a diagram showing the basic FSM model; not that this experiment requires only Moore-type outputs.

Figure 5: A diagram showing basic sub-modules of a FSM.

#### Constraints:

• Your design must include the three basic parts of a FSM. These must be modeled using discrete devices. That means decoders for the input and output, and registers for the state registers. I apologize in advance for the large decoders.

#### **Deliverables:**

- 1. HDL models for all modules you wrote in this lab activity

- 2. Black-box models for the circuits you modeled in this lab activity

- 3. State diagram; you only need to include states associated with {0, 1, 2... 13, 14, 15} (the idea is the full state diagram is repetitious (the thus tedious), so figure out a clean way of showing part of the state diagram while not wasting your time drawing the entire state diagram).

- 4. PS/NS table (no need to include the Output Decoder's output)

- 5. Answers to the "questions"

- 6. Solution for design problem(s)

#### **Questions:**

- 1. Briefly describe the difference between a flip-flop and a latch.

- 2. Sequential circuits are referred to as having "state". In your own words, briefly describe what exactly that means.

- 3. Briefly describe why state diagrams generally do not include any notion of a clock signal.

- 4. This experiment only asked you to draw a state diagram using six states. Briefly describe how many states the FSM in this experiment actually contains.

- 5. Briefly but completely describe the three basic modules of a FSM. Make sure your description includes which of the two classes of digital circuits the modules represent.

- 6. The state registers in a FSM are considered a synchronous circuit. Briefly describe what this means in context of the FSM.

- 7. This experiment used a clock divider to slow down the dev board's clock to something around 2Hz. Show how exactly you slowed down the clock, including any associated calculations.

- 8. Sequential circuits are known to contain memory, but it is not clear from the word "sequential" where the memory comes from. For this problem, briefly describe the relation between the word "sequential" and memory.

- 9. The FSM you designed in this experiment has status inputs and control outputs. Make a table showing the FSM's inputs and output; briefly describe the function of each input and output in terms of status and control signals.

#### **Design Problems:**

Design a 4-bit synchronous down counter. This output of this counter should reflect a binary output that represents RC numbers, which effectively means the counter counts as listed below. This counter should follow the standard FSM model that includes three basic modules, though you may not need all three modules for this problem. Provide a BBD for the top two levels of your design and a state diagram that models your FSM (feel free to abbreviate the state diagram, but make it clear).

{... 6, 5, 4, 3, 2, 1, 0, -1, -2, -3, -4, -5, -6, -7, -8, 7, 6, 5...}

- To implement a FSM with both Moore and Mealy-type outputs

- To implement a simple 2-digit 7-segment display multiplexing circuit

- To reinforce the notion of decoders when all else is in doubt

**Somewhat Meaningful Comments:** Yet another rite of passage in digital design is designing a circuit that drives a multiplexed display. The multiplexed display takes advantage of one of the less amazing aspects of the human visual system. Seven-segment display devices are common out there in digital land, and designing a multiplexed driver for such a device is not a big deal.

A four digit multiplexed display (7-segment devices) consists of 32 separate LEDs (including the radix point). This requires a relatively large amount of outputs to drive the circuit. To reduce the number of required outputs, we connect the display in a manner and take advantage of the human visual system (HVS) to make it "appear" to be doing what we want.

In a typical 7-segment display device, all the digits in the display share a single signal for each of the digits seven segments (and generally the decimal point as well). This means that at any given time, you can't drive more than one different number to the 7-segment display. In order to make it appear like there is more than one number on the display, we turn one number on for a short period of time, and then turn the next number on for a short period of time, etc. If we do this fast enough, it appears to your HVS that there is actually more than one number on the display at the same time. We refer to this as display multiplexing.

Assignment: Start with the circuit from the previous experiment, but do the following two modifications.

- Remove the univ\_sseg.v device and replace it with display multiplexing circuitry that you design. This multiplexing circuit must include a clock divider to slow the clock down to a reasonable frequency. This clock divider is in addition to the clock divider you already have in the circuit (recall that clock divider slow the clock down to a frequency that allowed humans to see the counting action on the 7-segment displays). The counter is a 4-bit counter that counts from 0-15, so you only need to design a two-digit display multiplexor.

- 2) Modify the stoneage unary output to allow it to show the count in either normal form or inverted form. Use the input that allows the counter to count up or down for this control. So when the counter is counting up, the LED display shows a normal stoneage unary count (LEDs on for each "count"); when the counter is counting down, show an inverted stoneage unary count (LEDs off for each "count").

#### Constraints:

- Minimize your use of hardware in your design

- Your display multiplexor hardware must be purely combinatorial

#### Deliverables:

- 1. HDL models for all modules you wrote in this lab activity

- 2. Black-box models for the circuits you modeled in this lab activity; make sure to show the appropriate low-level details of the display multiplexor.

- 3. Answers to the "questions"

- 4. Solution for design problems

#### **Questions:**

- 1. Briefly describe the FSM output-type classification of the stoneage unary output you used in the previous experiment and then in this experiment.

- 2. Briefly describe the FSM output-type classification of the decimal output you used in this experiment.

- 3. Briefly describe the particular attribute of a digital circuit (not of an HDL model) that gives the circuit the ability to store data.

- 4. Briefly describe the relation, if any, between a sequential circuit in digital design and a sequential statement in Verilog?

- 5. Briefly describe what the term "sequential" refers to in the term "sequential circuit".

- 6. Briefly describe why an AND gate is not functionally complete.

- 7. Explicitly show how you can obtain an OR function from an AND gate. In your own writing, show both the derivation and the resulting circuit element.

- 8. Explicitly show how you can obtain an AND function from an OR gates. In your own writing, show both the derivation and the resulting circuit element.

- 9. An EXNOR gate is often referred to as an "equivalence gate". Briefly explain how it would get such a name.

- 10. Briefly explain what characteristic of a circuit makes it a "mixed logic" circuit?

#### **Design Problems:**

Design a 3-bit synchronous up counter. Include a HOLD input that when asserted, prevents the circuit from counting. This output of this counter should be a 3-bit value in binary [0-7] format when the HOLD is asserted; otherwise a compliment of that 3-bit value when the HOLD is not asserted. This counter should contain all three basic FSM modules. Be sure to include a state diagram with your solution. Include a state diagram and a PS/NS table with your solution. State how the circuit is controlled.

- To gain experience designing Finite State Machines configured as counters

- To gain experience using the HDL behavioral method for implementing FSMs

**Somewhat Meaningful Comments:** Using FSM design techniques for counters is common digital design pursuit. The counter in this lab activity is a counter that has many potentially useful features. As you will see from the specification below, this FSM is not completely specified. You the designer thus have the choice of how to handle cases that are not completely specified. Your mission is to make it work as specified and to fill in the gaps in an intelligent manner. This is typical of a real-world design experience where someone who know a lot less than you do (namely, the management) has specified the design.

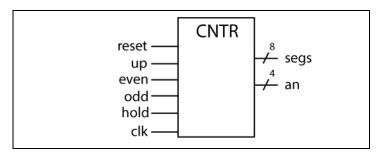

<u>Assignment:</u> Design a FSM that implements a synchronous 3-bit up/down counter with the attributes listed in Table 9. Visually test your counter using the circuit shown in Figure 6; choose about 2Hz for the FSM clock. The possible count values for this counter are: 0, 1, 2, 3, 4, 5, 6, 7; this counter naturally rolls over  $(7\rightarrow 0)$  and rolls under  $(0\rightarrow 7)$ .

- Use the provided FSM template as a starting point for the FSM

- Make the **RESET** signal asynchronous. Put asynchronous control signals in the code that models the FSM's registers; do not place it in the combinatorial portion of the circuit.

- If neither EVEN nor ODD are asserted, the counter counts in a normal count sequence in the direction determined by the UP control input.

- Your state diagram must have eight states

- You can display the output using a single bit or the univ\_sseg.v module

| Control<br>Input | Comment                                                            | Attribute    | I/O Map              |

|------------------|--------------------------------------------------------------------|--------------|----------------------|

| RESET            | Clears counter (count = 0)                                         | asynchronous | left-most<br>Button  |

| UP               | direction of count sequence (UP = '1' up; UP= '0' down)            | synchronous  | SW15                 |

| EVEN             | counts in an even sequence according to UP direction when asserted | synchronous  | SW0                  |

| ODD              | counts in an odd sequence according to UP direction when asserted  | synchronous  | SW1                  |

| HOLD             | prevents count from changing                                       | synchronous  | right-most<br>button |

#### Table 9: Attributes for the up/down counter.

Suggestions: Here are a few items that will expedite your path to success:

- When drawing your state diagram, use the labels **E**, **O**, and **H** for signals **EVEN**, **ODD**, and **HOLD**. This state diagram becomes rather busy; using these labels will help it readable.

- Plan on using an entire sheet of paper for your state diagram. The state diagram becomes busy; once again, your mission is to keep it readable.

Figure 6: The top-level circuit for testing the up/down counter.

#### **Constraints:**

- Don't use math operators in your FSM

- Your state diagram modeling the FSM must have eight states

- You must model your FSM using the behavioral modeling template. This model has two procedural blocks; one block is combinatorial and the other block is sequential.

#### **Deliverables:**

- 1. HDL models for all modules you wrote in this lab activity

- 2. Black-box models for the circuits you modeled in this lab activity

- 3. State diagram for FSM

- 4. Answers to the "questions"

- 5. Solution for design problems

#### **Questions:**

- 1. From your state diagram, what would happen if both the ODD and EVEN input were simultaneously asserted?

- 2. From your HDL model, what would happen if any other input is asserted at the same time as the RESET input?

- 3. Briefly describe the symmetry present in both the state diagram and HDL model of this FSM.

- 4. Self-correcting hardware is a great feature in digital design. Briefly describe what the term "illegal state recovery" means and the specific condition that it attempts to avoid.

- 5. Did the FSM model you used for the circuit in this lab activity use some form of illegal state recovery? Briefly explain.

- 6. Briefly state why it is that state diagrams never includes clock signals.

- 7. If someone told you they encoded their FSM using eight flip-flops, would you know how many unique states were in their state diagram? Briefly explain.

- 8. Write a closed form formula that relates the maximum number of unique states in a sequential circuit to the number of 1-bit storage elements in the sequential circuit.

- 9. Write a closed form formula that shows how many storage elements (n) would need to implement a circuit requiring Q unique states. This formula should include a floor or ceiling function.

#### **Design Problems:**

- 1. Design a counter that continuously counts in the following sequence:  $\{2, 5, 7, 1, 4\}$ .

- The counter has a hold input that prevents the counter from counting. The counter's output shows the sequence as given when the hold input is not asserted (positive logic), or negative values of the sequence when the hold input is asserted. In other words, the hold input pauses the counter and causes the output to display a negative version (RC format) of the current count.

- Make the design self-correcting by sending any unused states to state associated with count 7. The counter's output for unused states is zero.

Provide a high-level BBD, a PS/NS table, and a state diagram for this problem. Minimize your use of hardware.

## Exp 11: Sequence Detector FSMs

#### **Objectives:**

- To design and implement a FSM that you can use for something relatively useful

- To gain more experience using the HDL behavioral method for implementing FSMs

**Somewhat Meaningful Comments:** The design of sequence detectors using FSMs is one of the more basic uses for a FSM. The designs are not overly complicated yet they provided immediate gratification to FSM designers. In order to convince you that FSMs really work and they're actually on the cool side, you'll be implementing a FSM in this lab activity that acts as a sequence detector.

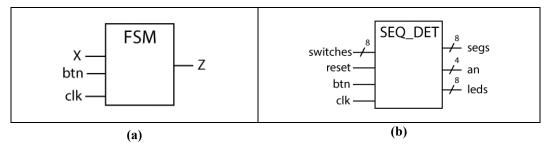

<u>Assignment:</u> Design a sequence detector that will detect the provided sequences according to the button press information below. Make your FSM a Moore-type FSM the resets when the one of the desired sequences are found. Drop your FSM design into the circuit shown in Figure 7. Here are the sequences:

- If BT0 is pressed: 100010

- If BT0 is not pressed: 100110

For this design, the SEQ\_DET module of Figure 7(b) is provided for you, but is missing the FSM. Figure 7(a) shows the BBD for the FSM you need in this experiment. The circuitry of the SEQ\_DET module provides the values on the **switches** input one bit at a time; the **leds** output shows which bit is currently being input to the FSM.

**Constraints**: only use one FSM in your design. Be sure to properly label all aspects of the associated state diagram.

Figure 7: The FSM BBD (a) and the top-level BBD (b) for this experiment.

#### **Deliverables:**

- 1. HDL models for all modules you wrote in this lab activity