# Investigation Into How the Floor Plan Layout of a Manufactured PCB Influences Flip-Chip Susceptibility to Vibration

Kangkana Baishya, David Mark Harvey<sup>®</sup>, Guangming Zhang, and Derek Richard Braden

Abstract—This article investigates how floor plan layout of a printed circuit board (PCB) influences the reliability of the component's solder joint connections when operated in a vibrating environment. A random vibration profile as seen in an automotive environment was used in full lifetime tests. An industry-standard FR4 PCB with electroless nickel immersion gold (ENIG) surface finish was manufactured with double-sided component placement including 14 flip chips, eight on the top side and six on the bottom side. Ultrasound scans were used as a nondestructive test to assess the integrity of solder joints from manufacture to failure. This enabled monitoring of the important interface between solder joints and flip chip where failure mostly occurs. The initial failure pattern was found by experiment where 86 cycles of random vibration caused all flip chips to mechanically fail. Failure followed a Weibull probability with a value of  $\beta = 1.297$ , indicating that failure rates increase with time. The results show that the reliability of a flip chip varies with its position on a PCB with some marked differences to component lifetimes. The results also show that for two-sided flip-chip placements on a PCB, backto-back, overlapped, and single-sided orientations have subtle effects on flip-chip lifetimes. Similarly, reliability varied with solder joint positions since joints on the sides of a flip chip nearest the PCB edges were less reliable than those on sides on a flip chip furthest away. Finally, design guidelines are offered to effect the most reliable flip-chip placement on a two-sided PCB when operated in a vibrating environment.

Index Terms—Flip chip, floor plan layout, solder joint, vibration.

# I. INTRODUCTION

OLDER joint fatigue failure under vibration loading has always been a great concern in the microelectronics industry. In automotive, aerospace, and military applications, electronic systems should be able to undergo various dynamic loads and vibration frequencies during their operation [1]–[4]. Vibration was identified to be one of the most important

Manuscript received February 26, 2020; accepted April 6, 2020. Date of publication April 13, 2020; date of current version May 11, 2020. This work was supported in part by Delphi, U.K., and in part by Delphi, Krackow, Poland. Recommended for publication by Associate Editor T. Chiu upon evaluation of reviewers' comments. (Corresponding authors: Kangkana Baishya; David Mark Harvey.)

Kangkana Baishya, David Mark Harvey, and Guangming Zhang are with the General Engineering Research Institute, Liverpool John Moores University, Liverpool L3 3AF, U.K. (e-mail: kbaishya010@gmail.com; d.m.harvey@ljmu.ac.uk; g.zhang@ljmu.ac.uk).

Derek Richard Braden is with the European Validation and Hardware Operations Engineering Department, Aptiv PLC, Coventry CV3 1JG, U.K. (e-mail: derek.braden@aptiv.com).

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCPMT.2020.2987334

causes of electronic failure by the U.S. Air force [5] and solder interconnects usually are the weakest link in terms of product reliability [6]. Therefore, solder joint reliability testing is necessary to understand the effects of high-frequency vibration, particularly for any manufactured electronics that are prone to encounter harsh environments in practice [7]. Liu and Meng [8] studied the lead-free solder joint behavior of ball grid array (BGA) packages under different random vibration loadings and results showed that the corresponding failure modes were converted from ductile fracture to brittle fracture with the increase of vibration intensity. Wong [9] presented a methodology to characterize and predict fatigue failure of BGA package solder joints under vibration loading based on board strain versus number-of-cycles-to-failure (or S-N) curve. The comparison of SnAgCu and SnPb solders in fatigue curves clearly indicated the better performance of SnAgCu solder system under high-cycle fatigue test, while this trend was reversed in low-cycle fatigue where SnPb solder has superior fatigue resistance. Che and Pang [10] carried out some sinusoidal vibration reliability tests for flip-chip solder joints and applied a linear cumulative damage analysis method (Miner's rule) to predict the life of solder joints. However, none of these studies attempted to conduct real-time vibration tests or were able to monitor the exact dynamics of manufactured solder joint reliability. Solder joint reliability, which is greatly affected by the component's floor plan, the thickness of the printed circuit board (PCB), and the influence of the surrounding components [6], has never been fully studied before. A previous article has investigated the effects of floor plan layout on through-life PCB reliability when considering thermal cycling effects [11]. This article investigates the reliability of solder joints in flip chips through real-time vibration and a nondestructive solder joint health monitoring system using acoustic microimaging (AMI/C-SAM) that detects the changes in mechanical integrity in the solder joints in terms of the mean intensity of reflected ultrasound signals from a solder joint [12]. Finally, PCB floor plan design guidelines for the most secure flip-chip placement for systems working in a vibration environment are proposed, which will ensure better reliability and improved lifetimes of PCBs in a vibration environment.

# II. EXPERIMENTAL DESIGN

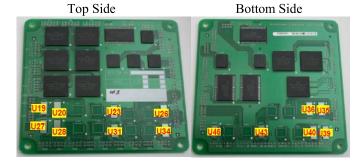

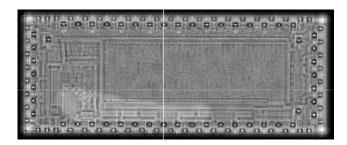

An industry-standard FR4 PCB of 0.8-mm board thickness (see Fig. 1) and a surface finish of electroless nickel immersion

Fig. 1. Generic board layout with flip-chip numbers [19].

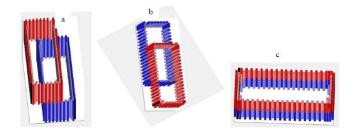

Fig. 2. Different flip-chip orientations. (a) Flip chip with back-to-back connection and offset along the breadth. (b) Flip chips with back-to-back connection with offset along the length. (c) Flip chips with back-to-back connections with no offset [19].

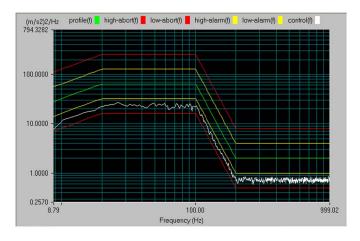

gold (ENIG) with various area array packages was designed at Delphi, Krakow, for the experiment. The 10-cm square manufactured PCB has a range of BGA and other area components populated carefully on both sides. One side of the PCB has eight flip chips, whereas the other side has six, making a total of 14 flip chips, numbered as shown in Fig. 1. Each flip chip has 109 solder joints. Table I shows more detailed information on the flip chips [13]. All the flip chips are placed in different positions on the PCB and also have different orientations relative to each other, as shown in Fig. 2. Flip chips U23 and U26 are stand-alone flip chips with no backto-back connections. U19-U35 and U20-U36 pairs are placed back-to-back with an offset along the breath [see Fig. 2(a)]. U27-U39 and U28-U40 pairs are placed back-to-back with an offset along the length [see Fig. 2(b)]. U34–U46 and U31-U43 pairs are placed back-to-back with no offset [see Fig. 2(c)]. An aluminum test fixture was also designed at Delphi, Krakow, for the experiment that can accommodate four test boards at a time within a 4–5-mm recessed support for each board, as shown in Fig. 3. Each PCB is secured to the test fixture by a screw torqued to  $1 \text{ N} \cdot \text{m}$  at its four corners. A random vibration profile used for the experiment is shown in Fig. 4. This profile was conceived with the help of automotive vibration experts in Delphi. The profile was designed to be a representation of the vibration loading experienced by many automobiles in real life. The setup is tabulated in Table II, with a level G rms = 9.5 g. A vibration shaker in Delphi, Liverpool, was programmed with this profile and used for the experiments, as shown in Fig. 5. Ultrasound C-scan images used for solder joint through life monitoring were obtained using the Sonoscan Gen6 C-Mode Scanning

TABLE I

INFORMATION ABOUT THE FLIP CHIPS [13]

| Flip chip                            |                          |

|--------------------------------------|--------------------------|

| Die X                                | 3948µm                   |

| Die Y                                | 8898µm                   |

| Die Z                                | 725μm                    |

| Poisson's ratio                      | 0.22 to 0.28             |

| CTE flip chip                        | 2.6 ppm/K                |

| UBM material                         | UBM stack is Al, Ni and  |

|                                      | Cu                       |

|                                      | with Cu being on the top |

|                                      | of stack.                |

| UBM pad size                         | 102μm                    |

| Level 1 interconnects (Solder joint) |                          |

| Solder bump diameter (middle)        | 140µm                    |

| Solder Bump height                   | 125μm                    |

| Solder Joint height after assembly   | 90μm ±5μm                |

| Solder material                      | Sn=52.9%, Pb=45.9%,      |

|                                      | Cu= 1.2%                 |

| Substrate                            |                          |

| Material                             | FR-4                     |

| Thickness                            | 0.8mm or 1.6mm           |

| Substrate x dimension                | 100mm, 5mm radius to     |

|                                      | corners                  |

| Substrate y dimension                | 100mm, 5mm radius to     |

|                                      | corners                  |

| CTE - PCB (ppm/K)                    | z=35x10-6, x=11x10-6,    |

|                                      | y=13x10-6, (in/in/c)     |

| Pad thickness                        | 35 - 42 microns          |

| Pad material                         | Cu with HASL orENIG      |

|                                      | surface finish           |

| Underfill                            | No underfill             |

Fig. 3. Aluminum test fixture with one PCB and three empty slots [19].

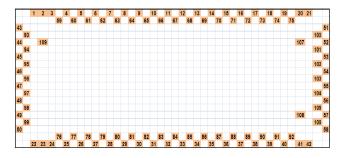

Acoustic Microscope in the LJMU Laboratory, as shown in Fig. 6. A schematic of how the 109 solder joints was labeled to help with analysis along with an ultrasound C-Scan of the solder joints in a flip chip is shown in Figs. 7 and 8, respectively. A resolution of 3  $\mu$ m was found to be optimal for the acoustic scanning after initial tests.

The PCB was mounted in the vibration shaker and vibrated according to the random profile obtained from Delphi, Krakow. As the total time to complete the mechanical failure of all the flip chips in the PCB was unknown, a pretest was conducted to help determine the maximum test time. All the flip chips were found to have reached complete failure after 86 vibration cycles, where each cycle was 4 min. Based on the pretest data, nine flip chips were selected according to their positions and

Fig. 4. Proposed random profile for the experiment (green trace) [19].

TABLE II

RANDOM VIBRATION PROFILE

| Frequency<br>(Hz)                             | 10 | 20 | 50 | 100 | 200 | 300 | 400 | 500 | 750 | 1000 |

|-----------------------------------------------|----|----|----|-----|-----|-----|-----|-----|-----|------|

| PSD<br>((m/s <sup>2</sup> ) <sup>2</sup> /Hz) | 32 | 64 | 64 | 64  | 2   | 2   | 2   | 2   | 2   | 2    |

Fig. 5. Vibration chamber in Delphi, Liverpool, U.K.

relative orientations in the PCB to be monitored by acoustic scanning at different scan intervals based on their pretest results, as shown in Table III. This through lifetime data collected as an acoustic image was then processed and used for further analysis using MATLAB.

Table IV shows the failure time and pattern of the flip chips.

### III. RESULTS AND DISCUSSION

# A. Weibull Analysis

The Weibull distribution is one of the most widely used lifetime distributions in reliability engineering. The equation for the probability density function (pdf) f(t) of a Weibull distribution is given by [13]

$$f(t) = \frac{\beta}{\eta} \left( \frac{t - \gamma}{\eta} \right)^{\beta - 1} e^{-\left( \frac{t - \gamma}{\eta} \right)^{\beta}} \tag{1}$$

where  $f(t) \ge 0, t \ge 0$  or  $\gamma, \beta > 0, \eta > 0, -\infty < \gamma < \infty$ .

Fig. 6. Sonoscan Gen6 C-Mode Acoustic Microscopy System (image courtesy of Sonoscan Inc.).

Fig. 7. Labeling scheme for 109 solder joints [16].

Fig. 8. C-scan of a target flip chip scanned at  $3-\mu m$  resolution.

TABLE III

SCAN INTERVALS FOR DIFFERENT FLIP CHIPS FOR 0.8-MM ENIG

| 0.8mm ENIG | Scan interval    |

|------------|------------------|

| U23        | 1 scan/cycle     |

| U26        | 1 scan/ 2 cycles |

| U27        | 1 scan/5 cycles  |

| U34        | 1 scan/5 cycles  |

| U19        | 1 scan/5 cycles  |

| U28        | 1 scan/10 cycles |

| U20        | 1 scan/10 cycles |

| U35        | 1 scan/5 cycles  |

| U40        | 1 scan/5 cycles  |

The parameters  $\beta$ ,  $\eta$ , and  $\gamma$  control the scale, shape, and location of the pdf function. The scale parameter  $\eta$  defines where the bulk of the distribution lies. The shape parameter  $\beta$

$\label{thm:table_iv} \mbox{TABLE IV}$  Flip Chip Failure Pattern for  $0.8\mbox{-mm}$  ENIG

| 0.8mm ENIG flip<br>chip no. | Cycles to failure<br>1 cycle = 4<br>minutes | Failure time in hours |

|-----------------------------|---------------------------------------------|-----------------------|

| U23                         | 3                                           | 0.2                   |

| U26                         | 14                                          | 0.933                 |

| U35                         | 21                                          | 1.4                   |

| U39                         | 23                                          | 1.533                 |

| U46                         | 24                                          | 1.6                   |

| U34                         | 29                                          | 1.933                 |

| U36                         | 34                                          | 2.267                 |

| U27                         | 45                                          | 3                     |

| U43                         | 48                                          | 3.2                   |

| U20                         | 53                                          | 3.533                 |

| U31                         | 55                                          | 3.667                 |

| U40                         | 57                                          | 3.8                   |

| U19                         | 68                                          | 4.533                 |

| U28                         | 86                                          | 5.733                 |

TABLE V

RELIABILITY BASED COLOR CODING SCHEME

| Color code                 | Criteria (% cycles to     |

|----------------------------|---------------------------|

|                            | failure, say X)           |

| Red: least reliable        | X≤25                      |

| Yellow: medium reliability | 25 <x≤ 50<="" td=""></x≤> |

| Blue: most reliable        | X>50                      |

defines the shape of the distribution, and the location parameter  $\gamma$  defines the location of the distribution in time.

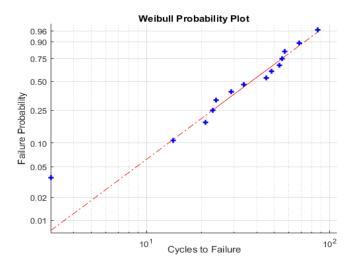

The Weibull distribution can take on the characteristics of other types of distribution based on the value of its shape parameter  $\beta$ . The Weibull shape parameter  $\beta$ , also known as the slope, is equal to the slope of the regressed line in a probability plot. The value of  $\beta$  has a marked effect on the failure rate of the Weibull distribution. Inferences can be drawn about a population's failure characteristics just by considering whether the value of  $\beta$  is less than, equal to, or greater than one. Populations with  $\beta < 1$  exhibit a failure rate that decreases with time, populations with  $\beta = 1$  have a constant failure rate that is consistent with an exponential distribution, and populations with  $\beta > 1$  have a failure rate that increases with time. Fig. 9 shows the Weibull probability plot of the 0.8-mm ENIG-based PCB from the observations of Table IV.

The shape parameter  $\beta$  [15] has been calculated to be  $\beta=1.297$ , which, being greater than 1, indicates that the ENIG PCB material set has a failure rate that increases with time. The fact that the data set closely follows the predicted Weibull distribution indicates the validity of the experimental data set.

# B. Reliability Analysis Based on Flip-Chip Position

Upon close observation of the failure (Table IV), one can argue that the flip chips in the PCB can be classified into three categories based on their reliability performance. If we consider 86 cycles as the total expected lifetime of a flip chip,

Fig. 9. Weibull plot for 0.8-mm ENIG PC.

Fig. 10. 0.8-mm ENIG board layout with color-coded flip-chip positions based on reliability.

then flip chips with a lifetime of less than 25% of expected lifetime will be considered as the least reliable, those above 50% will be considered as the most reliable, and those in between 25% and 50% will have medium reliability. In order to visualize this classification, color coding was introduced as detailed in Table V and implemented in Fig. 10. Fig. 1 shows the nomenclature of the flip chips, whereas Fig. 10 shows their respective reliability.

Now, from Table IV, it can be seen that the most reliable positions are those of flip-chip pairs U31-U43 and U40-U28. Of these flip chips U31-U43 is a pair with backto-back connection and no offset, while U40 is back-toback connected with offset along the length. On the other hand, the least reliable flip chips are U23 and U26. They were the first two flip chips to fail within the first few vibration cycles in the test boards. Both these flip chips are stand-alone and have no back-to-back connections. Considering then together U23 that is placed near the center of the PCB has lower reliability than U26. Hence, it can be safely concluded that in a PCB, flip chips with backto-back connections with no offset are the most reliable, while standalone flip chips with no back-to-back connections, especially the ones placed near the center of the PCB, are the least reliable when considering their susceptibility to vibration cycling.

Fig. 11. Positions of the flip chips selected for analysis on the PCB.

# C. Reliability Analysis Based on Flip-Chip Orientation and Solder Joint Position on PCB

In order to determine which of the solder joints fail first depending on the orientations and positions of the flip chip on the board, an in-depth analysis was done on selected flip chips U19, U26, U27, and U34, each of which belongs to a specific orientation.

- U34: Back-to-back with no offset, near the board edge at the corner.

- 2) *U19:* Back-to-back with breath offset, near the board edge next to the corner.

- 3) *U27:* Back-to-back with length offset, near the board edge near the corner.

- 4) *U26:* Single sided near the board edge next to the corner. Fig. 11 shows the flip-chip placement positions on the bare PCB in red circles. For the purpose of brevity and to avoid repetition, only the detailed analysis results for flip chip U34 will be discussed. Full details are available in [19].

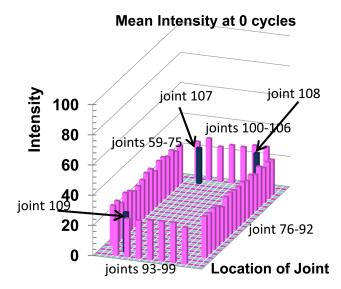

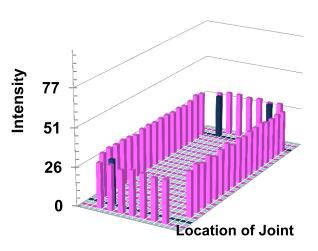

In order to witness the behavior of the solder joints in each of the flip chips based on their orientations and positions, a 3-D plot of the mean intensity of the 51 solder joints in the inner region of each of the flip chips was generated. The mean intensity represents the reflected ultrasound wave strength from the solder bump to the flip-chip interface. As this connection cracks during vibration testing, the mean intensity grows in line with the crack size, giving a useful parameter through which to assess solder joint failure. The reason for dealing with only the inner 51 joints is to eliminate an ultrasound imaging edge effects. Yang [16] in his thesis concluded that because of an acoustic edge effect witnessed at the imaging of the outer row of solder joints in these particular flip chips, getting an accurate measure of their image parameters is very difficult. When an ultrasound signal strikes the edge of a material, the signal is scattered away that results in a drop of the required information from the solder joint [17], [18]. This effect can be reduced by custom transducer design but cannot be eliminated entirely due to the intrinsic properties of ultrasound. Hence, in order to get a more accurate picture of the behavior of the solder joints in a vibration environment based on the positions and orientations of the flip chips, only the inner periphery of 51 solder joints was selected to be analyzed, as shown in Fig. 12.

From the detailed mean intensity analysis of each of the solder joints in flip chips of various reliabilities in the PCB using

Fig. 12. C-scan image of U34 showing the solder joints to be examined within the red box.

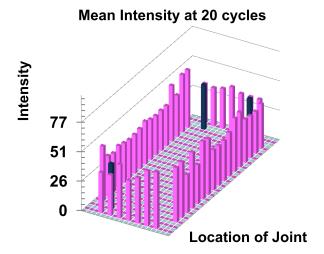

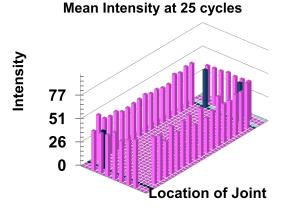

Fig. 13. 3-D plot of the mean intensity of joints 59-109 of U34 at cycle 0.

MATLAB [19], it was found that for all types of joints in a flip chip, the first trigger point occurs at around 35%–40% cycling and second change occurs at around 80%-85% cycling [19]. Thus, the failure pattern of any solder joint can be loosely said to fall into regions. The region between zero cycles and first trigger point where the crack initiates, the region between the first and second trigger point where the crack propagates, and finally the region after the second trigger point where the crack formed reaches its peak and finally the flip chip fails. Consequently, for flip chip U34 that has a total vibration cycling time of 29 cycles, the first trigger point of change or crack initiation should occur at around ten cycles, whereas the second trigger point should be at around 25 cycles. Hence, the solder joints at scan intervals of 0, 10, 20, and 25 cycles will be analyzed in detail. The reason for analyzing the scan at 20 cycles is because 20 cycles represent a point between the first and second trigger points and hence will provide valuable information on the crack propagation. Figs. 13–16 show the 3-D plots of the mean intensity of the solder joints of U34 at cycles 0, 10, 20, and 25, respectively.

# Mean Intensity at 10 cycles

Fig. 14. 3-D plot of the mean intensity of joints 59-109 of U34 at ten cycles.

Fig. 15. 3-D plot of the mean intensity of joints 59-109 of U34 at 20 cycles.

Fig. 16. 3-D plot of the mean intensity of joints 59-109 of U34 at 25 cycles.

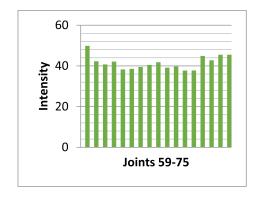

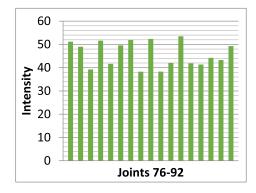

For a clearer visualization, the graphs in Figs. 17–21 show the intensity change of all the 51 joints at cycle 25. It should be kept in mind that all the joints had a mean intensity of around 20–25 at cycle 0, as shown from Fig. 13.

Fig. 17. Intensity of solder joints 59-75 (away from the PCB edge) at cycle 25.

Fig. 18. Intensity of solder joints 76-92 (near the PCB edge) at cycle 25.

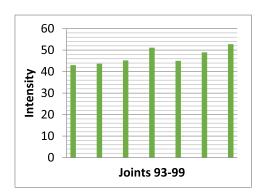

Fig. 19. Intensity of solders joint 93-99 (near the PCB edge) at cycle 25.

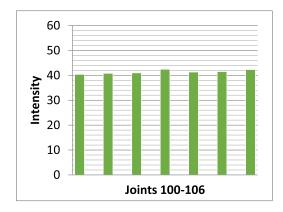

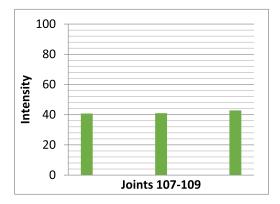

From the 3-D plots, it can be clearly seen that at cycle 0, all the solder joints have a mean intensity of around 20–25. However, after 25 cycles, joints 76–92 that are located near the edge of the board start showing more intensity change with an average intensity value of 45.8 compared with joints 59–75 that are located away from the edge and have an average intensity value of 41.2. Similarly, joints 93–99 that are located near the edge of the board start showing more intensity change with an average intensity value of 47.1 compared with joints 100–106 that are located away from the edge and have an average intensity value of 41.0. Joints 107–109 show a similar intensity change, but the intensity change of joint 109 that is located nearer the board edge is very slightly more than 107 and 108.

Fig. 20. Intensity of solders joint 100-106 (away from the PCB edge) at cycle 25.

Fig. 21. Intensity of solder joints 107-109 at cycle 25 (joint 109 is nearest the edge).

A similar pattern in the behavior of solder joints was observed in the case of the rest of the flip chips as well. In the case of U19, the solder joints near the edge of the board, namely 59-75, showed more damage compared with the joints at the side away from the edge, namely 76-92. The overlapping joints 95-99 and 103-106 show average damage, but joints 103-106 near the board edge have slightly more damage compared with joints 95-99. In the case of U27, the solder joints near the edge of the board, namely, 59-75, show more damage compared to the side away from the edge, namely 76–92. The overlapping joints 59–67 and 76–84 show average damage, but joints 59–67 near the board edge have slightly more damage compared with joints 76–84. Solder joints 68–75 have more damage compared with joints 59-67 and 76-92, whereas joints 85-92 have more damage than joints 76-84. Finally, in the case of U26, the solder joints near the edge of the board, namely 59-75 show more damage compared to the joints at the sides away from the edge, namely 76-109.

From all the earlier observations, it can be concluded that in the case of vibration loading, the solder joints near the board edges start failing first. Thus, the farther away from the edge a solder joint is, the better the reliability. Solder joints with back-to-back connections are more reliable than the ones placed in one-sided orientation. However, solder joints with back-to-back connections but located near the board edges are

less reliable compared with the ones located away from the board edges.

## D. Design Guidelines for Floor Plan Layout in a PCB

Based on all the observations mentioned in Sections III-B and III-C, certain design guidelines can be loosely suggested to ensure better reliability of solder joints and flip chips and improve their susceptibility to PCBs operated in a vibration environment.

- 1) Single-sided flip-chip placements should be avoided.

- Back-to-back connections should be made where possible.

- Placement of flip chips at the center of the PCB should be avoided.

- 4) Placement of flip chips very close to the edges of the PCB should be avoided.

- Back-to-back connection with no offset is the most reliable orientation for flip chips in PCBs subjected to vibration.

- Back-to-back connection with length offset is the second most reliable orientation for flip chips in PCBs subjected to vibration.

- 7) Finally, back-to-back connection with breath offset is the least reliable of the three offsets, but it is more reliable than a stand-alone single-sided connection.

# IV. CONCLUSION

In this article, the effects of vibration cycling on the reliability of flip chips of different positions and relative orientations in an industry-grade PCB were evaluated. Nondestructive testing in the form of AMI was used for data collection and MATLAB was used for data analysis. It was found that in the case of vibration cycling in a 10-cm square PCB attached by screws at each corner, flip chips with back-to-back connections with no offset are the most reliable, while stand-alone flip chips with no back-to-back connections, especially the ones placed near the center of the PCB, are the least reliable. A detailed 3-D mean intensity analysis of the degradation of individual solder joints in a flip chip was also done to study the failure patterns of individual solder joints in a flip chip based on their location and orientation on a PCB. It was found that in the case of vibration loading, the solder joints near the board edges start to fail first. Solder joints with back-toback connections were more reliable than the ones placed in the one-sided orientation. However, solder joints with backto-back connections but located near the board edges were still less reliable compared with the ones located away from the board edges. Thus, the farther away from the PCB edge a solder joint was, the better the reliability. Based on all these observations, a few design guidelines for the floor plan layout of flip chips in a PCB were proposed from this article.

# REFERENCES

[1] B. Gadalla, E. Schaltz, and F. Blaabjerg, "A survey on the reliability of power electronics in electro-mobility applications," in *Proc. Int. Aegean Conf. Electr. Mach. Power Electron. (ACEMP), Int. Conf. Optim. Electr. Electron. Equip. (OPTIM), Int. Symp. Adv. Electromech. Motion Syst.* (ELECTROMOTION), Sep. 2015, pp. 304–310.

- [2] R. Enrici Vaion, M. Medda, A. Mancaleoni, G. Mura, A. Pintus, and M. De Tomasi, "Qualification extension of automotive smart power and digital ICs to harsh aerospace mission profiles: Gaps and opportunities," *Microelectron. Rel.*, vols. 76–77, pp. 438–443, Sep. 2017.

- [3] P. Lall and K. Mirza, "A study on the effect of mean cyclic temperature on the thermal fatigue reliability of SAC solder joints using digital image correlation," in *Proc. ASME Int. Mech. Eng. Congr. Expo.*, 2015, pp. 1–11.

- [4] V. Samavatian, A. Masoumian, M. Mafi, M. Lakzaei, and D. Ghaderi, "Influence of directional random vibration on the fatigue life of solder joints in a power module," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 9, no. 2, pp. 262–268, Feb. 2019.

- [5] D. S. Steinberg, Vibration Analysis for Electronic Equipment. Hoboken, NJ, USA: Wiley-Interscience, 2000.

- [6] D. R. Braden, R. S. H. Yang, J. Duralek, G.-M. Zhang, and D. M. Harvey, "Investigation into the impact of component floor plan layout on the overall reliability of electronics systems in harsh environments," in *Proc. 3rd Electron. Syst. Integr. Technol. Conf. (ESTC)*, Berlin, Germany, Sep. 2010, pp. 1–6.

- [7] F. X. Che and J. H. L. Pang, "Study on reliability of PQFP assembly with lead free solder joints under random vibration test," *Microelectron. Rel.*, vol. 55, no. 12, pp. 2769–2776, Dec. 2015.

- [8] F. Liu and G. Meng, "Random vibration reliability of BGA lead-free solder joint," *Microelectron. Rel.*, vol. 54, no. 1, pp. 226–232, Jan. 2014.

- [9] S. F. Wong, P. Malatkar, C. Rick, V. Kulkarni, and I. Chin, "Vibration testing and analysis of ball grid array package solder joints," in *Proc.* 57th Electron. Compon. Technol. Conf., May/Jun. 2007, pp. 373–380.

- [10] F. X. Che and J. H. L. Pang, "Vibration reliability test and finite element analysis for flip chip solder joints," *Microelectron. Rel.*, vol. 49, no. 7, pp. 754–760, Jul. 2009.

- [11] R. S. Yang, D. R. Braden, G.-M. Zhang, and D. M. Harvey, "Effects of component placement on solder joint through-life reliability," *Proc. Inst. Mech. Eng. O, J. Risk Rel.*, vol. 228, no. 4, pp. 327–336, Aug. 2014.

- [12] R. S. H. Yang, D. R. Braden, G. Zhang, and D. M. Harvey, "Through lifetime monitoring of solder joints using acoustic micro imaging," *Soldering Surf. Mount Technol.*, vol. 24, no. 1, pp. 30–37, Feb. 2012.

- [13] D. Braden, "Non-destructive evaluation of solder joint reliability," Ph.D. dissertation, GERI, LJMU, Liverpool, U.K., 2012.

- [14] Reliability Engineering Resources. Accessed: Feb. 22, 2019. [Online]. Available: https://www.weibull.com

- [15] D. Di Maio and C. P. Hunt, "High-frequency vibration tests of Sn-Pb and lead-free solder joints," in *Proc. 2nd Electron. System Integr. Technol. Conf.*, Sep. 2008, pp. 819–824.

- [16] R. S. H. Yang, "Through-life non-destructive monitoring of solder joints using ultrasound," Ph.D. dissertation, GERI, LJMU, Liverpool, U.K., 2012.

- [17] J. E. Semmens and K. W. Lawrence, "Characterization of flip chip bump failure modes using high frequency acoustic micro imaging," in *Proc. IEEE 35th Int. Rel. Phys. Symp.*, Apr. 1997, pp. 141–148.

- [18] H. H. Jiun, Z. H. Shu, and X. Ming, "Characterization of flip chip bump failure mode by using high frequency 230 MHz MP and CP4 transducer," in *Proc. 10th Electron. Packag. Technol. Conf.*, Dec. 2008, pp. 601–607.

- [19] K. Baishya, "Through-life monitoring of the impact of vibration on the reliability of area array packages using non-destructive testing," Ph.D. dissertation, GERI, LJMU, Liverpool, U.K., 2019.

Kangkana Baishya received the B.Eng. degree in electronics and telecommunication from Assam Engineering College, Gauhati University, Guwahati, India, in 2011, the M.Sc. degree in wireless communications from the University of Southampton, Southampton, U.K., in 2012, and the Ph.D. degree in electronic and ultrasonic engineering from Liverpool John Moores University, Liverpool, U.K., in 2019.

Her current research interests include electronic reliability engineering, nondestructive testing of electronics, image processing, and wireless communications.

**David Mark Harvey** received the B.Sc. (Hons.) and Ph.D. degrees in electrical and electronic engineering from Liverpool Polytechnic, Liverpool, U.K., in 1979 and 1984, respectively.

From 1977 to 1979, he was an Electrical Engineering Degree Placement Student at British Steel, Sheffield, U.K. From 1983 to 1984, he was the Principal Electronics Design Engineer at Kratos Analytical Instruments, Manchester, U.K. From 1984 to 1985, he was the Principal Electronics Engineer at Plessey Crypto, Liverpool, U.K. In 1985, he joined

Liverpool Polytechnic, now Liverpool John Moores University (LJMU), where he has been a Professor of electronic engineering since 2003. He was the Director of two large technology transfer projects; the Electronic Design and Manufacturing (EDAM) Centre, LJMU, from 1996 to 2001, and the Engineering Development Centre (EDC), LJMU, from 2002 to 2008. His research has been concerned with design and test of electronic instrumentation and optical metrology systems. His recent focus has been on the nondestructive evaluation of manufactured automotive electronics using novel techniques.

Dr. Harvey is a Fellow of the Institution of Engineering and Technology, U.K., and a Chartered Engineer of the Engineering Council, U.K.

**Guangming Zhang** received the M.Sc. and Ph.D. degrees in mechanical engineering from Xi'an Jiao Tong University, Xi'an, China, in 1996 and 1999, respectively.

He joined the Institute of Acoustics, Nanjing University, Nanjing, China, in 1999. From 2001 to 2003, he was as a Post-Doctoral Fellow with the Signals and Systems Group, Uppsala University, Uppsala, Sweden. He also joined Liverpool John Moores University, Liverpool, U.K., as a Post-Doctoral Fellow in 2003, where he has been a Reader/Associate

Professor in ultrasonic engineering since 2014. In the past, he has undertaken research in acoustic signal and image processing, ultrasonic data compression, nonlinear acoustic imaging, nonlinear acoustical field simulation, acoustical micro imaging, surface acoustic waves motor, ultrasonic nondestructive evaluation of materials, and in the development of ultrasonic imaging systems. His current research interests include prognostics and health management of electronic systems, reliability testing of advanced microelectronic packages, sparse signal representations of acoustic signals in over complete dictionaries, advanced acoustical micro imaging, and artificial intelligence (AI) and matching learning for life prediction of electronics.

**Derek Richard Braden** received the B.Eng. degree in electrical and electronic engineering, the M.Sc. degree in information engineering and microelectronics, and the Ph.D. degree from Liverpool John Moores University, Liverpool, U.K., in 1998, 2000, and 2012, respectively.

From 1987 to 1992, he was a Product Engineer at Marconi Underwater Systems, Wirral, U.K. From 1993 to 1994, he taught control and instrumentation engineering at the Wirral Metropolitan College, Wirral, U.K. From 1994 to 1996, he was an Elec-

tronics Development Engineer with the Proudman Oceanographic Laboratory, Wirral. From 1996 to 1997, he was a Senior Development Engineer at Allen Group Limited, Bodelwyddan, Wales. From 1997 to 1998, he was an Experimental Officer with the Centre for Intelligent Monitoring Systems, University of Liverpool, Liverpool. In 1998, he moved to Aptiv PLC (formerly Delphi) as a Project Engineer, progressing to the Validation Engineering Group Manager in 2003 and finally to the European Validation and Hardware Operations Engineering Manager in 2011. His research has been concerned with the reliability and testing of products deployed in harsh environments, developing, and using through life inspection techniques. More recently, his research has been focused on prognostics of electronics-based systems and the deployment of artificial intelligence (AI) and deep learning to reduce test time and increase the understanding of component degradation.

Dr. Braden is currently a member of the Institution of Engineering and Technology, U.K. Additionally, he is also a member of the British Standards Committee, London, U.K., supporting the development of ISO16750 and a Visiting Research Fellow at Liverpool John Moores University.