# TEN COMMON DFN DSSUES AND HOW TO FIX THEM

### THE IMPACT OF AN INTERRUPTED DESIGN FLOW

Every day is busy for PCB designers; strict schedules and tight deadlines are a normal occurrence. From layout to manufacture and testing, a single holdup can cost a business untold amounts in lost productivity.

We've all been there: you create a great design that should be watertight. You are relieved when it gets sent off to be manufactured, but become frustrated when certain parameters have severe violations. You're stuck back to the drawing board, no closer to a finished piece than before and worse yet— you are already weeks down the line.

This scenario happens all too often, and this is why it's important to Design for Manufacture (better known as DFM). DFM is the basic practice of designing a product with the end (manufacturing) in mind, helping entire design process go as smoothly as possible; with little to no surprises. Simply put, when you design to your ending specs at the source, your company will greatly increase its productivity. Good DFM will keep your projects on schedule, prevent late-stage changes, and keep build costs predictable.

MFG Data Accepted

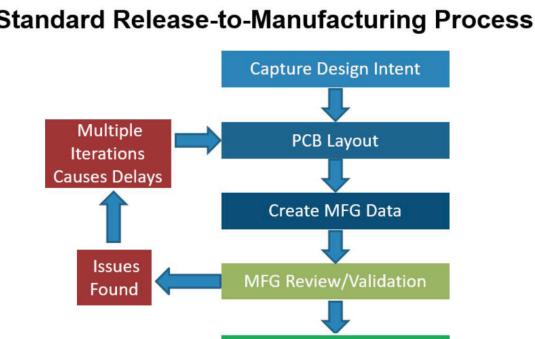

### Standard Release-to-Manufacturing Process

#### Typically, most issues are found much too far down the pipeline.

The design department has gone through the phases of design intent, layout, manufacturing data, and is now into review. Once there, the manufacturer finds issues with the board and you are forced to go back into the layout process to solve them. This can happen several times with multiple iterations, causing massive delays. Eventually, your board will be accepted, but not before your department has spent a significant amount of time, money, and man-power.

DFM issues are all too common; from reduced yields to missed time-to-market schedules, the blowback from such a failure can be detrimental in a competitive market. How do we break this cycle? The first step is to get a good understanding of the common DFM issues that plague design teams again and again. Recognizing roadblocks is a way to gain better insight in designing a better workflow in future projects.

### THE ISSUES A COMPREHENSIVE LIST

### There are numerous challenges to face when running DFM checks.

Knowing where to start in the vast array of PCB challenges is half the battle. To help narrow it down, we have outlined ten commom DFM issues for you to reference.

Read on to learn more about each type of problem and what you can do to fix them in your initial design. In addition, we have provided a few tips on how to implement better DFM practices in order to prevent these types of issues from occurring in the future.

- **1. Acid Traps**

- 2. Duplicate Drill Holes

- **3.** Insufficient Annular Ring

- 4. Missing Solder Mask

- **5.** Missing Paste Mask

- 6. Edge Violation

- 7. Solder Mask Slivers

- 8. Copper Slivers & Islands

- 9. Silkscreen-to-Pad Violations

- **10.** Copper Pad-to-Cutout

- **BONUS:** Component-to-Outline

#### **Acid Traps**

**Issue:** Acid traps are generated when a gap from pad-to-trace is too small, causing the etchant to pool. They are formed when creating an acute angle pad entry on a high-density PCB. Due to the un-etched copper, your board may short circuit.

Impact: Reliability issues and eventual failures due to continued erosion of traces over time.

**Fix:** Use enhanced entry routing techniques towards the beginning of the design process, such as minimizing the use of trace connections less than 45° or adding via holes to the area to allow the chemical to escape.

### DUPLICATE DRILL HOLES DESIGN ISSUE #2

#### **Duplicate Drill Holes**

**Issue:** A point where two vias meet on top of each other. They are hard to spot through visual inspection of CAD data. These often occur when using CAD tools that require workarounds to produce mouse-bite-style break-off tabs or multiple adjacent holes intended to be slots.

**Impact:** Disastrous on a manufacturing level, drill bits can—and will—break during drill operation, causing project delays and data re-working before you can see a finished product.

**Fix:** Change your duplicated drill holes for mouse-bite and slot operations to slotted-hole-types if your CAD tool supports the ability to do so.

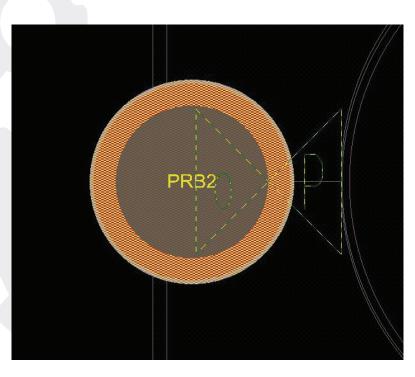

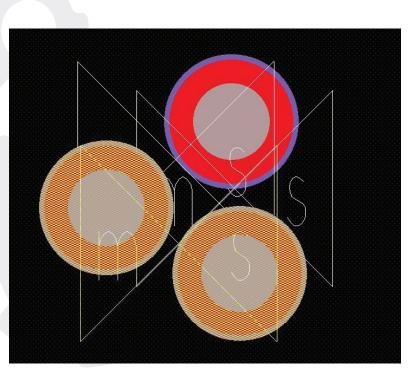

### **INSUFFICIENT ANNULAR RING** DESIGN ISSUE #3

#### **Insufficient Annular Ring**

**Issue:** An annular ring is the remaining copper ring left after drilling the pad. When the annular ring is too small, it may be deemed insufficient. It is very common for the drill to "walk" or go slightly outside of the intended area. In this case, it causes a "breakout" through the annular ring.

**Impact:** Pads easily delaminate from the board surface, causing time-costly repair and rework problems on the board.

Fix: Size up the annular ring in relation to the ratio between the drill and copper pad.

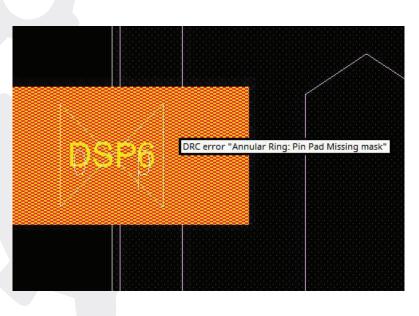

### MISSING SOLDER MASK DESIGN ISSUE #4

#### **Missing Solder Mask**

Issue: Missing solder mask openings on pads.

**Impact:** If there are no openings in the mask, you will not be able to bond the part, as the part will be covered in solder and rendered useless. Oftentimes, the manufacturer will find this issue, but it will still result in lost production time.

**Fix:** Update the padstack to include solder mask definition and use software program checks to detect the problem.

### MISSING PASTE MASK DESIGN ISSUE #5

#### **Missing Paste Mask**

**Issue:** Very similar to a missing solder mask, a paste mask opening allows you to put solder paste onto the land pattern to bond the part. Paste masks are used to create an assembly stencil and very small pads can be easily overlooked.

**Impact:** Causes missing masks when you go to assemble the board. This oversight also results in an additional cost impact when the stencil needs to be re-manufactured.

Fix: Update the padstack to include paste mask definition.

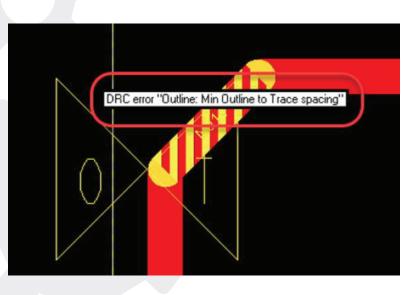

### EDGE VIOLATION DESIGN ISSUE #6

#### **Copper-to-Board Edge Violation**

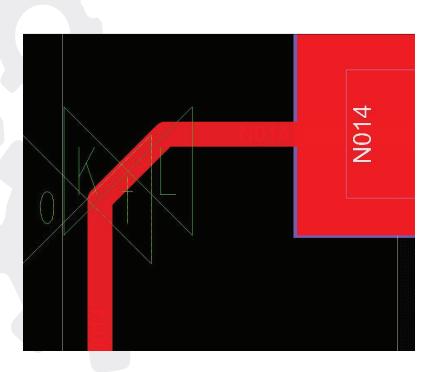

Issue: A trace or other copper feature is placed too close to the edge of the board.

**Impact:** The assembly rails on a conveyor require an allowance of space to work correctly. Placing traces too close to the edge may result in irreparable damage on the conveyed edges.

**Fix:** Move the copper trace away from the card edges and be sure to provide enough clearance all around. If you are unsure how much clearance is necessary, ask your manufacturer to provide specifics.

### SOLDER MASK SLIVERS DESIGN ISSUE #7

#### **Solder Mask Slivers**

**Issue:** Two pads that are very close together get solder mask applied to them and a thin web of solder forms between them.

**Impact:** The web can cause the solder to flake off in uneven pieces and result in small islands between copper features. The connection of solder between pads will also cause all pads involved to short out, causing delays in the final manufacturing process.

**Fix:** Employ a check in your design software and increase the clearance between vias and other objects, providing plenty of room for each specific solder mask placement on the board.

### COPPER SLIVERS & ISLANDS DESIGN ISSUE #8

#### **Copper Slivers and Islands**

**Issue:** Slivers and islands are common around areas of large pin arrays on a board. The areas are not connected to anything, floating in between components.

**Impact:** During the etching process, these slivers can float off and land on other areas of the board, shorting out the components upon contact. Additionally, remaining islands can cause noise coupling through the antenna effect.

Fix: Delete unconnected copper in the design process, thus removing the possibility of causing large problems later.

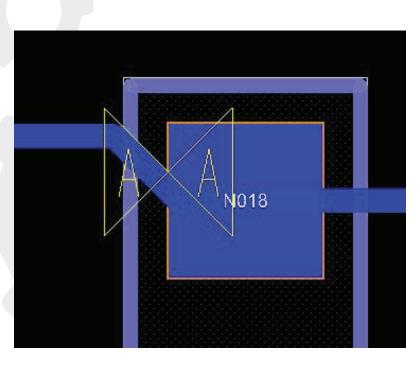

### SILKSCREEN-TO-PAD DESIGN ISSUE #9

#### Silkscreen-to-Pad Violation

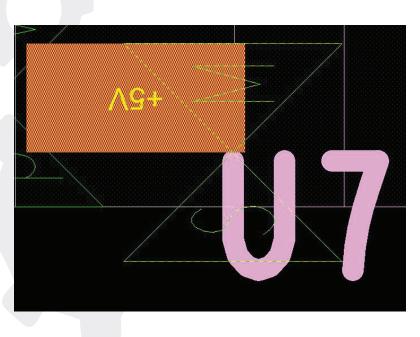

Issue: A violation that occurs when silkscreen text or lines are covering copper pads.

**Impact:** The ink from the silk-screening process can cause a contamination of the pads if it is not removed right away. This contamination can result in soldering issues further in the process.

**Fix:** Be aware of the location of your silkscreen and, if in violation, you can simply move the text or lines away from copper pads. If moving it is impossible, another alternative is to clip the text or lines back from around the pads.

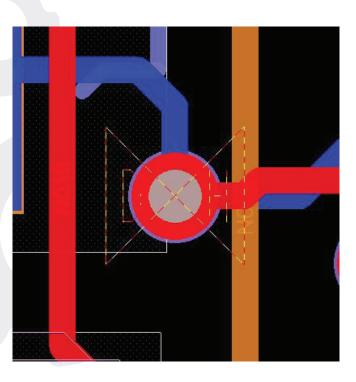

### COPPER PAD-TO-CUTOUT DESIGN ISSUE #10

#### **Copper Pad-to-Cutout**

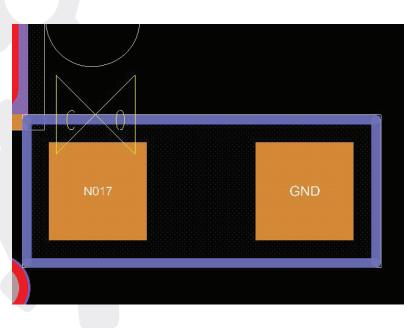

Issue: The copper pad features are too close to a cutout opening on the board.

**Impact:** This problem is often not found until the board is almost complete and, after going through most of the manufacturing process, it can be devastating to find a copper pad-to-cutout violation. It can require a major re-work from the beginning to correct it and its surrounding routing components. Such a setback will result in massive delays in your product-to-market time.

**Fix:** Look for the violation up front during part placement, before you advance too far in the design process. Adjusting at the beginning is easier than the end.

### **COMPONENT-TO-OUTLINE** BONUS: DESIGN ISSUE #11

#### **BONUS: Component-to-Outline**

**Issue:** Components are too close to the edge of the board in general.

**Impact:** If components are too close to the edge during a conveyor assembly, the parts may be damaged or ripped off the board entirely.

**Fix:** This can be addressed in your program by setting the manufacturing DRC rules to detect component-to-board edge spacing. Once you run a check for errors, they can be easily adjusted in and resolved during the initial placement process.

### **NOW WHAT?** HOW TO FIND ERRORS THE EASY WAY

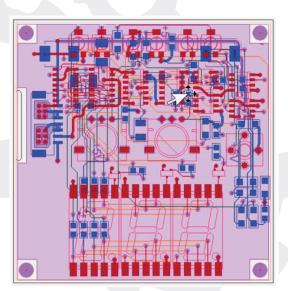

Manually spotting errors...

... is harder than it looks.

#### So HOW do you look for these errors in the design process?

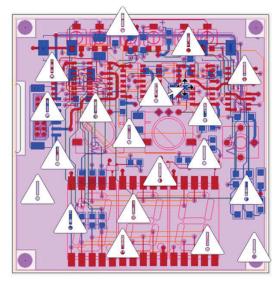

Well, we wouldn't suggest trying to manually find them all. A board design can have hundreds to thousands (or more) components and connections, and it is therefore next to impossible to find all the issues with the naked eye. At first glance, a board can look perfectly fine, but when you try to send it to your fabricator, you come to find it has dozens of errors.

The endless process of fixing and checking can become incredibly tedious and will cost a lot over time in lost production. There has to be a better way...right?

## **REAL-TIME DESIGN IN ORCAD** PREVENT DFM ERRORS BEFORE THEY HAPPEN

### With In-Design DFM Checking You Can:

See & Fix Violations In Real-Time

Eliminate Multiple Validation Iterations

Streamline Design Release Process

### It's simple: you need it, we've got it. Design your board in OrCAD.

For the best results, we recommend using the In-Design DFM checking process with OrCAD. Streamline your design process by scanning and spotting your board violations in realtime, with easy-to-implement fixes that will massively improve your time-to-production by eliminating multiple validation iterations. It's easy, efficient, and effective. With real-time DFM checking, OrCAD users are reducing their manufacturing validation times by 70%. What could you do with that extra time (and peace of mind)?

EMA Design Automation is a trailblazer in product development solutions offering a complete range of EDA tools, PLM integrations, services, training, and technical support. EMA is a Cadence® Channel Partner serving all of North America. EMA develops a host of custom solutions to enhance the OrCAD products, and all are distributed through a worldwide network of value added resellers. Visit www.ema-eda.com for more info.