# Velocity CAE Program Generator

For Simulation to ATE and

ATE to ATE Conversion

Release 8.3.5.0

# Configuration Guide

# Velocity CAE Program Generator Configuration Guide

---

## COPYRIGHT NOTICE

Copyright  2016 Alliance ATE Consulting Group, Inc.

All rights reserved

Documentation version 3.0

Any technical documentation that is made available by Alliance ATE Consulting Group is the copyrighted work of Alliance ATE Consulting Group and is owned by Alliance ATE Consulting Group.

**NO WARRANTY.** The technical documentation is being delivered to you AS-IS and Alliance ATE Consulting Group makes no warranty as to its accuracy or use. Any use of the technical documentation or the information contained therein is at the risk of the user. Documentation may contain technical or other inaccuracies or typographical errors. Alliance ATE Consulting Group, Inc. reserves the right to make change without prior notice.

No part of this publication may be copied without the express written permission of Alliance ATE Consulting Group, 3080 Olcott St Suite 110C, Santa Clara, CA 95054.

## TRADEMARKS

Velocity CAE Program Generator, and ShellConstructor are trademarks of Alliance ATE Consulting Group.

SmarTest, 93000, and 93K are trademarks of Advantest Corporation.

Typographic Conventions

This document uses specific typographic conventions in defining the syntax of all Velocity Configuration File elements. The following is a list of those conventions for each major syntactic category.

**Bold** Reserved words, such as keywords, plus any other symbols that are to be typed exactly as shown.

**Italicized** Placeholder for a user-specified symbol; or, placeholder for a high-level syntactical element – made up of smaller elements – that will be subsequently defined.

**[ ]** Regular style (not bold or italic) square brackets are used to enclose optional elements. For elements in which square brackets are part of the syntax, the brackets will be in bold font.

**{ }** Regular style (not bold or italic) braces (or, “curly brackets”) are used to enclose elements that are to be repeated 0 or more times. For elements in which braces are part of the syntax, the braces will be in bold font.

**|** The vertical bar is used to separate alternative choices for an element.

**::=** Two regular style colons and an equals sign means “can be replaced by”. This is used for breaking down a high-level syntactical element into its constituent elements.

The following is an example of a syntax definition using the typographic conventions listed above:

```

PINS pinList startStopList [ condition ] [

map      ]      where,      pinList      ::=

pinName|groupName{,pinName|groupName

e}      startStopList      ::=      startAddr-

stopAddr{,startAddr-stopAddr}      condition

::=  COND  =  {conditionList}  where,

conditionList      ::=

refPin[[relativeCycle]]=“pinState”{

```

,refPin[[relativeCycle]]="pinState"}

map ::= {MAP [ originalStateList ]:[targetState] }

where, originalStateList ::= one or more

single bit logic-state characters

targetState ::= one or more single bit logic-

state characters OBSERVATIONS:

1. In the PINS definition:

- a. The symbols pinList, startStopList, condition, and map are high-level syntactical elements that are subsequently broken down into smaller elements.

- b. The use of regular style square brackets around condition and map means that they are optional.

2. In the pinList definition (pinList ::=):

- a. The symbol pinList is defined as a comma-separated list of elements in which each element can be either a pinName or a groupName.

- b. Note the use of the regular style vertical bar to indicate a choice of either pinName or groupName.

- c. Note the use of the regular style braces to indicate 0 or more additional pinName or groupName elements, each preceded by a required comma.

- d. The fact that the first occurrence of pinName|groupName is not enclosed in square brackets or braces means that at least one element must be specified. Any others are optional.

3. In the condition definition (condition ::=):

- a. The use of bold style braces means that braces are to be typed as a required part of the syntax.

4. In the conditionList definition (conditionList ::=):

- a. Note that the symbol relativeCycle is enclosed in two sets of square brackets.

- b. The innermost brackets are in bold font, indicating that square brackets are to be typed as a required part of the syntax.

- c. The outermost brackets are in regular font, indicating that the element within is optional.

Table of Contents

|                                            |    |

|--------------------------------------------|----|

| 1.0 GENERAL INFORMATION .....              | 10 |

| 1.1    What is a Configuration File?.....  | 10 |

| 1.2    Creating a Configuration File ..... | 11 |

| <br>                                       |    |

| 2.0 CONFIGURATION FILE STRUCTURE .....     | 16 |

| 2.1    Elements of Syntax.....             | 17 |

| 2.2    Control Definitions.....            | 17 |

| 2.3    Line-Oriented Structure.....        | 19 |

| 2.4    List of Control Types .....         | 21 |

| 2.5    Order of Control Definitions .....  | 22 |

| 2.3    Example Configuration File .....    | 23 |

| <br>                                       |    |

| 3.0 CONTROL DEFINITION REFERENCE .....     | 29 |

| 3.1 Environment Definitions .....          | 30 |

| 3.2 General Build Definitions .....        | 32 |

| 3.2.2 TARGET_PORT Definition .....         | 32 |

| 3.2.3 LIBRARY .....                        | 34 |

| 3.2.4 HEADER .....                         | 34 |

| 3.2.5 WARNING .....                        | 35 |

| 3.2.6 BUS .....                            | 35 |

| 3.3 Pin Configuration Definitions .....    | 36 |

| 3.3.1 PINLIST Definition.....              | 36 |

| 3.3.2 BIDIRECTIONAL CONTROL.....           | 38 |

| 3.3.3 GROUP Definition.....                | 39 |

|                                          |    |

|------------------------------------------|----|

| 3.4 Source-Port-Specific Variables ..... | 41 |

| 3.4.1 IGNORE TIMEPLATE.....              | 41 |

| 3.4.2 JOB .....                          | 41 |

| 3.4.3 MACROSTYLE.....                    | 41 |

| 3.4.4 MASTER .....                       | 42 |

| 3.4.5 PERSISTENCE .....                  | 42 |

| 3.4.6 SYNC .....                         | 43 |

| 3.4.7 UNDERSAMPLE.....                   | 43 |

| 3.4.8 OVERSAMPLE .....                   | 43 |

| 3.4.9 VCDPAGE .....                      | 44 |

| 3.4.10 SAMPLE .....                      | 45 |

| 3.5 Target-Port-Specific Variables.....  | 45 |

| 3.5.1 BINARY.....                        | 45 |

| 3.5.2 COMBINATION .....                  | 47 |

| 3.5.3 CONTEXT .....                      | 47 |

| 3.5.4 CONFIGURATION (PIN FILE).....      | 48 |

| 3.5.5 CTIM .....                         | 48 |

| 3.5.6 DOMAIN TRACKING.....               | 49 |

| 3.5.7 FAMILY.....                        | 49 |

| 3.5.8 FASTMODE .....                     | 50 |

| 3.5.9 FSPINS .....                       | 50 |

| 3.5.10 MEMORY .....                      | 51 |

| 3.5.11     METHOD .....                  | 51 |

| 3.5.12 MODEL .....                       | 52 |

| 3.5.13 STATEMAP .....                    | 52 |

| 3.6 Verilog Feedback Variables .....     | 53 |

| 3.6.1 MAXDELTA Definition .....          | 53 |

| 3.6.2 MODULE.....                        | 53 |

| 3.6.3 VERILOG Definition.....            | 54 |

| 3.6.4 WINDOW.....                        | 54 |

| 3.6.5 FEEDBACK FILTER.....               | 55 |

|                                     |    |

|-------------------------------------|----|

| 3.7 General Purpose Variables ..... | 57 |

| 3.7.1 COMMENT .....                 | 57 |

| 3.7.2 DDRMODE .....                 | 57 |

| 3.7.3 DELAY .....                   | 59 |

| 3.7.4 INIT .....                    | 59 |

| 3.7.5 PAGE .....                    | 60 |

| 3.7.6 INIT .....                    | 61 |

| 3.7.7 SUBROUTINE .....              | 62 |

| 3.7.7 PERPAT .....                  | 62 |

| 3.7.7 PERPORT .....                 | 63 |

| 3.7.7 BURSTMODE .....               | 63 |

| 3.7.8 TERMINATION .....             | 64 |

| 3.7.9 TRISTATE .....                | 64 |

| 3.7.10 WARNINGS .....               | 65 |

| 3.7.11 MINREPEAT .....              | 65 |

| 3.7.12 MAXLOOP .....                | 66 |

| 3.7.13 DEBUG .....                  | 66 |

| 3.7.14 BURST .....                  | 67 |

| 3.8 Timing Variables .....          | 67 |

| 3.8.1 CAPTUREMODE .....             | 69 |

| 3.8.2 CAPTURE .....                 | 69 |

| 3.8.3 DATARATE .....                | 70 |

| 3.8.4 EDGES .....                   | 71 |

| 3.8.5 EQUATION .....                | 72 |

| 3.8.6 NORMALIZE .....               | 72 |

| 3.8.7 OPTIMIZE .....                | 72 |

| 3.8.8 BLOCK .....                   | 73 |

| 3.8.9 PERIOD .....                  | 74 |

| 3.8.10 DRIVE Block .....            | 75 |

| 3.8.11 STROBE Block .....           | 76 |

| 3.8.13 RUNNINGCLOCKS .....          | 77 |

| 3.8.14 GLOBALSPEC .....             | 78 |

|                                                |     |

|------------------------------------------------|-----|

| 4.0 CUSTOM LEVELS.....                         | 80  |

| 4.0.2 Power Sequences .....                    | 81  |

| 4.0.3 Power down sequencing .....              | 82  |

| 5.0 CUSTOM TIMING.....                         | 83  |

| 5.01 TEST Definitions .....                    | 84  |

| 5.02 FLOW Definitions.....                     | 91  |

| 6.0 CUSTOMIZING PATTERNS .....                 | 93  |

| 6.2     BASE Syntax .....                      | 94  |

| 6.3     Command and Parameter List Syntax..... | 94  |

| 6.3.1 TYPE (optional) .....                    | 95  |

| 6.3.2 DOMAIN (optional).....                   | 95  |

| 6.3.3 FUNC (optional).....                     | 95  |

| 6.3.4 LOOP.....                                | 96  |

| 6.3.5 REPEAT.....                              | 96  |

| 6.3.6 MATCH.....                               | 96  |

| 6.3.7 START.....                               | 96  |

| 6.3.8 STOP .....                               | 97  |

| 6.3.9 WAIT .....                               | 97  |

| 6.3.10 CUSTOM PATTERN EXAMPLES.....            | 98  |

| 6.4 Logical Masking .....                      | 99  |

| 6.4.1 PINS.....                                | 99  |

| 6.4.2 MAPS.....                                | 100 |

| 6.4.3 CONDITIONS.....                          | 101 |

| 6.4.4 PIN DUPLICATION.....                     | 102 |

| 6.5     Serial Masking.....                    | 103 |

| 6.5.1 SYNTAX .....                             | 103 |

| 6.5.2 EXAMPLES .....                           | 104 |

# 1.0 GENERAL INFORMATION

A brief look at what a Velocity CAE configuration file entails and how it is created and used.

## 1.1 What is a Configuration File?

A Configuration File is a human-readable, ASCII text file used by Velocity to control the conversion process.

Some of the aspects of the conversion process that a Configuration File controls are:

- The directory into which files generated by the conversion are to be written

- The period by which a VCD pattern is to be divided into cycles

- The target pin list, including test system resource assignments

- Pin groups

- Custom timing

- Custom levels

- Rules for creating custom patterns from existing patterns

- Standardized test and power up/down definitions

- Test flow

Every Velocity conversion – whether the ShellConstructor or Design-to-Test (D2T) or Tester-to-Tester (T2T) – requires the use of a Configuration File.

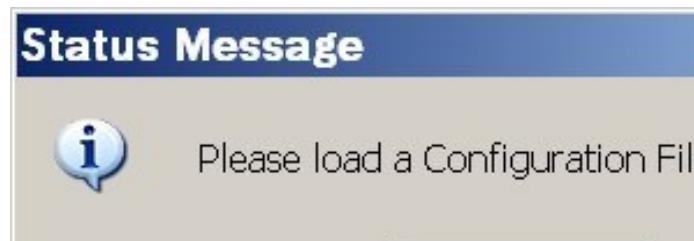

If the user does not specify a Configuration File and attempts to run a conversion, Velocity will display the following error message:

Configuration Files can be given any name, within the limitations of the host operating system. But, all names use a .cfg extension. They can reside in any directory that the user chooses.

## 1.2 Creating a Configuration File

As a human-readable, ASCII text file, a Configuration File can be created and edited using any text editor. The user may choose to start from nothing and create the entire Configuration File in the text editor; or, use an existing file as a template and edit those elements which differ.

As an alternative, Velocity offers a way to speed up the Configuration File creation process. The Velocity GUI can quickly and automatically generate an initial Configuration File from an existing pattern file that is to be converted.

The automatic process will create a file containing, at a minimum, the definition of the target file path and the pin list. The user can then add any other required elements in the text editor.

### 1.2.1 Automatically Generating an Initial Configuration File

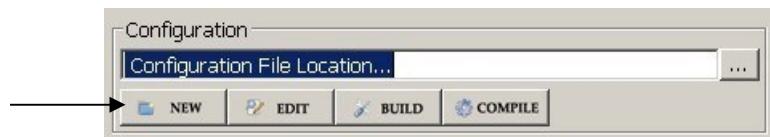

- From the GUI Configuration menu, select New.

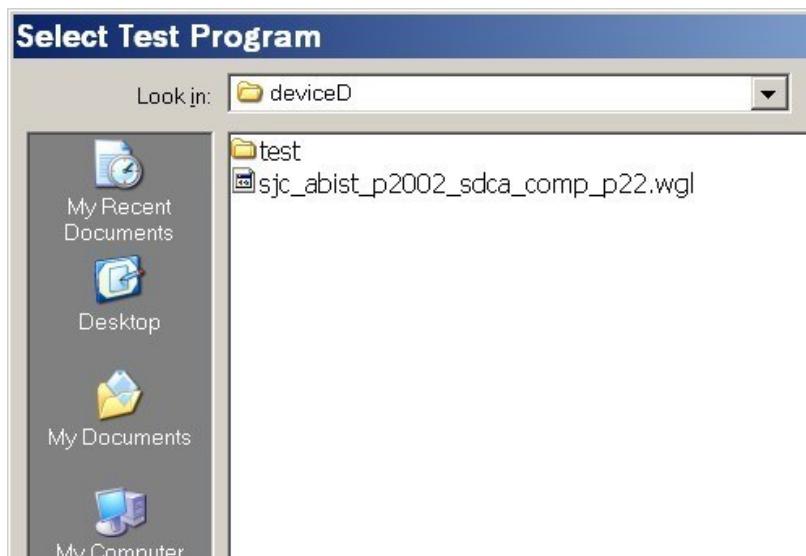

- A window similar to the following will appear.

- Navigate to the directory containing the simulation output files or ATE files from which you want to build a test program.

- Select any one file which, at a minimum, defines all of the required pins to be used in the test program.

- Click the Open button. A progress indicator window will pop up, following by a completion message, similar to the one shown next:

- Note the location of the new Configuration file, as shown in the message. Click the OK button to acknowledge.

## 1.3 What Happens During the Conversion Process?

In order to better understand the aspects of the pattern conversion process that are controlled by the Configuration File, it is useful to have a basic understanding of what happens during conversion.

### 1.3.1 Conversion Process Inputs

Every Velocity conversion takes, as input, one or more pattern files of one of the following supported types:

- STIL

- VCD/EVCD

- WGL

- VCT

- CPTD (Credence ASL3000)

- XLS/ATP (Teradyne J750)

- XLS/ATP (Teradyne UltraFlex)

- ADR (Teradyne J973)

- AVC/DVC (Advantest 93000)

### 1.3.2 “Cyclized” vs. “Uncyclized” Pattern Formats

ATE test systems output functional stimulus to the device (and sample functional responses from the device) in the form of a vector sequence. The vectors are presented at a particular rate defined by the cycle time (also known as the period).

The following are excerpts from a STIL pattern file and timing file, respectively, showing how digital pattern sequences and corresponding cycle timing are represented in an ATE environment:

```

////////////////////////////// Pattern Block: example_vectors

////////////////////////////// Pattern example_vectors { Start_example_vectors:

W "tps66000_10000";

V { all = 0XXXXXXXXXXXXXXXXXXXXXXZ00XXXXXX1XXXXXX1XXXXXX0X00X00XXXX1X; }

//0

V { all = 0XXXXXXXXXXXXXXXXXXXXXXZ00XXXXXX1XXXXXX1XX0XX0X00X00XXXX1X; }

//1

```

```

////////////////////////////// Timing Blocks

/////////////////////////////

Timing "customTiming" {

WaveformTable "tps66000_10000" {

Period 'PERIOD';

Waveforms {

"addr[10]" {

01Z { '0.000*PERIOD' D/U/Z; }

LHXM { '0.091*PERIOD' L/H/X/T; }

}

"addr[11]" {

01Z { '0.000*PERIOD' D/U/Z; }

LHXM { '0.091*PERIOD' L/H/X/T; }

}

}

}

```

Many other simulation and test data formats, such as WGL (Waveform Generation Language), also have a concept of vectors and cycle times, which can be translated to tester independent STIL format in a relatively straightforward manner. These kinds of pattern formats can be categorized as cyclized formats.

The following are excerpts from a WGL file, showing how digital pattern sequences and cycle timing, corresponding to the STIL example above, are represented in a WGL format:

```

timeplate tps66000_10000 period 66000ps

...

"addr[10]" := input[0ps:S];

"addr[11]" := input[0ps:S];

...

"addr[10]" := output[0ps:X, 6000ps:Q'edge];

"addr[11]" := output[0ps:X, 6000ps:Q'edge];

```

## OBSERVATIONS:

1. In the above comparison of STIL and WGL formats, the pins were not defined in the same order; so, the vector columns will not match up. However, the same underlying vector data, per pin, would be contained in each format.

2. In the STIL example on the previous page, note how vectors and cycle timing are brought together by preceding a sequence of vector lines (those lines that begin with “V”) with a waveform table selection line beginning with “W”. The waveform table specified after the “W” is defined within the Timing Block shown on the same page.

3. In the WGL example above, cycle timing is defined within a timeplate definition, and then brought together with vectors in individual vector lines (those lines containing the keyword vector), by referencing the timeplate name.

Not all pattern formats are cyclized. The most notable examples of non-cyclized formats are the VCD (Value Change Dump) and EVCD (Extended Value Change Dump) formats. In these non-cyclized formats, signal patterns are represented as a continuous stream of events, where an event is a change of state at a particular point in time relative to the beginning of the pattern.

The following is an excerpt from an example VCD file:

```

... #1000

pT 0 0 <262 pT 0 0

<263 pX 6 0 <265 pX 6

0 <266 pL 6 0 <267

#3000 pb 6 6 <9

```

```

pb 6 6 <10 pb 6 6

<11 pb 6 6 <12

#4000 pN 6 6 <96

pN 6 6 <97 ...

```

#### OBSERVATIONS:

1. The lines beginning with “#” are timestamps, with the time unit being specified previously in the file with the \$timescale statement. (In this example, the time unit is 1ps; so, 1000 represents 1ns.)

2. Following each timestamp line is a sequence of value change lines, one for each signal which changes state at that timestamp. (Signals which do not change state at that timestamp are not listed.)

3. The first field of each value change line is the state to which the signal changes. The fourth field is an arbitrary, user-defined symbol for a specific signal.

For VCD, Velocity will analyze the spacing of timing events for each signal, and determine a best-fit tester cycle time and edge delays for your test program.

## 2.0 CONFIGURATION FILE STRUCTURE

Information on the structure and syntax of a Velocity Configuration File.

## 2.1 Elements of Syntax

Configuration Files are made up of a number of different types of syntactic elements.

At the top level, there are two main types of elements. These types are:

- Control Definitions, which define particular aspects of the conversion and program generation process; and,

- comments, which begin with the '#' symbol and continue to the end of the line.

## 2.2 Control Definitions

Control Definitions can be categorized into two forms: single-line and multi-line.

### 2.2.1 Single-line

A single-line definition begins with a keyword, includes one or more parameters, and continues to the end of the line or to the beginning of a comment, whichever comes first.

The following PERIOD definition is an example of a single-line Control Definition:

|        |                 |

|--------|-----------------|

| PERIOD | 5.000ns default |

|--------|-----------------|

In this example, the keyword is PERIOD, and the two parameters are 5.000ns (the value of the target period for cyclization) and default (the name given to this particular target period, or Clock Domain).

### 2.2.2 Multi-line

A multi-line definition (also called a block) consists of a starting line, zero or more sub-parameter lines, and an ending line.

- Starting Line

The starting line begins with a keyword and includes zero or more parameters.

- Sub-parameter Line

A sub-parameter line consists of one or more keywords and/or user-defined symbols or values whose order depends on the type of Control Definition. Each line provides further details in the definition of the Control.

- Ending Line

The ending line consists of the keyword END followed by the starting line keyword. The following PINLIST block definition is an example of a multi-line Control Definition:

```

PINLIST

ANALOG_VDD           default IO      ANALOG_VDD

CVDD                 default IO      CVDD

HOLDn                default IO      HOLDn

END PINLIST

```

Note that the block begins with a starting line consisting only of the keyword PINLIST and ends with an ending line consisting of END PINLIST. In between are sub-parameter lines that begin with a pin name and consist of several parameters that define properties of the pin.

### 2.2.3 Comments

Comments can appear anywhere within the Configuration File, with the following restrictions:

- They only extend to the end of the line. Multi-line comments require a separate starting “#” for each line.

- Everything from the starting “#” to the end of the line is part of the comment. No part of a Control Definition will be recognized by Velocity if placed after the “#”.

- If a comment is placed at the end of a Control Definition line, the starting “#” must be separated from the last Control Definition line character by whitespace. (See below for more information on the use of whitespace in Configuration Files.)

The following is an example of a multi-line comment in a Configuration File, with the comment on each line taking up the entire line:

```

#####

##  PinList Definition

#####

```

The following is an example of a comment at the end of a Control Definition line (in this case, the starting line of a TEST definition block):

```

TEST contNegative 150 # Continuity test with negative forcing current

```

### 2.2.4 Keywords

Keywords are Velocity reserved words. That is, they may not be used for user-defined names, such as ClockDomain names, Pin names, and Pattern names.

Keywords are NOT case-sensitive. For example, Velocity would interpret period the same as PERIOD or, even pErIoD. However, for readability purposes and for establishing a standard convention, it is recommended that all keywords be in UPPER-CASE.

### 2.2.5 Parameters

Parameters are elements of a Control Definition that allow the user to provide details for a particular instance of the Control. The user does so by giving a user-defined symbol or value, called an argument, at the corresponding parameter location.

For example, the first parameter in the starting line of the TEST block definition is the test name. In the example above, the argument for that parameter is “contNegative”.

Arguments for parameters ARE case-sensitive. So, a later test flow definition referencing the TEST called “contNegative” would have to specify the exact same case.

### 2.2.6 Use of Whitespace

Whitespace in a Configuration File includes spaces and tabs.

A Configuration File may contain any amount of whitespace at the beginning and end of lines, and between keywords, parameters, and comments. Some parameters, such as the pin list of a PINS masking definition, can be specified with multiple sub-elements separated by a non-whitespace character. The following example shows a PINS sub-parameter definition within a PATTERN block definition:

```

PATTERN func_pat_masked

PINS Q0,Q1,Q2,Q3 55-83

END PATTERN

```

Note that the pin list, “Q0,Q1,Q2,Q3”, is considered the argument to one parameter of the PINS definition. Therefore, it contains no embedded whitespace. The individual sub-elements (Pins in this case) are separated only by commas. Likewise, the cycle range parameter is made up of a start and stop address separated by a hyphen.

## 2.3 Line-Oriented Structure

The main elements of a Configuration File – Control Definitions and Comments – follow, for the most part, a line-oriented structure. That is, the end-of-line (i.e. carriage return) marks the end of:

- Single-line Control Definitions;

- Starting and Ending lines of Multi-line Control Definitions;

- Sub-parameter lines of Multi-line Control Definitions (with exceptions noted below); and,

- Comments.

The only exceptions to the end-of-line termination are the masking sub-parameter definitions – ON, OFF, and PINS – of a PATTERN block definition. Those sub-parameter definitions are terminated by a semicolon (;) and are allowed to extend to multiple lines. This feature allows for long, complex masking definitions. Refer to the detailed description of the PATTERN block syntax later in this guide.

Also, as noted in the previous section of this guide on Comments, a Control Definition line may be terminated by the beginning of a Comment on the same line.

## 2.4 List of Control Types

The following table lists all of the available Control Types for a Configuration File, along with a brief description.

| Control Type | Description                                                                                                                                                                                                                                   |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PATH         | Base directory path for test program files                                                                                                                                                                                                    |

| DEVICE       | Sub-directory of path specified by PATH Control, used to hold test program files for a specific device                                                                                                                                        |

| PROGRAM      | Base file name used for various timing, levels, and pattern files and subdirectories                                                                                                                                                          |

| SOURCE_PORT  | Default value for the Source port. This will cause the source port to be automatically defined when the Configuration File is loaded. Valid entries can be chosen from anything that is present in the Source Port drop down list in the GUI. |

| TARGET_PORT  | Default value for the Target port. This will cause the target port to be automatically defined when the Configuration File is loaded. Valid entries can be chosen from anything that is present in the Target Port drop down list in the GUI. |

| PERIOD       | Specifies the time period used for “cyclizing” a VCD or EVCD pattern, per “Clock Domain”                                                                                                                                                      |

| EDGES        | Specifies maximum number of timing edges to expect within a tester period                                                                                                                                                                     |

| PINLIST      | Assigns type and tester resource to each active Pin                                                                                                                                                                                           |

| MODEL        | (Advantest 83K- and 93K-specific) Specifies tester model                                                                                                                                                                                      |

| MEMORY       | (Advantest 83K- and 93K-specific) Type of pattern memory to use                                                                                                                                                                               |

| METHOD       | (Advantest 83K- and 93K-specific) Type of test method to use                                                                                                                                                                                  |

| SUBROUTINE   | Defines whether pattern subroutines from source will be flattened in-line with the calling pattern, or kept as a separate, called pattern                                                                                                     |

---

|             |                                                                                                                                                               |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MACROSTYLE  | For STIL sources                                                                                                                                              |

| PERSISTENCE | Specifies whether Velocity samples a VCD file for a short or a long portion for calculating a best-fit cyclization period                                     |

| UNDERSAMPLE | Specifies a strobe interval, N, to apply to a converted pattern, in which only every Nth cycle can have output strobes, and intervening cycles will be masked |

| DELAY       | Assigns cycle delay to pins listed                                                                                                                            |

| PATTERN     | Defines a custom pattern modified from an existing pattern                                                                                                    |

| TIMING      | Defines custom timing for a set of Pins to override the timing derived from the input files                                                                   |

| LEVELS      | Defines DC levels for a set of Pins to be used in the test program                                                                                            |

| POWER       | Defines a power up or power down sequence                                                                                                                     |

| TEST        | Creates a specific instance of a standardized test type                                                                                                       |

| FLOW        | Defines a sequence of previously-defined TEST instances to be inserted into the test program                                                                  |

| TERM        | Defines the beginning of termination block that can be used to Set the drive action for comparisons on IO pins                                                |

---

## 2.5 Order of Control Definitions

Many of the Control Definitions can reference elements that are defined in other Control Definitions elsewhere in the Configuration File. For example, a TIMING block definition can reference a Pin defined in the PINLIST block or a Group defined in a GROUP definition.

Elements must be defined in a Configuration File before they can be referenced. Therefore, the order of Control Definitions within the file is important. The order of the Control Types shown in the previous table is the recommended order in which those types should be defined.

NOTE: It is not necessary to define every Control Type in a Configuration File. Velocity uses a default set of properties and behaviors for those aspects of a conversion not defined in the Configuration File. Only those Control Types with properties which differ from the defaults need to be defined.

## 2.3 Example Configuration File

The following simple Configuration File example includes definitions from each of the Control Types:

```

#####

# ASCII Velocity Configuration File

#####

PATH /home/field/testPrograms

DEVICE 56374

PROGRAM ShellExample

#####

# PIN LIST: This will define regular IO and power pin defs

#####

PINLIST

p0      default    I    0 11

p1      default    I    0 83

q0      default    O    0 69

q1      default    O    0 76

cpd     default    CLK  0 62

cpu     default    CLK  0 55

VS1    DPS        POW  4 0

END PINLIST

GROUP clocks = "cpu,cpd"

#####

# Pattern lists

#      The following patterns will be translated. If the pattern is #      not in the list, then it will

# be skipped. If the pattern is #      not in the source file then a warning will be issued.

#####

PATTERN

multipleLoop

BASE SpecFunc

LOOP 5,10 16

END PATTERN

#####

# Timing and Levels

#      definitions will define the values of specs. The following

#      values will be assigned by default. Groups and pins can # be defined to override

#      defaults by using a pin name or group name.

#####

TIMING default period 100ns offset 0ns

```

```

duty 50% drive 25%

receive 90%

END TIMING

LEVELS default

POWER 3.3V

VIL 10%

VIH 90%

VOL 40%

VOH 60%

END LEVELS

#####

# Power up and power down

#####

POWER nominal

VS1 1.25V 500mA 5uS

END POWER

#####

# Test Definitions

#

#           The following tests will be defined as discrete functions

#           that can be executed as user commands or as part of flows

#####

TEST contNegative 150

TYPE cont

FORCE -10uA

CLAMP 2V

LOW      400mV

HIGH     800mV

PINS     ALL

END TEST

TEST funcSpec 1

TYPE      func

PATTERN SpecFunc

END TEST

#####

# Flow Definition

#

#           The following tests will be executed in the following #   order. If no

#           flow is defined, then all the tests will # be included in the order they are defined.

#####

FLOW experimentName

TEST contNegative

```

```

POWER nominal

TEST funcSpec

DELAY 15ms

POWER off

END FLOW

```

## 3.0 CONTROL DEFINITION REFERENCE

Definitions and examples for all configuration file variables and blocks

## 3.1 Environment Definitions

The Environment section of the Configuration File consists of a set of definitions that define the location and naming of the target test program files. Typically, this is the first section in a Configuration File.

Velocity divides the test program location and file names into three parts:

- base path – Typically, points to the directory used as the parent directory of all test programs.

- Device name – Appended to the base path. Categorizes test programs by device.

- Program name – Specifies a base file name that Velocity will use for many of the generated test files. (Pattern files for the target tester are typically named for the source pattern files.)

The test program directory path and file names are defined by the following Control Types:

- PATH

- DEVICE

- PROGRAM

### 3.1.1 PATH

Syntax:

PATH *pathName*

where,

*pathName* is a directory path specifier

Example:

```

PATH /home/programs

```

NOTE: The directory path specifier must use valid syntax for the underlying file system.

### 3.1.2 DEVICE

Syntax:

```

DEVICE directoryName

```

where,

directoryName is the name of a directory

Example:

```

DEVICE      myDeviceName

```

### 3.1.3 PROGRAM

Syntax:

```

PROGRAM filename [equationNumber]

```

where,

fileName is the base name to be used for generated test files

equationNumber is the base number to be used for equation set numbering

Example:

```

PROGRAM      finalTest

finalTest 10          # Begin with equation set number 10

PROGRAM

```

Using the PATH, DEVICE, and PROGRAM Definitions in the above examples, Velocity would create test program files for the Build under the directory

`/home/programs/coolChip`

A number of the created test files would begin with base file name `finalTest`. Their location under the device directory (or subdirectories thereof) would depend on the specific target test system.

## 3.2 General Build Definitions

The General Build section of the Configuration File consists of a set of definitions that define the basic settings common to any conversion.

### 3.2.1 SOURCE\_PORT Definition

Specifies the Source Port for the Velocity conversion. Valid entries can be chosen from anything that is present in the Source Port drop down list in the GUI.

Syntax:

`SOURCE_PORT sourcePortType`

where, `sourcePortType` is a valid licensed source entry.

Examples:

`SOURCE_PORT WGL`

`SOURCE_PORT VCD`

NOTE: The source type must match a valid licensed entry or this variable will be ignored.

### 3.2.2 TARGET\_PORT Definition

Syntax:

`TARGET_PORT targetPortType`

where, `targetPortType` is a valid licensed target entry. Valid entries can be chosen from anything that is present in the Target Port drop down list in the GUI.

Examples:

`TARGET_PORT STIL`

`TARGET_PORT 93K`

NOTE: The target type must match a valid licensed entry or this variable will be ignored.

### 3.2.3 LIBRARY

This variable is used to define the name and location of any predefined libraries that you want to have included in the target program

Syntax:

LIBRARY EXTERNAL|LOCAL LIBRARY\_FILE\_NAME

where,

EXTERNAL|LOCAL directs Velocity whether to physically copy this library to the target program or simply refer to its path through a makefile or some other method depending on the target.

LIBRARY\_FILE\_NAME is the path and name of the library file itself Examples:

|        |                                         |

|--------|-----------------------------------------|

| HEADER | LOCAL /usr/local/lib/someLibrary.so     |

| HEADER | EXTERNAL /usr/local/lib/ someLibrary.so |

NOTE: referenced library file must be present and valid for the target

### 3.2.4 HEADER

This variable is used to define the name and location of any predefined headers that you want to have included in the target program

Syntax:

HEADER EXTERNAL|LOCAL HEADER\_FILE\_NAME

where,

EXTERNAL|LOCAL directs Velocity whether to physically copy this header to the target program or simply refer to its path thro a makefile or some other method depending on the target.

HEADER\_FILE\_NAME is the path and name of the header file itself Examples:

|        |                                       |

|--------|---------------------------------------|

| HEADER | LOCAL /usr/local/include/someHeader.h |

|--------|---------------------------------------|

|        |          |                                 |

|--------|----------|---------------------------------|

| HEADER | EXTERNAL | /usr/local/include/someHeader.h |

|--------|----------|---------------------------------|

NOTE: referenced header file must be present and valid for the target

### 3.2.5 WARNING

This variable allow the user to block WARNING statements that are generally ignorable such as MISSING PIN warnings. Warnings for ASYNC or snapping will still be printed because they are indicating data edge being moved in the output files. But, anything that is skipped in such a way that it is not going to affect other pins will be left out if warnings are set to off

USAGE: WARNING ON|OFF

### 3.2.6 BUS

This variable sets the interpretation for BUSSES during export of ATE and REPLAY files and also how pin names are chosen when generating a new CFG.

Bus representation means that square brackets would be used o indeix pins within a bus

By default BUS AUTO is used.

When BUS is OFF, the bracketed index would be replaced with an underscore for each index.

USAGE: BUS ON|OFF|AUTO

BUS ON: AutoGenerated PINLIST will use Bus notation so that Both the ATE and the REPLAY files will use Bus notation

BUS OFF: AutoGenerated PINLIST will use Bus notation so that BOTH ATE and the REPLAY files will NOT use Bus notation

BUS AUTO: AutoGenerated PINLIST will use Bus notation so that ATE will NOT use Bus notation, but REPLAY files WILL use Bus notation.

## 3.3 Pin Configuration Definitions

### 3.3.1 PINLIST Definition

Syntax:

PINLIST

pinName domain pinType [slot] [channel] [alias1 [alias2...aliasN]]

END PINLIST

The PINLIST block defines, per pin, the tester channel assigned and any alternate versions of that name used in the simulation or ATE conversion source.

The tester channel information that can be specified includes:

- domain:

- For digital pins: default or any port name that does not have a n underscore)

- For power supplies: DPS16, DPS32, UHC4, MSDPS (type must be POW)

- pinType: I, O, IO, CLK, TRIG, REF, POW, R, DIR, A, MASK or NC.

I: pure input pin

O: pure output

IO: bidirectional

CLK: special case of input which will use spec values that apply to CLK instead of regular simple drive actions when specs are available.

REF: pure input pin that is used as a zero reference for all edge values in a VCD/EVCD.

POW: power pin. This would then assume that the domain value is assigned with a power supply type

R: relay pin (essentially unused. But, useful as a placeholder)

A: analog pin (essentially unused. But, useful as a placegolder)

MASK: pin will be included in the output files, but all source data will be ignored. Data will be assigned as “X” on all cycles

NC: No Connect. Pin will be completely ignored as removed from outputs

TRIG: pure input that will automatically default all data to “0” so that triggers can be added manually on the tester.

- Slot number (optional)

- Channel number (optional)

- Aliases This is a space delimited list of alternate names that can be used in source files that will be expressed in the target files as whatever is in the pinName field. You can specify as many Aliases on a pin line – separated by whitespace – as you need. Velocity uses Aliases to match simulation or ATE pin names that are different from the target pin name.

#### “REMOVE” as alias

Generally, aliases and pin names must be unique. The exception to this is when the alias “REMOVE” is used. This is a special alias that instructs Velocity to remove this pin from the resulting compiled target files, but leaves it in so that it can be used as part of MASK blocks or simply as markers in the ascii files. The pin will not be visible once loaded on the tester.

The following is an example of a PINLIST definition:

```

#####

# PinList

Definition

#####

# PINLIST

ANALOG_VDD      DPS16  POW 230 2

HOLDn      default I 101 1 hold_n holdn

WPn             default O 101 8 wp_n anapadext_data_n      DPS16

POW 230 3 END PINLIST

```

Pin ANALOG\_VDD uses channel 2 of a DPS16 card in slot 230.

Also, note that pin HOLDn has aliases of hold\_n and holdn, meaning that it can take its data from simulation or ATE conversion sources that use either of those alias names.

### 3.3.2 BIDIRECTIONAL CONTROL

One special case within the PINLIST section is the bidirectional control pin. A control pin will only be needed for standard VCD translations. This source port format does not have a state character differentiation between input and output. Therefore, without the extra control wire, there is no way to determine the IO state of a bidirectional pin. For these types of simulations, there must always be a set of control wires that would also be included in the VCD file. These are “virtual” pins that are used to define the IO direction of other pins. In other words, these pins are controls for other pins.

The Velocity configuration syntax for these is similar to the regular pins except the alias column would be used to make reference to another pin instead of merely providing an alternate name for the active pin. There will then be two rows used to define each bidirectional pin. One for the pin itself, and another for the control wire defining its IO state. Once this is defined the control wire’s state is kept as the VCD file is processed. At any given time, if the control pin is actively high, then the pin which it controls is set to output mode. If the control wire is low, then the pin which it controls is set to input mode. Example

|          |             |         |

|----------|-------------|---------|

| DATA0    | default IO  | data[0] |

| DATA1    | default IO  | data[1] |

| DATA2    | default IO  | data[2] |

| DATA3    | default IO  | data[3] |

| control0 | default DIR | DATA0   |

| control1 | default DIR | DATA1   |

| control2 | default DIR | DATA2   |

| control3 | default DIR | DATA3   |

In the above example, there are 4 pins defined as IO and 4 pins defined as DIR. For the IO pins, there is an alias that defines an alternate nomenclature that the simulation file might use to express the given pin name. For the DIR pins, the alias column contains an entry that is already defined as a column 1 pin name. This pseudo-alias is the key that provides the connection between the control pin and its target.

The pin listed as DIR type will not show up in the target test pattern. These are treated as virtual pins rather than real pins that would require data to be provided behind them.

As stated above, the default behavior for control pins is that a control pin high means output mode. Control pin low means input mode. This behavior can be inverted by also inserting the keyword “NEG” at the end of the control pin definition (after the alias). If the NEG keyword is used, then the convention will be opposite. Control pin high will indicate input mode. Control pin low will indicate output mode. Example

|          |             |           |

|----------|-------------|-----------|

| DATA0    | default IO  | data[0]   |

| control0 | default DIR | DATA0 NEG |

### 3.3.3 GROUP Definition

The GROUP Control definition allows you to assign a name to a group of pins, for easier reference elsewhere in the Configuration file.

To define a Group, use the keyword GROUP followed by a Group name, followed by an equals sign (=) and a comma-separated list of pin names enclosed in double-quotes (""). The following is an example of a Group definition:

```

GROUP DBUS = "D0, D1, D2, D3, D4, D5, D6, D7"

```

If you use a group as a member of another group, this group must have already been defined. If not already defined a configuration loader error will occur.

## Automatic Group definitions

There are a number of groups that are automatically generated. These groups are generated automatically because certain API's assume that they are there. For example, the functional test API does an automatic connect on all pins. This assumes that there is a group named "allpins" that is there and this group's contents include all of the digital pins for a given device.

---

### Automatic Group Description of Contents

#### Name

---

|         |                                                                      |

|---------|----------------------------------------------------------------------|

| allpins | All digital pins not including any trigger pins that may be assigned |

|---------|----------------------------------------------------------------------|

---

|        |                        |

|--------|------------------------|

| allios | All bidirectional pins |

|--------|------------------------|

---

|        |                                                                                          |

|--------|------------------------------------------------------------------------------------------|

| allins | All pins that can have input actions. Includes bidirectionals as well as input only pins |

|--------|------------------------------------------------------------------------------------------|

---

|         |                                                                                            |

|---------|--------------------------------------------------------------------------------------------|

| allouts | All pins that can have output actions. Includes bidirectionals as well as output only pins |

|---------|--------------------------------------------------------------------------------------------|

---

|             |                                               |

|-------------|-----------------------------------------------|

| triggerPins | Group to collectively define all trigger pins |

|-------------|-----------------------------------------------|

---

|         |                                                                                               |

|---------|-----------------------------------------------------------------------------------------------|

| Allpins | All digital pins including the trigger pins. This is used to connect and disconnect all pins. |

|---------|-----------------------------------------------------------------------------------------------|

---

|             |                            |

|-------------|----------------------------|

| allSupplies | All DPS defined power pins |

|-------------|----------------------------|

## 3.4 Source-Port-Specific Variables

The Source-Port-Specific section of the Configuration File consists of a set of definitions that define build settings specific to the selected Source Port.

### 3.4.1 IGNORE TIMEPLATE

Sometimes WGL files have timeplates that the user wants to ignore like at the start of a simulation. You can instruct Velocity to ignore these timeplates.

IGNORE TIMEPLATE timeplatename

### 3.4.2 JOB

This directive is used to enable a specific job as defined in a J750 or UltraFlex source test program. This feature is ignored for all other input ports. When used, the active spec sheets for timing and levels are picked from a specific job. If the job does not exist in the source, by a typo or any other reason, the last job is always the one that is chosen. This is also what is chosen when no JOB is defined at all. Syntax:

JOB ;jobName'

Example:

|     |         |

|-----|---------|

| JOB | QA_TEST |

|-----|---------|

### 3.4.3 MACROSTYLE

This variable will allow you to tell Velocity how to interpret Macros and Procedure when loading STIL simulation files. Depending on the way these are created variables to pass values into subroutines will either be passed through STIL Macros or with STIL procedures. It will be one or the other but not both. By default these are done with Macros. Therefore, therefore the default value for this flag is "1". But, if your source STIL files pass variables into procedures instead, you can handle this by disabling the passed variable usage in the macros by setting the MACROSTYLE flag to "0"

Syntax:

MACROSTYLE 0|1

Example:

|            |                                                      |

|------------|------------------------------------------------------|

| MACROSTYLE | 0 # Procedures pass variables                        |

| MACROSTYLE | 1 # Macros pass variables (This is default behavior) |

IEEE STIL is a very richly defined language. There are quite a few variations and these are not always compatible with one another. If you translate a STIL pattern and see scrambled data or experience a crash, it is very often because the MACROSTYLE variable is backward. In most cases, there will be header information that tells Velocity where the file was generated which will then allow Velocity to self determine the proper MACROSTYLE. But, sometimes hand generated STIL will not have the necessary header information. That is why this variable is present. It allows you to tune the STIL translations accordingly.

#### 3.4.4 MASTER

When using any of the EVCD format, there may be places where the state characters that are used indicate that the bench and the DUT are both driving. If not specified, Velocity will take the DUT as the master. That means that the competing drive values will result in the DUT value being used instead of the bench. If you specify the bench as the master, the opposite will occur. EVCD state characters of “0” or “1” will then be assumed to be tester drives instead of tester strobe values.

Syntax:

MASTER DUT|BENCH|CONFLICT

Example:

|        |       |

|--------|-------|

| MASTER | DUT   |

| MASTER | BENCH |

#### 3.4.5 PERSISTENCE

By default, a very small portion of a VCD file is used to evaluate the pins and calculate periods. Sometimes this is insufficient when multiple time domains are active. One domain may start toggling later than another. For this reason, there may not be enough actions in one domain to properly calculate a period. If this is the case, the user will receive a message that informs them that PERIOD values for one domain will track with the other. If this is undesired there is a secondary calculation scheme that might work. This is called “PERSISTENCE” mode. If enabled, a much larger page size will be used to calculate periods.

This is disabled by default, but can be explicitly assigned with the following syntax.

Syntax:

PERSISTENCE ON|OFF

Example:

```

PERSISTENCE ON  # persistence is enabled

```

```

PERSISTENCE OFF # persistence is disabled

```

### 3.4.6 SYNC

SYNC will allow Velocity to tune itself to a given timestamp before it will start handling the calculations for defining periods for VCD/EVCD translations. In certain instances, simulations will have multiple data rates present in different domains. If the simulation is very large it may require a very large amount of one domain to be processed before the second domain begins to toggle.

The SYNC variable will essentially fast forward the self discovery algorithm to focus on a particular area of the simulation. This can speed the translation greatly for large simulations.

The SYNC point defaults to time zero unless overridden by the variable which is defined in units of time. Nanoseconds (ns) are used if no unit is specified. Units can be used as well

Syntax:

```

SYNC timeValue[unit]

```

Example:

```

SYNC      1000  # SYNC period discovery to 1000ns

```

```

SYNC      5.52ms # SYNC period discovery to 5.32ms

```

### 3.4.7 UNDERSAMPLE

This allows you to apply a global value that will block strobes except in cycles with a clean modulus to whatever is specified here. When OFF, all cycles are strobed.

Syntax

```

UNDERSAMPLE  ON|OFF

```

Examples:

```

UNDERSAMPLE  OFF  # No under-sampling

```

```

UNDERSAMPLE  5   # Under sample by a factor of 5

```

### 3.4.8 OVERSAMPLE

This allows you to apply a domain specific value that will allow oversampling to be used. This is a good way to handle slow asynchronous behavior or to automatically insert oversampled strobing if edge placements are not deterministic in the source format. This applies only to VCD/EVCD. Other formats will ignore this feature

The oversample value is applied only if self discovered timing is used for VCD/EVCD translation. The calculated period would then be divided by the oversample value to give a faster (oversampled) cycle period

## Syntax

**OVERSAMPLE** domainName value

### Examples:

```

OVERSAMPLE default 10 # undersampling the default domain by a factor of 10

OVERSAMPLE I2C 10 # Under I2C domain by a factor or 10

```

## 3.4.9 VCDPAGE

This allows you indirectly control the size of pages that are used during a VCD translation. The value is in percentage. This default to 100% but you can increase or decrease the page size depending on this value. This is used to limit the size of loops when made smaller or remove page boundary issues by making the page larger.

The default page value is 100%. The page is then calculated based upon the number of pins and the density of activity. This is not something that is specifically controlled to a fixed value. This is a general property that can be used to give you larger or smaller page sizes relative to the base.

## Syntax

**VCDPAGE** value

### Examples:

```

VCDPAGE 10 # Use smaller page

VCDPAGE 500 # Use larger page

```

### 3.4.10 SAMPLE

Sample provides a way to tell the VCD/EVCD loader how to build waveforms relative to the calculated or pre-defined PERIOD for each time domain. By default, the entire set of actions within each tiled cycle will be turned into a waveform which contains all of the actions. Those actions will then be assigned to a state character that will be used to reference that waveform.

If there are multiple actions within a cycle then that waveform will include all of those actions unless the default behavior is overridden to give a different representation.

The available actions can be used to tell Velocity to build a waveform based on all of the actions, the initial action, the last action, one ‘primary’ action, or the action at a particular location within that cycle by percentage

SAMPLE AUTO

SAMPLE SINGLE

SAMPLE BEFORE

SAMPLE AFTER

SAMPLE 90%

NOTE: The best way to think about the argument of SAMPLE is to apply meaning based on what the desired interpretation of OUTPUT actions should be. Inputs will retain their pulsing waveforms. But, outputs can be filtered using the value of SAMPLE. i.e. Strobe before and edge. Strobe after an edge. Strobe in the middle of a cycle. Strobe BOTH edges of a clock pulse etc...

## 3.5 Target-Port-Specific Variables

The Target-Port-Specific section of the Configuration File consists of a set of definitions that define build settings specific to the selected Target Port.

### 3.5.1 BINARY

Compilation to the 93K will result in a pattern master file as well as a merged binary file. If you wish to include statistics in the compilation then you’ll need to create the concatenated BINL file as well. This is enabled by turning BINL “ON”

Syntax:

BINARY ON|OFF

Example:

```

BINARY      ON  # merged BINL will be created

```

```

BINARY      OFF # Only PMFL will be created

```

### 3.5.2 COMBINATION

Velocity dynamically builds a combination file base on your XMODE state. If the user want to tell Velocity to use a specific combination file, here is the syntax. This is specific to the 93K testers.

Additionally, there are arguments to explicitly provide the MINIMUM number of combinations. By specifying MINIMUM, the resulting timing will contain ONLY those waveforms that are explicitly used. There will be none that are added for debug or online editing purposes.

If MAXIMUM is specified, there will be additional waveforms added that are logically similar to the ones that are used already. That is if an edge drives 0, then it will also have a waveform to drive 1, even if these never occurs in the source. It is logically reasonable to add both. Similarly, if a strobe is present on a given edge, both strobes high and low as well as the X will be used as valid combinations. MAXIMUM is the default value for this variable

If very large simulations are used, then evaluation of the results can be limited to a predefined number of cycles. For example if you have a long scan test, you don't necessarily need to evaluate the entire file before concluding on which combinations are needed. By using a number for this value, a cycle limit will be applied for evaluating the required combinations

Syntax:

COMBINATION filename|MINIMUM|MAXIMUM|number

Example:

```

COMBINATION      /home/demo/device/ACT74.cmb

COMBINATION      ACT74.cmb # This will look alongside the CFG file

COMBINATION      MAXIMUM    # combinations will be calculated and logically #      similar states

#      will be inserted automatically

#      for debug purposes

COMBINATION      MINIMUM    # combinations will be calculated and logically #      Only those

#      states that are used by each

#      pattern and pin will be used. Smallest wave #      table possible will be created for

debug           #      purposes

```

### 3.5.3 CONTEXT

There are certain instances where different configurations of a chip require the 93K pin types to be defined differently for different modes of operation. This can be accomplished by defined the “CONTEXT” of the PINLIST block directly. If not specified, the context will be defined as

default. The Velocit CFG can assign the value to any string. Once this is done, any patterns, timing, and even levels that are created will be associated with that context only.

You can then add the extra context to the 93K pin file that you use for loading

Syntax:

CONTEXT contextName

Example:

|         |            |

|---------|------------|

| CONTEXT | inputMode  |

| CONTEXT | outputMode |

### 3.5.4 CONFIGURATION (PIN FILE)

This variable allows for a pre-defined 93K pin file to be referenced in the Velocity generated testflow instead of the auto-generated one that is used for compilation. If nothing is specified for this variable, then the pin file used by the testflow will be auto created from the PINLIST block of the CFG. Using this variable to reference pre-defined pins file is useful if you are applying patterns to an existing program where you have created you want to use multi-site, have analog pins, have relay setups defined, or certain power supply types.

There are a number of 93K pin file features that do not work when used with the pattern compiler. Multi-Site and Analog setups are two such features. The CONFIGURATION variable allows you to export to an existing test program directory without touching the pin file that is already in use.

It must be known that the pin list of the pre-defined CFG is compatible with the PINLIST generated for compilation. If this is strictly maintained then any binary pattern and timing will automatically work the pre-defined file.

|               |                                                    |

|---------------|----------------------------------------------------|

| CONFIGURATION | myCfgName # testflow will use pre-defined pin file |

|---------------|----------------------------------------------------|

### 3.5.5 CTIM

This variable will control whether or not timeset switching is allowed or not for the V93K. By default, the Virtual Timesets will be used. This means that the patterns will be created in such a way that slower ports are expressed as multiples of the faster ports, so that the DUT sees the period switching without the ATE having to physically change a timing resource in order to change the period. Period switching is disabled because this will result in either very long run times due to break cycles or will result in timing that is too large to compile. But, there are situations where this is the correct usage. So, this variable is present to enable such actions on the system

Syntax:

---

CTIM ON|OFF|VIRTUAL

### Examples

```

CTIM ON

CTIM OFF

```

## 3.5.6 DOMAIN TRACKING

Domain tracker allows you to specify the timing relationship between ports. In the following example the device has three well defined ports: 1. CLOCK, 2. DDR and 3. SDR

### Syntax:

```

DOMAIN

domainName  MASTER|TRACK [MasterDomainName [periodMultiple]]

```

where,

domainName: matches domains defined in PINLIST block

MASTER|TRACK: determines whether the period is defined itself or dependent on another domain

MasterDomainName: If specified as a TRACK, then this will refer to another port already defined as master

periodMultiple: defaults to 1.0, If other, then the current domain will track with the MASTER at the given period multiplier Example:

```

DOMAIN

CLOCK  MASTER # PortName  MASTER(Reference)

DDR    TRACK  CLOCK 1.0 # PortName TRACK Port2Track Ratio

SDR    TRACK  CLOCK 75 # PortName TRACK Port2Track Ratio

END DOMAIN

```

## 3.5.7 FAMILY

Port names for Advantest 93K are defined with the DOMAIN column of the PINLIST. In ST8, each sub group of patterns can have its own group definitions. If there are 2 different groups of patterns that have port names that are the same, it is allowable to have the contents be different. The port/group definitions are essentially sequestered to a namespace defined by the CFG's PROGRAM variable. You can

have different PROGRAM variable redefined the content of commonly named DOMAINs without any issue.

In ST7, there is one and only one Pin File and the ports/Domains are all defined in that in one space. For that reason, port names need to be unique as you go from pattern group to pattern group. The contents of ports can't change

To account for this in ST7, the FAMILILY variable can be applied with essentially creates a unique suffix for the port names that will be created. The SUFFIX variable is available so that the same patterns can be created in 2 different setups where the SUFFIX is added to the loaded pattern name. In similar fashion, the FAMILY is applied ass a suffix to the portnames in order that the DOMAIN names can be reused from CFG to CFG. The resulting ports will be marked uniquely.

EXAMPLE:

### 3.5.8 FASTMODE

This directive is used to enable or disable the use of Fastmode. Fastmode is an Advantest digital option that uses a software programmable switch to enable faster drivers. When this mode is used, special care will be taken in how the timing is exported. All pins that are set to toggle at a rate that is faster than 1.25ns will be set to use the FAST option. Data bit rates and all compilation and tester file options will automatically be adjusted. If nothing is specified, then this option is assumed to be OFF.

Syntax:

FAST ON|OFF

Example:

|      |    |

|------|----|

| FAST | ON |

|------|----|

### 3.5.9 FSPINS

This block specifically applies to the SmartScale series of cards for the Advantest V93000 tester. These channels have a property that allows the Z edges to be handled independently from the drive edges. This features allows for a zero turn around time setup for bi-directional pins. If any target other than V9300 coupled with a MODEL definition of PS6800 is used, then this block will be ignored.

Syntax:

```

FSPINS

pinName1|groupName1

pinName2|groupName2

...

pinNameN|groupNameN

END FSPINS

```

This blocks serves as a container for a list of pins or groups that should be setup with timing in such a way that the drive and Z edges are separated. Any pin left off this list will be treated as a regular IO pin instead of a FAST IO pin.

Example:

|        |    |                |

|--------|----|----------------|

| FSPINS | DQ | MQ COMBINATION |

|--------|----|----------------|

### 3.5.10 MEMORY

Compilation to the 93K can be done using Vector Memory or Sequencer Memory. By default, vector memory is used. If you want to only use sequencer memory you can override using this directive .

Syntax:

MEMORY SM|VM|SHMEM

Example:

|        |       |                         |

|--------|-------|-------------------------|

| MEMORY | SM    | # sequencer memory      |

| MEMORY | VM    | # vector memory         |

| MEMORY | SHMEM | # shared memory enabled |

### 3.5.11 METHOD

Specific to the Advantest 83K and 93K ports.) Specifies the type of test method to be used: Classic (CTM) or Universal (UTM). Used for generating the appropriate format for the test flow file.

Syntax:

METHOD CTM|UTM

Example:

|        |     |                        |

|--------|-----|------------------------|

| METHOD | CTM | # Classic Testmethod   |

| METHOD | UTM | # Universal Testmethod |

### 3.5.12 MODEL

Syntax:

```

MODEL modelType

```

where, `modelType` is a tester model type. This Control is specific to the Advantest 83K and 93K tester ports. Valid entries are:

- F330

- C400

- P1000

- PS400

- PS800

- PS1600

- PS6800

- PS3600

- PS5000

- PSSL

Examples

```

MODEL      PS3600  # PinScale

MODEL      P1000  # Single Density 93K

MODEL      PS6800 # SmartScale

```

### 3.5.13 STATEMAP

(Specific to the Advantest 93K ports.) Specifies that the “STATEMAP” blocks should be activated in the resulting compiled timing files. This block is required if reverse compilation from binary back to ascii is desired. It is also required when using some forms of the `SCAN_TML`

Syntax:

```

STATEMAP ON|OFF

```

Examples

```

STATEMAP      ON

```

STATEMAP OFF

## 3.6 Verilog Feedback Variables

There are set of configuration commands blocks that are intended specifically to affect the export of

Verilog feedback files. These variables will have no effect on regular ATE output files. If “Enable Verilog Feedback” is not checked in the GUI or enabled from the command line, then all of these variables will simply be ignored by the Build process.

### 3.6.1 MAXDELTA Definition

When Verilog feedback is enabled, there may be instances where delta values for timestamps may be too large for the compiler that will be used. By default, the maximum delta is 400us. If a delta is larger than this it will be broken into multiple timestamps and spread.

This directive can be used to use a different value other than 400uS.

If no units are specified the number will be assumed to be in ns.

Syntax:

```

MAXDELTA value[ps|ns|us|ms|s]

```

Example:

```

MAXDELTA 200us # max delta of 200us

MAXDELTA 500000 # max delta of 500000ns

```

### 3.6.2 MODULE

This variable will define the moduleName that is to be used in the Verilog feedback files if that option is chosen. If not defined at all, the default for the moduleName variable in the testbench and EVCD files created will be “moduleName”. This allows you to tune it so that re-simulations can happen more seamlessly.

Syntax:

```

MODULE moduleName

```

Or

---

MODULE moduleName.TestBenchName.DUT\_InstanceName

Example:

|        |                      |

|--------|----------------------|

| MODULE | hx_5672              |

| MODULE | dsp_1080.DEV1080.dut |

The purpose of the two separate usage models is to provide granularity on what blocks are renamed in the resulting testbench files. By default a single string entered will rename ONLY the module name that is defined by the Verilog File.

If the 3 string setup is used the resulting testbench will use pre-defined names for all three of those properties in the Verilog testbench. The ModuleName uses the first string. The second and third strings of this variable will rename the TestBench and the DutInstance. The following screen shot highlights the three updated spots in the resulting test bench for the 3 string example above...

### 3.6.3 VERILOG Definition

When using the Verilog feedback path, testbenches can have their timings expressed in one of two ways. Sequential timing will express all timestamps as relative deltas from the previous stamp. On large simulations these numbers can end up too large for the target Verilog compiler. Parallel will express each timestamp as its wall time clock value. This can result in very large numbers that may crash. By default, parallel timing is used.

Syntax:

VERILOG ON|OFF|ALL|<number>|DYNAMIC

Example:

|         |                                                        |

|---------|--------------------------------------------------------|

| VERILOG | SEQUENTIAL # Express edges as delta from previous edge |

| VERILOG | PARALLEL # express every edge as a unique timestamp    |

### 3.6.4 WINDOW

Verilog files are always print on change. In simulations, that means that only transitions are exported as timestamps. For input actions this is simple. For output actions, the ATE versions of the same stimulus will inherently insert Z-actions before each strobe. By default, these Z actions are left out of the Verilog files. If the user wants to add these actions in the “WINDOW” variable can be used to essentially define the length of the active strobe window. If WINDOW is OFF, as it is by default, then there will be no closing actions added to close the strobe windows.

In the end, this is a more exact representation of what the ATE is doing, however, the resulting verilog files will be much larger.

Syntax:

```

WINDOW OFF|value[ps|ns|us|ms|s]

```

Example:

```

WINDOW      OFF  # no windowing off output actions

WINDOW      20ps # Use 20ps strobe window

```

### 3.6.5 FEEDBACK FILTER

Verilog feedback files will export all ATE actions in all cycles and on all pins by default. In some cases, the user may want to limit the export. This can be limited to a certain cycle range. It can be limited by certain pins. Or, you can choose to export certain pins as running clocks instead of explicit data. All of these actions are taken to limit the size and scope of testbench. FEEDBACK filter blocks can be created that can tune the Verilog scope on a pattern by pattern basis

Syntax:

```

FEEDBACK default|patternName

BASE          basename

START         BEGIN|timeStart|cycleStart

STOP          END|timeStop|cycleStop

pinName1|ALL  ON|OFF|CLK

pinName2      ON|OFF|CLK

pinName3      ON|OFF|CLK

...

pinNameN      ON|OFF|CLK

END FEEDBACK

```

default|patternName: name of feedback block. If the name is “default”, then this filter will apply to all patterns. If the name is something else, then the filter will only apply to patterns whose name matches that of the FEEDBACK block.

If the desired patternName is different than the source file, you can specify the connection to a given simulation by additionally assigning the BASE variable. If this is done, the translation will use the base Name as the simulation hat is loaded, but will export to the name specified by patternName,

**START & -STOP:** This is an optional field that can assign the start and stop location for the translations. If left off then ALL cycles will be exported. These times can be expressed in either picoseconds or as a percentage. If the “%” is used, then you can export just the segments you like as a percentage of time. It is important to realize that this percentage is relative to the time value as opposed to the physical file location.

**pinNameN|ALL:** pin name to be added as regular pin (ON), removed from Verilog files (OFF), or included in Verilog as a running clock (CLK)

Examples:

```

# Export Verilog on all cycles for all pins except data[0-2].

FEEDBACK default

ALL ON  data0 OFF

data1 OFF  data2 OFF

END FEEDBACK

# Export Verilog for patternA for the fist 25% only. Include only CLK32

# expressed as running clock and data[0-2] expressed as regular data

FEEDBACK patternA  START

BEGIN

STOP 100us  CLK32

CLK  data0

ON  data1 ON  data2

ON END FEEDBACK

```

## 3.7 General Purpose Variables

The following list of variables are ones that can be applied to any combination of Source and Target port. In some instances these variables are meant simply to provide default states for objects in the GUI. In other cases, these variables will have no analogous command line or GUI feature and will affect outputs all on their own.

### 3.7.1 COMMENT

When using any of the serial protocol formats, this variable will optionally add comments to the patterns. That will inform you of the state of the protocol as data is transmitted. These comments will also be viewable on the target system in the pattern viewers.

Syntax:

COMMENT ON|OFF|ALL|OPTIMIZED

where,

ON: comments are passed in from source. Scan instances are marked

OFF: comments are blocked

ALL: comments are used like “ON” above, but additionally, timestamp markers are included

OPTIMIZED: comments are ignored when compression is used. If a comment is within a field of cycles that can be compressed, then the comment will be swallowed and dropped.

Example:

|         |           |

|---------|-----------|

| COMMENT | ON        |

| COMMENT | OFF       |

| COMMENT | ALL       |

| COMMENT | OPTIMIZED |

### 3.7.2 DDRMODE