DE LA RECHERCHE À L'INDUSTRIE

Full 300 mm Electrical Characterization of 3D Integration Using High Aspect Ratio (10:1) Mid-Process Through Silicon Vias

F. Gaillard<sup>1</sup>, <u>T. Mourier<sup>1</sup></u>, L. Religieux<sup>3</sup>, D. Bouchu<sup>1</sup>,

C. Ribiere<sup>1</sup>, S. Minoret<sup>1</sup>, M. Gottardi<sup>1</sup>, G. Romero<sup>2</sup>,

V. Mevellec<sup>3</sup>, C. Aumont<sup>2</sup>

<sup>1</sup> CEA-Leti, <sup>2</sup> STMicroelectronics, <sup>3</sup> aveni

www.cea.fr

### Introduction

> 3D Integration and why increasing aspect ratio

## New metallization of High aspect ratio TSV

- MOCVD TiN barrier

- Electrografted seed layer : eG<sup>3D</sup>

- ✓ Characterization

- ✓ Transfer on 300 mm platform

- Integration and electrical results

- Conclusions and perspectives

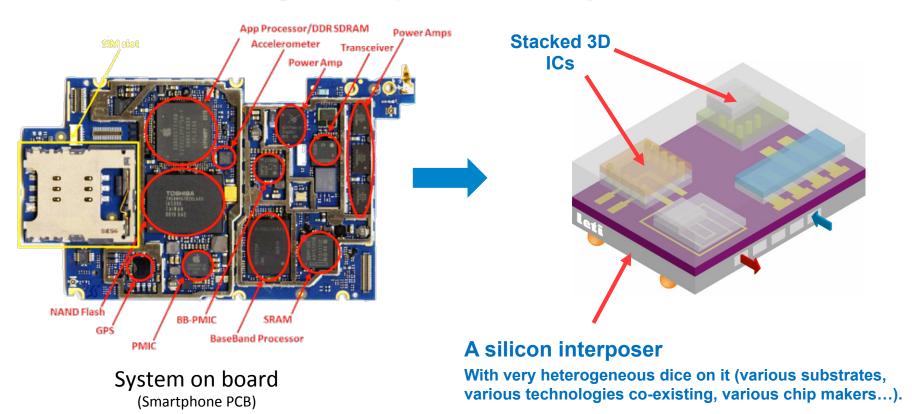

In the near future, the electronic circuit will probably be looking like this and will integrate complex electronic systems on silicon

Smaller - More Performance with higher functionalities - Cheaper

- Higher and higher aspect ratios are today forecasted

- TSV Mid-process

- > From 10x100  $\mu$ m today to 10x150  $\mu$ m or 5x80  $\mu$ m depending on application

- Where are the challenges for metallization of these TSVs?

| Barrier                | <ul> <li>Conformal deposition</li> <li>Good barrier properties for process temperature</li> </ul> |

|------------------------|---------------------------------------------------------------------------------------------------|

| Seed                   | <ul> <li>Conformal deposition, continuous on sidewalls</li> <li>Low resistance</li> </ul>         |

| Plating                | <ul> <li>Void free deposition in whole TSV</li> <li>Low overburden</li> </ul>                     |

| TMaurice EDTO 2045 204 |                                                                                                   |

# HIGH ASPECT RATIOS – ALTERNATIVE SEED LAYER

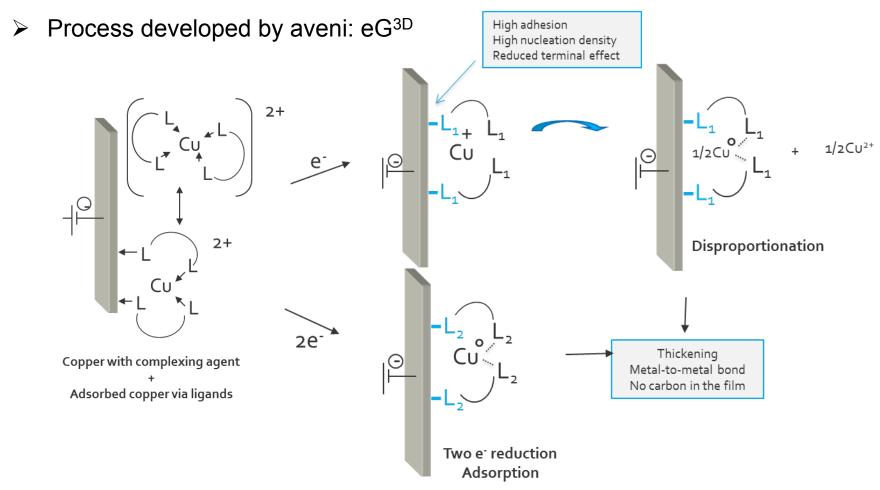

Electrografted seed layer

Can be used as a PVD seed repair or directly as DoB (Direct on Barrier)

# HIGH ASPECT RATIOS SEED LAYER – eG<sup>3D</sup>

#### Transfer to 300 mm scale

Copper filling

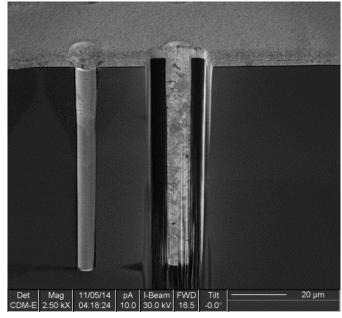

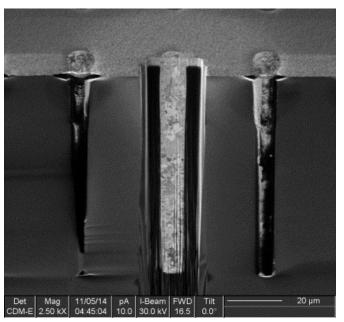

10x100 µm TSVs filled with the 2 selected options: seed repair or direct on barrier seed

PVD barrier + Cu seed layer + eG<sup>3D</sup> repair process

MOCVD TiN barrier + Cu seed flash + eG<sup>3D</sup> seed layer process

#### Void free filling obtained on both metallization options

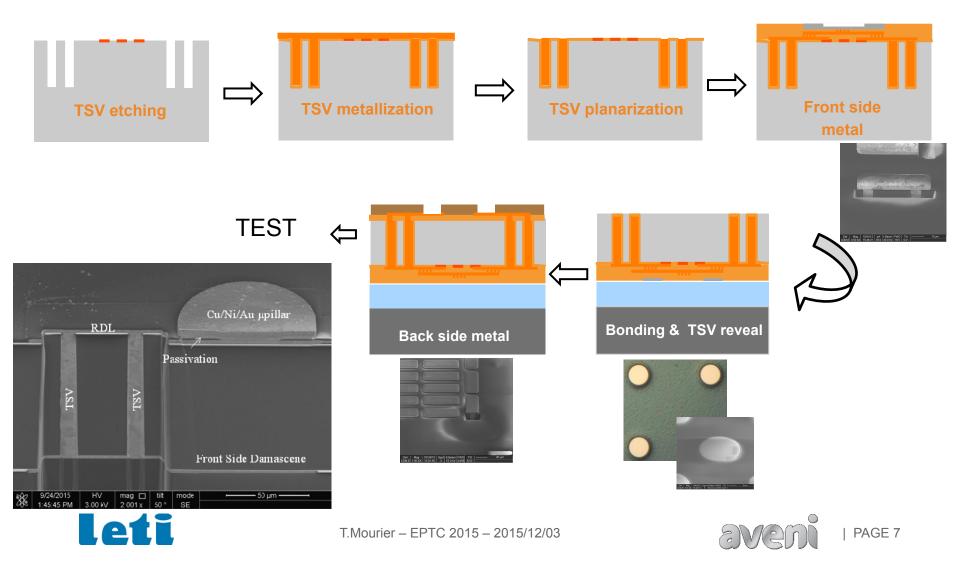

#### Complete integration was performed using TSV mid process flow

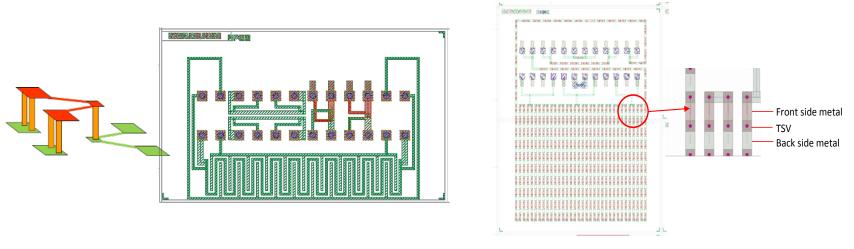

#### Test structure : Kelvins and daisy chains

10x100 µm Kelvin TSV

10x100  $\mu m$  : 2 to 754 TSVs Daisy Chain

#### Metallization splits for comparison

Split 1 : PVD barrier/seed repair option

Split 2 : MOCVD TiN barrier/seed repair option

Split 3 : MOCVD barrier/Flash PVD Cu/eG3D seed layer

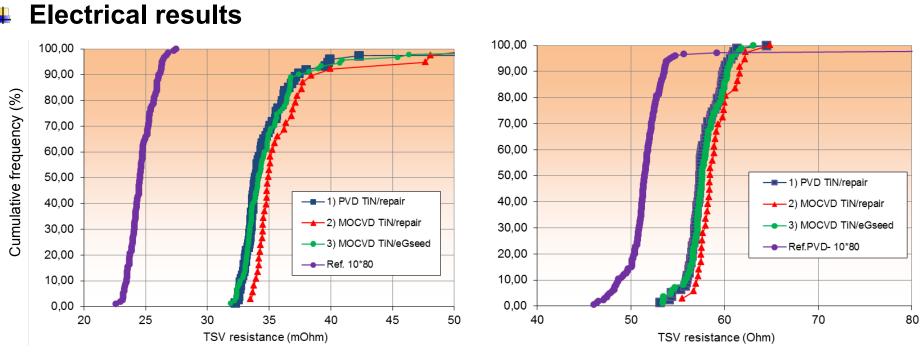

10 x 100 µm - Kelvin TSV

INTEGRATION

10 x 100 µm - 754 TSV daisy chain

- Excellent yield whatever metallization conditions

- Sharp distribution

- No clear difference between the splits

- Same distribution as 10x80 µm full PVD reference, difference is due to TSV height

#### Process extendibility to higher TSV

> Same process was applied to 12:1 aspect ratio TSV (10 x 120  $\mu$ m)

Option 2 MOCVD TiN – Flash Cu PVD 200 nm -200 nm eG<sup>3D</sup> seed

- Both presented metallization options are extendible to 12:1 aspect ratio

## CONCLUSIONS

- A new metallization process has been demonstrated enabling copper filling of high aspect ratio TSV based on :

- A low temperature MOCVD TiN barrier material

- An Electrografted seed layer that can be used in stand alone or as a seed repair option

- Process development was performed and transferred on a 300 mm platform

- Electrical integration was realized showing no degradation of TSV performances compared to reference iPVD metallization

- Extendibility of this process for higher aspect ratio has been demonstrated and integration is on going on 12:1 AR

- Adhesion is still under investigation through process and hardware optimization to remove the copper flash PVD

I would like to acknowledge :

- The 300 mm plating team

- People working on integration on the 300 mm 3D pilot line

- aveni process team

- Fabienne Allain for the electrical measurements

# Thank you for your attention

Grenoble - France