# C-Cube Processor Applications Programming Interface (API)

Reference Guide

DVXPRESS/DVXPERT Technical Document Library

This document is preliminary. We expect to update this document as we receive feedback from users of the product. Contact C-Cube Microsystems for a full design review before beginning design work.

C-Cube Microsystems Inc. reserves the right to change any products described herein at any time and without notice. C-Cube Microsystems assumes no responsibility or liability arising from the use of the products described herein, except as expressly agreed to in writing by C-Cube Microsystems. The use and purchase of this product does not convey a license under any patent rights, copyrights, trademark rights, or any other intellectual property rights of C-Cube Microsystems.

#### **Trademark Acknowledgment:**

C-Cube and the corporate logo are registered trademarks of C-Cube Microsystems. All other trademarks are the property of their respective companies.

© 1997 by C-Cube Microsystems Inc. All rights reserved.

#### **Customer Support and Feedback:**

To receive product literature or technical support, contact us at

C-Cube Microsystems 1778 McCarthy Boulevard Milpitas, CA 95035 Telephone: (408) 944-6300

Fax: (408) 944-6314 E-mail: support@c-cube.com http://www.c-cube.com

C-Cube Part # 92-5API-101 PRELIMINARY November 17, 1997

# **Preface**

This document is the primary source of technical information about the Processor's Applications Programming Interface (API).

#### This manual is intended for:

**Audience**

- System designers and managers who are evaluating the Processor's API.

- Programmers and software engineers who are writing application programs that interact with the Processor.

This manual is divided into seven chapters. See the table of contents for more details.

**Organization**

# **Conventions**

Please note the following notation examples and conventions that are used in this manual:

| Examples/<br>Conventions | Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x1C3                    | "0x" prefix indicates a hexadecimal number.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 11011 <sub>2</sub>       | "2" subscript indicates a binary number.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| VIE, Res                 | Italicized acronyms or abbreviations (initial or all caps) indicate bit field names within registers or data words.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| RESERVED or Res          | Indicates bit fields within registers that are not defined. These bits are used by the internal microcode, and modifying these bits should be done cautiously. If the register is modified during operation, the host should perform a Read-Modify-Write operation to preserve the state of the reserved bits. Writing the incorrect value to a RESERVED register bit causes indeterminate behavior. In addition, all registers and configuration parameters in DRAM that are not explicitly given names are also RESERVED, and accessing these registers may cause indeterminate results on current or future implementations. |  |

| Byte ordering            | Unless otherwise stated, all byte ordering in the <product_name> is bigendian: byte 0 is always the most significant (leftmost) byte.</product_name>                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Top, bottom<br>field     | This manual uses the MPEG standard terms "top" and "bottom" to refer to the video fields. The top field can also be referred to as the first, or the even field. The bottom field can also be referred to as the second, or the odd field.                                                                                                                                                                                                                                                                                                                                                                                      |  |

| MSB, LSB                 | Most significant byte, least significant byte.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

# **Contents**

# 1 Overview

| 011 |       | •                                          |    |

|-----|-------|--------------------------------------------|----|

| 1.1 | Feat  | ures                                       | 3  |

| 1.2 | Micro | ocode Download and Start-up                | 4  |

|     | 1.2.1 | Microcode File Format                      | 4  |

|     | 1.2.2 | Shared Memory Initialization               | 10 |

|     | 1.2.3 | Microcode Start Mode Flag                  | 11 |

|     | 1.2.4 | Microcode Status Location                  | 12 |

|     | 1.2.5 | Two-Chip Processor Loading Protocol        | 13 |

| 1.3 | Com   | munication Process                         | 15 |

|     | 1.3.1 | Sequence Numbers                           | 17 |

|     | 1.3.2 | Command Block Format                       | 18 |

|     | 1.3.3 | Message Block Format                       | 19 |

|     | 1.3.4 | Communication Initialization and Bootstrap | 20 |

|     | 1.3.5 | Error Recovery                             | 22 |

|     | 1.3.6 | Sample Communication Sequence              | 24 |

| 1.4 | Appli | cation Models                              | 25 |

|     | 1.4.1 | Interrupt-Driven Model                     | 25 |

|     | 1 4 2 | Polled-Mode Model                          | 28 |

| 2 | Con | nmands                                          |    |

|---|-----|-------------------------------------------------|----|

|   | 2.1 | Command Syntax                                  | 32 |

|   |     | Command Types                                   | 33 |

|   | 2.3 | Scheduled Command Execution                     | 34 |

|   |     | 2.3.1 Timecodes Format                          | 34 |

|   |     | 2.3.2 Command Queue Buffer Management           | 34 |

|   |     | 2.3.3 Timecode Wrap-Around and Expired Commands | 35 |

|   |     | 2.3.4 Escape Timecode                           | 35 |

|   |     | 2.3.5 Illegal Timecodes                         | 36 |

|   | 2.4 | Priority Command Execution                      | 36 |

|   | 2.5 | Command Execution Errors                        | 37 |

| 3 | Me  | ssages                                          |    |

|   | 3.1 | Message Format                                  | 40 |

|   | 3.2 | Message Types                                   | 40 |

|   |     | 3.2.1 Initialization Message                    | 41 |

|   |     | 3.2.2 Command Buffer Status Message             | 42 |

|   |     | 3.2.3 Error Messages                            | 43 |

| 4 | Dat | a Stream Input and Output                       |    |

|   | 4.1 | Protocol A Data Stream I/O                      | 47 |

|   |     | 4.1.1 Protocol A Data Stream Loading            | 48 |

|   |     | 4.1.2 Protocol A Data Stream Storing            | 49 |

|   | 4.2 | Protocol B Data Stream I/O                      | 51 |

|   |     | 4.2.1 Protocol B Data Stream Loading            | 51 |

|   |     | 4.2.2 Protocol B Data Stream Storing            | 53 |

| 5 | 0th | er Data Interfaces                              |    |

|   | 5.1 | Picture Input/Output Interface                  | 56 |

|   |     | 5.1.1 Command Format                            | 57 |

|   |     | 5.1.2 Data Format                               | 60 |

|   | 5.2 | Serial Interface                                | 63 |

|   |     | 5.2.1 Initialization Memory Format              | 63 |

|   |     | 5.2.2 Serial Interface Command Format           | 65 |

|   | 5.3 | Context Switch                                  | 68 |

| 6 S | stem Timing                                |    |

|-----|--------------------------------------------|----|

| 6.  | Overview                                   | 72 |

| 6.  | Timing                                     | 73 |

|     | 6.2.1 Command Timing                       | 73 |

|     | 6.2.2 Message Timing                       | 73 |

|     | 6.2.3 Encode Bitstream Timing              | 74 |

|     | 6.2.4 Decode Bitstream Timing              | 74 |

| 6.  | System Clock Reference                     | 75 |

| 7 A | dio I/O Configuration                      |    |

| 7.  | Audio Processing Overview                  | 78 |

| 7.  | Audio Frame Formats                        | 79 |

| 7.  | Audio Configuration Interfaces             | 83 |

|     | 7.3.1 Audio Configuration Command          | 83 |

|     | 7.3.2 Audio Status In_0/1 Registers        | 85 |

|     | 7.3.3 Audio Status Out Register            | 86 |

| 7.  | Audio Block Format                         | 86 |

| Cu  | tomer Feedback                             |    |

| No  | th American Representatives                |    |

| Int | rnational Representatives and Distributors |    |

| C-  | ube Microsystems Sales Offices             |    |

| Inc | <b>2X</b>                                  |    |

| 1-1 | General Dual-DV <sup>x</sup> Processor System | 13 |

|-----|-----------------------------------------------|----|

| 1-2 | Typical Interrupt-Driven Host Application     | 27 |

| 1-3 | Typical Polled-Mode Host Application          | 29 |

| 6-1 | Host Interface Timing                         | 72 |

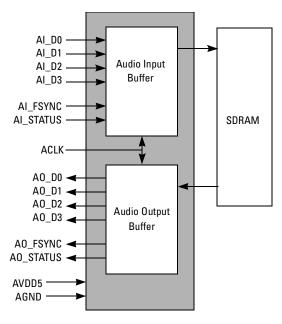

| 7-1 | DV <sup>x</sup> Audio Interface Block Diagram | 79 |

# **Tables**

| 1-1  | C-Cube Proprietary .ux File FormatInitial Header  | 5  |

|------|---------------------------------------------------|----|

| 1-2  | C-Cube Proprietary .ux File Format Section        | 6  |

| 1-3  | C-Cube Proprietary .ux File FormatExtended Header | 8  |

| 1-4  | Shared Memory Contents                            | 10 |

| 1-5  | Microcode Status Register                         | 12 |

| 1-6  | Loader Command Word                               | 13 |

| 1-7  | Loader State Words                                | 14 |

| 1-8  | Command Block Format                              | 18 |

| 1-9  | Message Block Format                              | 20 |

| 1-10 | Sample Communication Sequence                     | 24 |

| 2-1  | Scheduled Command Syntax                          | 32 |

| 2-2  | Priority Command Syntax                           | 32 |

| 2-3  | Command Types                                     | 33 |

| 3-1  | Outgoing Message Format                           | 40 |

| 3-2  | Message Types                                     | 40 |

| 3-3  | Initialization Message                            | 41 |

| 3-4  | Command Buffer Status Message                     | 42 |

| 3-5  | Error Message                                     | 43 |

| 3-6  | Common Error Sub-Types                            | 43 |

| 4-1  | Init Data Stream I/O Command                      | 47 |

| 4-2  | Protocol A Load Data Stream Command Format        | 48 |

| 4-3  | Protocol A Load Data Stream Message Format        | 49 |

| 4-4  | Protocol A Store Data Stream Command Format       | 50 |

| 4-5  | Protocol A Store Data Stream Message Format       | 50 |

| 4-6  | Protocol B Load Data Stream Command Format        | 51 |

| 4-7  | Protocol B Load Data Stream Message Format        | 52 |

| 4-8  | Protocol B Store Data Stream Command Format       | 53 |

| 4-9 | Protocol B Store Data Stream Message Format   | 53 |

|-----|-----------------------------------------------|----|

| 5-1 | Start Picture I/O Command Format              | 57 |

| 5-2 | Stop Picture I/O Command Format               | 59 |

| 5-3 | Picture I/O Data Format                       | 61 |

| 5-4 | Serial Interface Initialization Memory Format | 64 |

| 5-5 | Serial Interface Command Format               | 66 |

| 5-6 | Serial Interface Message Format               | 67 |

| 5-7 | Context Switch Command Format                 | 68 |

| 5-8 | Context Switch Message Format                 | 69 |

| 6-1 | Variables for Setting the PTS Counter         | 75 |

| 7-1 | Supported Audio Formats                       | 79 |

| 7-2 | Audio Frame Format                            | 80 |

| 7-3 | Processor I/O Operations                      | 81 |

| 7-4 | FRFORM 1 Timing References                    | 82 |

| 7-5 | Audio Configuration Command Parameters        | 83 |

| 7-6 | Audio Block Format                            | 86 |

# 1 Overview

The C-Cube Processor<sup>1</sup> is an integrated circuit that encodes and decodes MPEG-2 data and other digital video formats. It is optimized for use in computers with an internal Peripheral Component Interconnect (PCI) bus. It has a scalable platform architecture that efficiently implements motion-compensated block/DCT-based video compression algorithms in real time.

The processor is a compelling platform for MPEG encoders, decoders and codecs. It can be used as a 4:2:2 profile encoder and decoder, ML@MP encoder, SIF encoder, and simple profile codec. Because of its versatility, it is likely that the system designer might want to use the processor in several different products. To enable this, C-Cube provides a common Application Programming Interface (API) across the several processor-based products. The common API not only reduces support

<sup>1.</sup> The term "processor" or "the processor" is used from now on.

requirements and time-to-market, but also allows code re-use and easier maintenance.

For any processor-based product, the specific product API contains the proper mix of commands derived from the common API and whatever additional commands might be required by the specific microcode product.

This document describes the basic protocol for communicating control and status information between the host and all processor microcode products. The protocol elements common to all processor products include chip initialization, software downloading, command and message formats, management of command and message buffers, bitstream I/O, picture I/O, and other relevant information.

Although not all features described here are supported in all products, supported features must adhere to the API protocol. Refer to the product-specific documentation to determine the features that any particular microcode product supports.

## 1.1 **Features**

The processor Application Programmer Interface (API) provides these features:

- All processor-based products support a standard microcode format and use the same start-up procedure.

- The processor controls all PCI traffic except for the initial shared memory accesses, microcode downloading, and PTS counter (processor internal system time clock) updates.

- The processor accesses the host using ping-ponged "command" blocks.

- The processor sends status to the host via ping-ponged "message" blocks.

- "Sequence numbers," attached to each command and message block, maintain communication synchronization.

- Regardless of the number of chips in the product, the host always communicates with the *master* processor.

- After command parsing is complete, error checking is always done.

- All commands have a similar format:

<timecode><type><tc ID><stream ID><size><data payload> The amount and format of the data payload varies appropriately for the given command.

# 1.2 Microcode Download and Start-up

This section describes the elements involved in downloading, initializing, and executing the microcode on the processor. These include microcode file format, shared memory initialization, state retrieval for context switches, and processor status values. For those customers using two processors in a master-slave configuration, we also describe the two-chip microcode loading protocol.

#### 1.2.1 Microcode File Format

The processor's microcode consists of two files. The first file uses the Intel Code 99 "hex" format. This file contains the default data pattern that is programmed into the serial EPROM connected to the processor's PCI interface when a serial EPROM is used.

The second file is the actual microcode and is formatted using our proprietary "microcode executable" (.ux) file format (Tables 1-1 through 1-3).

The .ux file contains the instructions that initialize the processor's memory for getting the microcode loaded and running and for enabling the host to receive commands (see note below). The host needs only to understand the simple syntax elements contained in the .ux file and to handle a few types of data transfers under host control. This feature eliminates the need for complex host software to implement reset routines. Also, it eliminates the need to maintain different loaders for different processor-based products.

#### Note:

There are some minor host initializations, which are not included in the .ux file and need to be addressed explicitly by the host, because they involve pointers to host buffers. These are covered in other parts of this document.

The .ux format file has three primary regions:

1. At the beginning of the file, a very simple header with a magic number and the length of the released portion of the file. This header contains the minimum information necessary to load the microcode. See Table 1-1.

Table 1-1 C-Cube Proprietary .ux File Format --Initial Header

| Initial Header                        |                                                                                                                                                                                                                                                                                                                    |  |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| File Element                          | Definition                                                                                                                                                                                                                                                                                                         |  |

| ■ Magic number (32 bits)              | This is the 4-byte sequence 0x43, 0x33, 0x55, 0x58, which is equivalent to the ASCII string "C3UX" (without null termination).                                                                                                                                                                                     |  |

| ■ Number of sections (32 bits)        | This is the total number of "Sections" (defined on the next page) contained in the file. This is a little-endian number (the first byte in the file is the least significant).                                                                                                                                     |  |

| ■ Length of initial portion (32 bits) | The length of the initial portion is the length of that part of the file which is always distributed to customers. This is specified as a number of bytes and is a little-endian number. Optional information may be present at the end of the file beyond this length, but it is not needed for normal operation. |  |

2. The *main region* of the file follows and it carries one or more code sections. Each section specifies a certain portion of memory initialization, either of SDRAM or of one of the CBUS registers. Together, the sections in this main region supply the steps for microcode start-up.

Each section contains part of the microcode that is to be loaded into a contiguous section of the processor's memories. All sections must be contiguous within the file and occur between the initial header and the extended header. Data from each section must be loaded to the processor in the same order they occur in the file. See Table 1-2.

Table 1-2 **C-Cube Proprietary .ux File Format --Section**

| Section               |                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| File Element          | Definition                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Data type<br>(8 bits) | This is the type of memory space in which this Section loads. The predetermined values are:                                                                                                                                                                                                                                                                                                       |  |

|                       | 0 SDRAM                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Flags<br>(8 bits)     | <ul> <li>1 CBUS</li> <li>Bit 0: Ignore Checksum. This bit is set by the microcode linker for only those Sections intended for customer modification. It should not be modified by customers. If zero, the checksum (see below) for this Section is valid.</li> </ul>                                                                                                                              |  |

|                       | If <i>one</i> , it is invalid and should be ignored by the microcode loader.                                                                                                                                                                                                                                                                                                                      |  |

|                       | ■ Bit 1 and 2: Section Format.                                                                                                                                                                                                                                                                                                                                                                    |  |

|                       | If <i>zero</i> , the Section data is a block of data loaded at the Section start address.                                                                                                                                                                                                                                                                                                         |  |

|                       | If one, the Section data consists of address and data pairs, where the address is a 32-bit big-endian quantity, and the data format varies based on the data type. The loader determines how many bits of each quantity are valid according to the data type. If the data type is 1 (i.e. CBUS), the data is one big-endian 32-bit word. If the data type is 0 (i.e SDRAM), the data is one byte. |  |

|                       | Processor PCI target mode allows only data transfers in 32-<br>bit-word multiples. Thus, the host has to read 32 bits, mask<br>out 3 bytes and write 32 bits back to SDRAM.                                                                                                                                                                                                                       |  |

|                       | If <i>two</i> , the section data will have a valid big-endian address in the section header, and must contain exactly one byte. When this of type section is encountered, the loader will loop indefinitely, checking the current value of the memory byte at the address while it is not equal to the value of the section data byte.                                                            |  |

|                       | If <i>three</i> , the section is a big endian 32-bit value specifying a minimum number of microseconds for the loader to wait before proceeding. The section start field is unused.  Bits 3-7: unused (will be 0).                                                                                                                                                                                |  |

| Section (Continued)           |                                                                                                                                                                                                                                                                                 |  |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| File Element                  | Definition                                                                                                                                                                                                                                                                      |  |

| Unused flags<br>(16 bits)     | ■ Will be 0.                                                                                                                                                                                                                                                                    |  |

| Section length<br>(32 bits)   | This is the length of this Section in bytes.                                                                                                                                                                                                                                    |  |

| Section start<br>(32 bits)    | This is the product-specific little-endian address within the selected memory space for the first data word in the segment. Other data words must be loaded sequentially at increasing addresses. If Flags[1:2] is 1 or 3, then this value is unused and will be 0 (see above). |  |

| Section checksum<br>(32 bits) | This is a simple arithmetic little-endian checksum of the Section. It is ignored by the loader if Flags[0] is 1 (see above). It is computed as the sum of each <i>byte</i> in the Section, including all fields of the header except the checksum itself.                       |  |

| Section Data                  | This variable-length field contains the data values actually written to the selected memory space (Data type). This field may contain 32-bit address values if Flags[1:2] is 1.                                                                                                 |  |

After the main region, the extended header follows. It contains 3. the copyright, microcode product and revision number information. It also provides the silicon revision information of the hardware upon which the microcode should run.

This header is distributed to customers, but is not needed for production loads of microcode. All strings are ASCII characters and are padded with zeroes. See Table 1-3.

Table 1-3 **C-Cube Proprietary .ux File Format --Extended Header**

| Extended Header                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| File Element                                                                                   | Definition                                                                                                                                                                                                                                                                                                                                                                                               |  |

| File format revision (16 bits)                                                                 | The first byte contains the minor revision code for the file format. Changes to the minor revision indicate changes only to the C-Cube private portions of a file (debugging data, below) or changes which donot affect the basic load mechanism. The second byte is the major revision for the format. The description in this table matches a major revision value of 1.                               |  |

| Microcode version number (32 bits)                                                             | ASCII string (no null termination) indicating the version number of the microcode contained in this file.                                                                                                                                                                                                                                                                                                |  |

| Microcode product name (256 bits)                                                              | Text identifying the microcode product contained in the file, such as "AFF."                                                                                                                                                                                                                                                                                                                             |  |

| Customer specific name (256 bits)                                                              | Text describing customer-specific variant, or all zeroes if none.                                                                                                                                                                                                                                                                                                                                        |  |

| Silicon product name<br>(128 bits)                                                             | Name string such as "DV <sup>K</sup> or CL5000."                                                                                                                                                                                                                                                                                                                                                         |  |

| Minimum silicon revision<br>(8 bits)<br>Maximum silicon revision<br>(8 bits)                   | This is the minimum silicon mask revision needed to run this microcode, and the maximum revision (if any) past which this microcode will not work. If there is no maximum revision field, the maximum revision is 0. Silicon revisions are encoded as four bits for the major revision (all layer change) and four bits for the minor revision (metal mask only). 0x10 represents an "A0" mask revision. |  |

| Minimum extended feature revision<br>(8 bits)<br>Maximum extended feature revision<br>(8 bits) | These are the minimum silicon revisions needed for any conditional or extended features supported by this microcode, and the maximum silicon revision needed to run all extended features supported by this microcode. The microcode will have to examine the revision itself to decide which features can be enabled.                                                                                   |  |

| Copyright string (512 bits)                                                                    | This field contains the microcode's copyright notice.                                                                                                                                                                                                                                                                                                                                                    |  |

| Header checksum<br>(32 bits)                                                                   | This is a simple arithmetic checksum of the contents of<br>the Initial header and the other fields of the Extended<br>header.                                                                                                                                                                                                                                                                            |  |

Each code section in the main region supplies:

- Memory ID number<sup>2</sup>

- Starting address

- Length

- Checksum (optional)

- There are also special sections, indicated by a flag field, that contain multiple address/data pairs to allow the data to be written to non-contiguous areas of memory, or that call for the polling of a certain location for a certain value.

A typical .ux file provides the following code groups:

- First, one or more sections containing register-writes that reset the processor

- Next, one or more sections to load the microcode itself into SDRAM

- Finally, one or more sections containing the SDRAM and registerwrites necessary to put the chip in the run state and start the execution of the microcode

In summary, to load the microcode, the host needs only to:

- Load all the data from each section following the order given by the file

- Perform some other very minor initializations as outlined in the succeeding parts of this document. The host can load SDRAM using either target-mode transactions or by manipulating the processor's control registers to cause it to perform bus-master copies between the host memory and the processor's SDRAM.

<sup>2.</sup> Indicates to the host where to write data

### 1.2.2 Shared Memory Initialization

The region of the processor's SDRAM between addresses 0x40000 and 0x4003F is reserved as *shared memory*. This region is used with the .ux file to complete various microcode initialization steps<sup>3</sup> and it needs to be initialized for the processor to run. Thus, the best time to initialize shared memory is before loading the microcode.

Table 1-4 shows the contents of memory.

Table 1-4 Shared Memory Contents

| Address              | Data                        | Description                         |

|----------------------|-----------------------------|-------------------------------------|

| 0x40000              | Even Command Buffer Address | Section 1.3.4                       |

| 0x40004              | Odd Command Buffer Address  | Section 1.3.4                       |

| 0x40008              | Even Message Buffer Address | Section 1.3.4                       |

| 0x4000C              | Odd Message Buffer Address  | Section 1.3.4                       |

| 0x40010              | Microcode Status            | Section 1.2.4                       |

| 0x40014              | Reserved                    | n/a                                 |

| 0x40018 -<br>0x40024 | PTS Counter                 | "System Clock Reference" on page 79 |

| 0x40028              | Loader Command              | Section 1.2.5                       |

| 0x4002C              | Loader State                | Section 1.2.5                       |

| 0x40030              | Microcode Start Mode Flag   | Section 1.2.3                       |

| 0x40034              | Microcode State Address     | Section 1.2.3                       |

| 0x40038 -            | Reserved                    | n/a                                 |

| 0x4003F              |                             |                                     |

The .ux file implicitly handles the Loader Command location and the Loader State location, while the processor writes the Microcode Status location (Section 1.2.4). Remaining locations in the above table must be initialized by the host. (See Table 1-4 for document references.)

<sup>3.</sup> The PTS Counter locations, however, are used throughout code execution; see "System Clock Reference" on page 79.

#### 1.2.3 Microcode Start Mode Flag

The Microcode Start Mode Flag (0x40030) and the Microcode State Address (0x40034) shared memory locations are reserved for encode/ decode context switch applications. In those applications, the processor synchronizes with data loaded through the PCI bus instead of the realtime video clock. To reduce the context switch time, the processor skips some internal initialization stages. It also preserves the previous encoder or decoder state to maintain constant picture quality. To make this possible, the processor needs to save and restore its state in order to smoothly execute the context switch and restart correctly.

The Microcode Start Mode Flag location contains two bit-flags. The first one (bit 0) controls how the processor synchronizes itself. If this bit is zero, the processor starts the microcode in the normal way, synchronizing itself with video I/O timing and operating in real time. If bit 0 is set to one, on the other hand, the processor will synchronize itself with PCI picture I/O ("Picture Input/Output Interface" on page 56) and operate in non-real-time. For context switch applications, bit 0 should be set to one; otherwise, it should be set to zero.

Bit 1 of the Microcode Start Mode Flag controls the restoration of previous processor state. If it is set to zero, the processor fully initializes itself and the Microcode State Address location is ignored. However, if bit 1 is set to one, the processor obtains previous state information from a host buffer at the address given in the Microcode State Address Location. This host buffer will have been filled by use of a Context Switch command issued before the processor was last halted ("Context Switch" on page 71).

For non-context-switch applications, bit 1 of the Microcode Start Mode Flag should always be set to zero. For context-switch applications, it should be set to zero the first time the microcode is loaded for each of the two products involved in the context switch, and set to one each time the microcode is re-loaded thereafter.

#### 1.2.4 Microcode Status Location

The Microcode Status Register, which resides in shared memory address location 0x40010, is a 32-bit word that assists the developer in the initial debugging and bring-up of the microcode and the host communication software.

Upon boot-up, the processor sets the Microcode Status Register to "Init" to reflect its starting operation. When the initialization stage is done, the status register is set to "Idle." If the initialization fails, "Error" bits are set. See Table 1-5 for a description of the 32 bits.

**Microcode Status Register** Table 1-5

| Bits | Value      | Name              | Meaning                                                                         |

|------|------------|-------------------|---------------------------------------------------------------------------------|

| 0:3  | 0          | Uninit            | Microcode hasn't started yet or didn't get to _main()                           |

|      | 1          | Init              | Processor is in the initialization process                                      |

|      | 2          | ldle              | Processor completed initialization or was running and received a "stop" command |

|      | 3          | Run               | Processor is running and performing encode or decode                            |

|      | 4          | Pause             | Processor encode/decode operation is paused                                     |

|      | 5-15       | Reserved          | Reserved                                                                        |

| 4:7  | 0          | No Error          | No Error                                                                        |

|      | 1          | Error 0           | Checksum failure detected in init routine                                       |

|      | 2          | Error 1           | Communication protocol failure detected                                         |

|      | 3-15       | Error2<br>Error14 | Reserved                                                                        |

| 8:31 | 0-0xFFFFFF | Reserved          | Reserved                                                                        |

### 1.2.5 Two-Chip Processor Loading Protocol

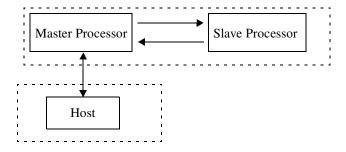

Figure 1-1 shows a dual processor implementation. In this two-chip system, the host accesses the secondary (slave) chip through the primary (master) chip. The host is not burdened with the two-chip processor loading protocol because it is handled by the .ux file syntax.

We describe the two-chip loading protocol here. This information might be useful if a customer finds it necessary to debug the start-up process.

Figure 1-1 **General Dual Processor System**

In a two-chip system, the .ux file is set up as follows:

- 1. The host loads the slave's microcode onto the master chip.

- 2. The host sets the shared memory Loader Command word at address 0x40028 to "kLoad Slave uCode," which instructs the master chip to transfer the code to the slave chip (Table 1-6.)

| Table 1-6 | Loader ( | Command | Word |

|-----------|----------|---------|------|

|-----------|----------|---------|------|

| Bits | Value         | Name             | Meaning                                                                          |  |

|------|---------------|------------------|----------------------------------------------------------------------------------|--|

| 0:3  | 1 kRun_uCode  |                  | Instructs the master processor to execute the loaded microcode.                  |  |

|      | 2             | kLoadSlave_uCode | Instructs the master processor to transfer the microcode to the slave processor. |  |

|      | 0,3-7         | Reserved         | Reserved                                                                         |  |

| 4:31 | 0 - 0xFFFFFFF | Reserved         | Reserved                                                                         |  |

3. The host sets the Loader State shared memory location at address 0x4002C to "kInit" (Table 1-7.)

Table 1-7 Loader State Words

| Bits | Value Name    |                  | Meaning                                  |  |

|------|---------------|------------------|------------------------------------------|--|

| 0:3  | 3             | klnit            | Initialization in progress.              |  |

|      | 4             | kSlave_Load_Done | The slave processor microcode is loaded. |  |

|      | 5             | kMaster_Ready    | The master processor is ready.           |  |

|      | 0-2, 6-7      | Reserved         | Reserved                                 |  |

| 4:31 | 0 - 0xFFFFFFF | Reserved         | Reserved                                 |  |

- 4. The host sets the processor to the run state and executes the microcode. The master processor transfers the code to the slave processor and sets the Loader State word to "kSlave\_Load\_Done." The host polls the Loader State word until it detects this value, then it loads the microcode for the master chip.

- 5. After the microcode for the master chip is loaded into the processor, the host initializes the Loader Command shared memory location to "kRun\_uCode" and the Loader State shared memory location to "kInit", sets the master chip to the run state, and executes the microcode. The host then waits for the transition of the Loader State location to "kMaster\_Ready" to indicate successful microcode loading.

#### Note:

When polling the Loader State shared memory location, limit the polling frequency to the rate specified by the Processor Hardware Specification. Also, include a host time-out counter to avoid dead locks.

6. Once the microcode loading and start-up processes are complete, normal command and message communication between the host and the processor occurs. The next section describes this process.

#### Note:

In a single chip implementation, the host must set the loader state location to "kMaster\_Ready" before executing the microcode.

Once the microcode loading and start-up is complete (see previous section), normal command and message communication between the host and the processor begins. This section describes the protocol used by the host to control and monitor a processor-based product.

# 1.3 Communication Process

The processor command and messaging interface is tightly contained and well-defined across all processor-based products, leading to maintainability, portability, and ease of design for the host system designer. The basic protocol guidelines follow:

- During initialization, the host allocates two *command* buffers and two *message* buffers on the host side of the PCI bus for all communication with the processor. One pair of buffers is used for *writing commands to the processor* and one pair is used for *reading messages from the processor*. Each buffer pair has an *even* and an *odd* component.

- The hosts writes all *commands*<sup>4</sup> to control processor operation into one of the command buffers. Command transfers take place in a ping-ponged manner; that is, the host writes to one command buffer (e.g., odd), while the processor reads from the other command buffer (e.g., even). After each command cycle, they switch buffers to avoid race conditions.

- All processor-based products write *messages*<sup>5</sup> to the host in response to certain internal events such as error conditions or bitstream consumption. The processor writes these messages into the message buffers. Messaging is also done in a ping-ponged manner. For example, while the processor is writing to the even message buffer, the host is reading from the odd message buffer.

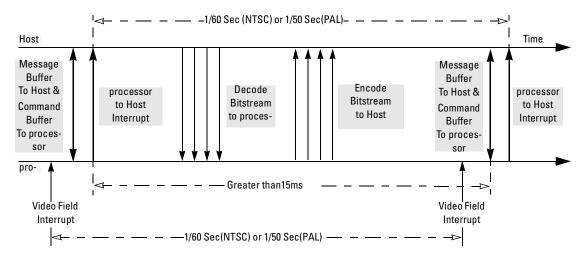

- Unless the microcode is configured otherwise, the exchange of command and message information between the host and the processor takes place once in each field time. This is synchronized either by an interrupt from the processor to the host (Section 1.4.1) or by the host polling the processor for completion of each cycle of command and message processing (Section 1.4.2).

<sup>4.</sup> See Section 1.3.2 for overall *command* structure.

<sup>5.</sup> See Section 1.3.3 for overall *message* structure.

■ One example where communication does not occur once per field is in non-real-time processing. In this case, the host and processor typically communicate once for each field's worth of data that is processed. In any case, the processor never sends an interrupt to the host more often than once per field time.

To summarize the process, for each communication cycle (typically every field), the processor:

- Copies the contents of the current host command buffer into its internal command queue(s), then switches its internal command input pointer to the other host command buffer for use in the next cycle.

- Transfers the contents of its internal message queue(s) to the current host message buffer, then switches its internal message output pointer to the other host message buffer for use in the next cycle.

- Issues an interrupt to the host.

When the host receives the interrupt from the processor (or, if in polled mode, when it detects that the processor has completed the message buffer transfer), the host:

- Clears the processor interrupt pin by writing a value of 0x20 to the host control register at CBUS address 0xFC0000, unless it is in polled mode.

- Reads and parses any processor's messages from the message buffer. To avoid a race condition, the host alternates reading between odd and even message buffers with each cycle. Since the processor is also using a ping-ponged scheme, switching message buffers with each communication cycle, the host simply switches back and forth with each cycle maintaining synchronization.

- Writes commands to the processor into the command buffer that was just read by the processor. As with the message buffers, a race condition is avoided because the processor is, for example, reading the odd command buffer while the host is writing to the even command buffer.

The rest of this manual provides additional details about the host communication protocol. A diagram at the end of this section discusses timing elements of the host communication protocol.

#### 1.3.1 Sequence Numbers

A sequence number provides synchronization between the host and the processor. This is a 16-bit number maintained by both the host and the processor and it is included within the message and command data. The number is incremented for each communication cycle and it rolls over from 0xFFFF to 0x0000.

During each communication cycle, the processor writes a sequence number to the current message block. The host checks this number against its internal sequence number to verify synchronization.

On the other side, the host writes a sequence number to the current command block. The processor checks it against its internal sequence number to verify synchronization.

To ensure cycle synchronization, the following conditions must be met:

- The processor must detect a sequence number in the current command buffer equal to the sequence number it is writing to the current message buffer.

- For the host, the sequence number it reads from the current message buffer should lag two digits behind the sequence number it is writing to the current command buffer.

If the above conditions are not met, then a synchronization error has occurred and error recovery is needed. Section 1.3.5 describes the error recovery process.

Because of the ping-ponged nature of the command and message buffers, the first command buffer and the first message buffer have odd sequence numbers, while the second command buffer and the second message buffer have even sequence numbers (numbers start at 1). For this reason, the two command buffers are called "odd and even command buffers," while the two message buffers are called "odd and even message buffers."

#### 1.3.2 Command Block Format

The size of the odd and even command blocks depends on the requirements and constraints for each product and may be different among processor-based products. However, no product requires a command block size greater than 4K bytes. See the product-specific documentation for the exact size requirement for each product.

Regardless of the size of the command blocks, they must conform to the same basic format across all products. Table 1-8 shows this format.

Table 1-8 **Command Block Format**

| Data Field            | Length                                                  | Description                                                                                                                                |

|-----------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Priority Commands     | M * 32 bits                                             | Priority commands of the format described in "Command Syntax" on page 32.                                                                  |

| Scheduled<br>Commands | N * 32 bits                                             | Scheduled commands of the format described in "Command Syntax" on page 32.                                                                 |

| Padding               | (Total size of command block) - ((M + N + 2) * 32 bits) | The command block is fixed length, so this field varies in size to keep the length and sequence number at the last locations in the block. |

| Reserved              | 16 bits                                                 | Must be set to 0.                                                                                                                          |

| Length M              | 16 bits                                                 | The size of the priority command portion of the command block, in 32-bit words.                                                            |

| Length N              | 16 bits                                                 | The size of the scheduled command portion of the command block, in 32-bit words.                                                           |

| Sequence Number       | 16 bits                                                 | Communication synchronization sequence number as described above in Section 1.3.1.                                                         |

The highlights of the Command Block format are as follows:

- Priority commands appear first in the host command block, followed by scheduled commands (Commands are further explained in Chapter 2).

- Since there may be a varying number of commands (each of a variable size), length fields (M and N) are provided so that the processor can discriminate between the end of the priority command and the scheduled command portions of the command block.

- Since the length fields and the sequence number are at fixed places at the end of the command block, there will be a variable amount of unused space in the middle of the command block between the commands and the length fields.

- The host writes the current command block during each command cycle, even if it has no commands to send, then writes the sequence number as the last field. If there are no commands, M and N are set to zero, but the sequence number is updated to maintain communication synchronization with the processor. Also, in order to keep from repeatedly reading the same command block during error recovery, the processor sets the most significant bit of the N field after it has finished reading the block. This means that the host must clear this bit during each communication cycle.

- Since the API is generalized for all processor products, some fields of the command block may not apply to all products. For example, some products may only support priority commands, rendering useless the scheduled command region of the command block. Unused fields are set to zero by the host to ensure compatibility with future microcode revisions.

### 1.3.3 Message Block Format

Like the command blocks, the odd and even message blocks may have different size requirements for different products. However, they are never larger than 1K bytes. Table 1-9 shows the general message block format that is common to all processor-based products. The highlights of the Message Block format are as follows:

- The actual messages occupy the first part of the message block. Since there may be a variable number of messages of varying lengths in the block, a length field (N) is provided so that the host software can determine where the message portion of the message block ends.

- The length field and the sequence number occupy the last word of the message block. Thus, in between the actual messages and the length field there is an unused area of variable size depending on the amount of message data present.

- The processor always writes the current message block, even if there are no messages. If there are no messages, N is set to zero,

but the sequence number is still updated to maintain synchronization. The sequence number is always the last data written to the message block. As such, it can act as a semaphore to the host if the host wishes to perform communication in polled mode instead of receiving interrupts from the processor (Section 1.4.2).

Table 1-9 Message Block Format

| Data Field Length |                                                           | Description                                                                                                                            |  |  |

|-------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Messages          | N * 32 bits                                               | Messages of the format described in<br>"Messages" on page 39                                                                           |  |  |

| Padding           | (Total size of<br>message block) -<br>((N + 2) * 32 bits) | Message block is fixed length, so this field varies in size to keep the length and sequence number at the last locations in the block. |  |  |

| Reserved          | 32 bits                                                   | Undefined, should be ignored                                                                                                           |  |  |

| Length N          | 16 bits                                                   | Total length of the actual messages in the block, in 32-bit words.                                                                     |  |  |

| Sequence Number   | 16 bits                                                   | Communication synchronization sequence number as described above in Section 1.3.1.                                                     |  |  |

#### 1.3.4 Communication Initialization and Bootstrap

Before starting the processor, the host allocates its memory for even and odd command buffers and even and odd message buffers of the sizes required by the specific product. Because of limitations of the PCI bus, the addresses of the command and message buffers must be eight-byte aligned.

The host must communicate to the processor the command and message buffers addresses via shared memory at the time required for initializing shared memory, i.e. just before the microcode is loaded. Table 1-4 shows the locations set aside for this purpose and the rest of the shared memory locations.

#### Note:

The processor expects the shared memory addresses to contain legal values before microcode execution begins. If the host does not provide legal values as part of the microcode download process, host memory could be corrupted by the processor.

To bootstrap the communication process, the host prepares the first two command buffers before starting microcode execution. The host writes the odd command buffer with a sequence number of one, and the even command buffer with a sequence number of two. These command blocks may or may not have actual commands in them; if they do not, their M and N fields are set to zero (Section 1.3.2).

When the processor executes, it checks that the odd command buffer is ready with a sequence number of one. (This is the case if the host follows the proper communication bootstrap procedure.) It then reads this first command block and writes the first message block to the odd message buffer with a sequence number of one. First, the processor sends the Initialization Message ("Initialization Message" on page 41). This message serves as a handshake back to the host, signalling that the processor has started the communication process. It also informs the host of parameters such as its internal checksum result and the software revision number.

#### Note:

We do not specify whether or not the processor sends the first message within the same field-time as when it detects the host's first command. The processor can delay this action one or more fields. This should be transparent to the host and the host can wait until the processor signals that the first message is written.

Once the processor completes the first command transfer and message blocks, it sends its first host's interrupt. After receiving the interrupt (or, if in polled mode, after detecting the first message block's sequence number), the host reads the first message block and sends the third command block in the odd command buffer using a sequence number of three.

From this point, communication proceeds as normal. For example, just prior to the second host's interrupt, the processor reads the even command block with a sequence number of two (prepared by the host prior to microcode execution) and writes the even message block with a sequence number of two. On reception of the second interrupt, the host reads the second message block and writes the even command block with a sequence number of four.

The odd-even-odd-even pattern continues. Due to the nature of the bootstrap process, in which the host prepares the first two command blocks before executing the microcode, the message block sequence number always lags two digits behind the sequence number of the next host's command block.

Table 1-10 graphically exemplifies the entire host communication process, which includes the bootstrap routines.

#### 1.3.5 Error Recovery

Due to performance constraints or system hardware glitches, errors may occur in the host communication process. These errors are detected either by the host or the processor as follows:

- The processor records an error if the sequence number it reads from the current command block does not match the sequence number it writes to the current message block.

- The host registers an error if the sequence number it reads from the current message buffer does not lag two digits behind the sequence number it is writing to the current command buffer.

The above cases indicate that either the host or the processor missed a communication cycle.

If the processor detects an error, it writes a sequence number of 0x7FFF to the even message block<sup>6</sup>. It then waits until the host writes a sequence number of one in the odd command block and clears the most significant bit of the "N" field (Section 1.3.2). In the meantime, it reduces the host interrupt rate by a factor of four to prevent amplifying any interrupt-servicing problem that caused the error in the first place.

<sup>6.</sup> This is an odd number in the even blockand it never occurs normally.

When the host sees a sequence number of 0x7FFF in the even message block, indicating that the processor detected a communication error, it restarts the communication process. That is, it writes a sequence number of two to the even command buffer (sets the M and N fields to zero), and writes a sequence number of one to the odd command buffer. Since the processor is waiting for the sequence number in the odd buffer to become one before it restarts the communication process, the host writes the even command block before the odd command block to prevent the processor from restarting the communication process before the even command block is ready.

Once the processor detects a sequence number of one in the odd command block, it assumes that the host is ready to resume normal communications. Consequently, it restarts the communication process on its side and resumes the normal rate of interrupts. Now, communications proceeds normally.

#### Note:

As with the communication bootstrap process, in error recovery, the processor does not necessarily respond immediately to the host writing the first command block. However, this should be transparent to the host since it waits until the processor writes the first message.

If the host detects a sequence number mismatch, it forces an error by writing the next command block's sequence number with an out-ofrange value. The processor detects this error and starts the protocol resynchronization process.

While in error recovery mode, the processor continues the encoding or decoding process using current parameters and available bitstreams or buffers. Thus, if the host decides not to keep up with the interrupts from the processor, it can operate indefinitely in error recovery mode while the processor continues its operations.

<sup>7.</sup> Refer to "Data Stream Input and Output" on page 45 for the default behavior of the data stream I/O process.

### 1.3.6 Sample Communication Sequence

Table 1-10 shows a typical processor-host communication sequence including the bootstrap process and an error detection and correction scenario. In the table, the first row represents the initialization period while other rows represent half of a VSYNC cycle (i.e. VSYNC high or VSYNC low),

Processor actions preceding the host interrupt occupy the upper part of each cell; host actions occurring after the host interrupt occupy the lower part. The cells displaying an action by the processor or the host indicate the command or message buffer accessed and the sequence number read from or written to that buffer.

**Table 1-10** Sample Communication Sequence

| VSYNC | Interrupt               | Command<br>Read By<br>processor                   | Message<br>Written By<br>processor          | Message<br>Read By<br>Host | Command<br>Written By<br>Host | Comment                                                                                                                                  |

|-------|-------------------------|---------------------------------------------------|---------------------------------------------|----------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Init  | Ucode<br>not<br>started | Ucode not yet started                             | Ucode not<br>yet started                    | Ucode not<br>yet started   | Odd: 1 and<br>Even: 2         | Initialization by host before starting the microcode (Ucode).                                                                            |

| 0     | 1                       | Odd: 1                                            | Odd:1                                       | Odd:1                      | Odd: 3                        | Processor detects that host is ready and sends the first host interrupt after writing the first message buffer.                          |

| 1     | 2                       | Even: 2                                           | Even: 2                                     | Even: 2                    | Even: 4                       | Normal communication cycle.                                                                                                              |

| 2     | 3                       | Odd: 3                                            | Odd: 3                                      | Odd: 3                     | Transfer error                | Host attempts to write 5, but the data doesn't get there for some reason.                                                                |

| 3     | 4                       | Even: 4                                           | Even: 4                                     | Even: 4                    | Even: 6                       | Error not yet detected, so this cycle is normal.                                                                                         |

| 4     | 5                       | Odd: 3<br>(Error: same<br>as last odd<br>command) | Even: 0x7FFF<br>(would have<br>been Odd: 5) | Even: 0x7FFF               | Even: 2, then<br>Odd: 1       | Command 5 never made it. The processor detects this and sets the even message to 0x7FFF. The host then detects this and starts recovery. |

| 5     | 6                       | Odd: 1                                            | Odd:1                                       | Odd:1                      | Odd: 3                        | Back to odd buffers and odd VSYNC, so restart communication.                                                                             |

| 6     | 7                       | Even: 2                                           | Even: 2                                     | Even: 2                    | Even: 4                       | Back to normal.                                                                                                                          |

| 7     | 8                       | Odd: 3                                            | Odd: 3                                      | Odd:3                      | Odd: 4                        | ad infinitum.                                                                                                                            |

The above table does not reflect the additional delay that, in the bootstrap and error recovery processes, may or may not occur between the time that the processor detects that the host wrote the first command buffer and the time that it writes the first message buffer and sends a host interrupt. Any such delay should be transparent to the host and the host should not depend on any specific response time.

## 1.4 **Application Models**

This section briefly describes two possible models for host applications that need to communicate with processor-based products. The first is an interrupt-driven model, while the second is a polled-mode model.

## 1.4.1 Interrupt-Driven Model

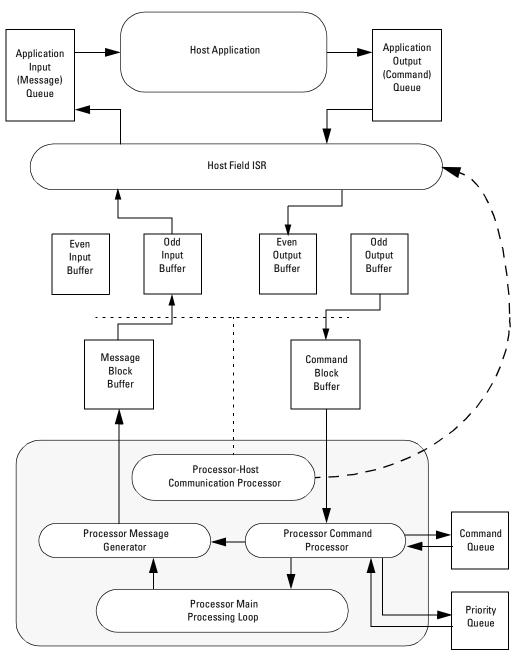

In an application using interrupt-driven communication, the host attaches an interrupt service routine (ISR) to the interrupt generated from the processor. The interrupt indicates completion of the command and message data transfer. The ISR handles the processing of the messages from the host and the commands to the processor as follows:

- The ISR stores messages in an internal message queue for further processing.

- The ISR transfers pending commands from an internal command queue instead of immediately parsing messages and deciding which commands should be sent next. This minimizes the time spent inside the ISR, which is usually a design concern for most systems.

When the above method is used, the main processing loop of the host application parses the messages from its internal messages queue and puts whatever commands it decided were appropriate into its internal command queue for transfer to the processor at the next host interrupt. Figure 1-2 illustrates this type of application.

In addition to reading messages and writing commands, the host's ISR verifies the sequence number of the current message block against the sequence number it writes to the next command block. The sequence number of the message block that the host reads with each communication cycle always lags two digits behind the sequence number of the command block that the host writes (Section 1.3.4). If this is not the case, the ISR needs to enter error recovery mode (Section 1.3.5).

The host ISR also needs to clear the host interrupt. Otherwise, since the host interrupt is a level-triggered interrupt, the host will continue to be interrupted. The interrupt can be cleared by writing a value of 0x20 to the host control register at address 0xFC0000.

In a normal situation (i.e., real-time decoding or encoding), the processor ensures that the host interrupts are one field time apart. However, the phase difference between a VSYNC transition and the host interrupt may be different in each microcode product. Refer to "System Timing" on page 75 and the product-specific documentation for more exact timing information.

In a non-realtime scenario such as copying images from the host to the encoder via the PCI bus or sending images through the PCI bus back to the host, a host interrupt is issued whenever the processor completes an image (field or frame) of data. In any case, the processor ensures that there is never more than one interrupt per field time.

Figure 1-2 **Typical Interrupt-Driven Host Application**

#### 1.4.2 Polled-Mode Model

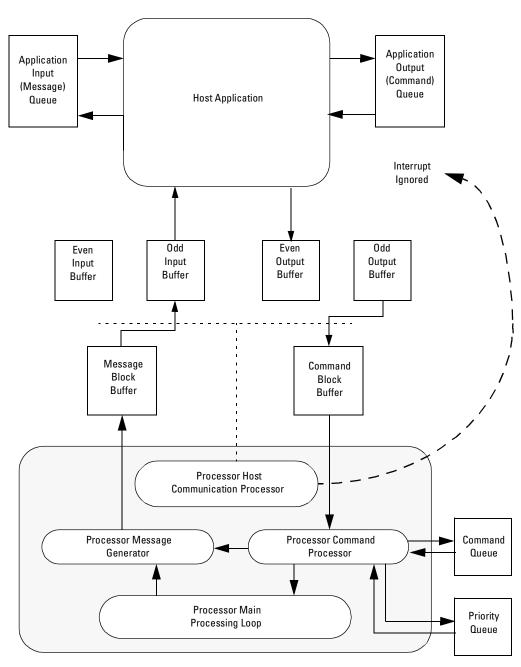

The host can also communicate with the processor in polled mode. Since the processor writes the current message block after it reads the current command block, and the sequence number is the last word written to the message block, the message block sequence number serves as a semaphore for the host to detect when the processor has completed transfer of all the command and message data. The host can simply ignore the interrupt from the processor and wait for the sequence number in the current message block to change. At this point, it can proceed with message and command processing as it would with an interrupt-driven application. Figure 1-3 illustrates a typical polled-mode host application.

Note that to the processor, it is irrelevant whether the host runs in polled mode or interrupt driven mode.

Figure 1-3 **Typical Polled-Mode Host Application**

**Application Models**

## 2 Commands