Methodological Handbook Efficient Development of Safe Avionics Software with DO-178B Objectives Using SCADE Suite

#### CONTACTS

#### Legal Contact

Esterel Technologies SA Parc Euclide - 8, rue Blaise Pascal 78990 Elancourt FRANCE Phone: +33 1 30 68 61 60 Fax: +33 1 30 68 61 61

#### **US Technical Support**

Esterel Technologies Inc. 100 View Street, Suite 208 Mountain View, CA 94041 UNITED STATES **Phone:** +1 650 641 3250

Submit questions to Technical Support at <a href="mailto:support@esterel-technologies.com">support@esterel-technologies.com</a>. Contact one of our Sales representatives at <a href="mailto:sales@esterel-technologies.com">sales@esterel-technologies.com</a>. Direct general questions about Esterel Technologies to <a href="mailto:info@esterel-technologies.com">info@esterel-technologies.com</a>. Discover latest news on our products and technology at <a href="mailto:www.esterel-technologies.com">www.esterel-technologies.com</a>.

#### LOCAL SUPPORT SITES

#### **Northern Europe**

Esterel Technologies PO Box 7995 Crowthorne RG45 9AA UNITED KINGDOM **Phone:** +44 1344 780898

#### **Central Europe**

Esterel Technologies GmbH Otto-Hahn - Str. 13b D- 85521 Ottobrunn - Riemerling GERMANY **Phone:** +49 89 608 75537

#### Southern Europe

Esterel Technologies SA Park Avenue - 9, rue Michel Labrousse 31100 Toulouse FRANCE **Phone:** +33 5 34 60 90 50

#### China

Esterel Technologies No. 10-401, Shanghai Pudong Software Park 498, GuoShouJing Road 201203, Shanghai P.R. CHINA **Phone**: +86-21 5027 1120

© 2006 Esterel Technologies SA. All rights reserved Esterel Technologies SA. SCADE Suite is a trademark of Esterel Technologies.

Shipping date: February 2006 Revision: SC-HB-DO178B - SC/2012u6-KCG4.2

### Abstract

This document addresses the issue of cost and productivity in the development of safe embedded software for avionics applications. Such projects, driven by the DO-178B guidelines, traditionally require very difficult and precise development and verification efforts. This handbook reviews the regulatory guidelines and then presents the optimization of the development and verification processes that can be achieved with the SCADE Suite methodology and tools. SCADE Suite supports the automated production of a large part of the development life-cycle elements. The effect of using SCADE Suite together with the qualified KCG 4.2 Code Generator will be presented in terms of savings in the development and verification activities, following a step-by-step approach and considering the objectives that have to be met at each step.

## **Table of Contents**

| 1. D | ocument Background, Objectives, and Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                            |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 1.1  | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                            |

| 1.2  | Objectives and Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                            |

| 2. D | evelopment of Safety-Related Airborne Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                            |

| 2.1  | ARP 4754 and DO-178B Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3                                            |

| 2.2  | <ul> <li>2.1.1 Introduction</li> <li>2.1.2 ARP 4754</li> <li>2.1.3 DO-178B</li> <li>2.1.4 Relationship between ARP 4754 and DO-178B</li> <li>2.1.5 Development assurance levels</li> <li>2.1.6 Objective-oriented approach</li> <li>2.1.7 DO-178B processes overview</li> <li>DO-178B Development Processes</li> </ul>                                                                                                                                                                                                                                                                                                                              | 3<br>3<br>4<br>5<br>5<br>6<br>7              |

| 2.3  | <ul> <li>DO-178B Verification Processes</li> <li>2.3.1 Objectives of software verification</li> <li>2.3.2 Reviews and analyses of the high-level requirements</li> <li>2.3.3 Reviews and analyses of the low-level requirements</li> <li>2.3.4 Reviews and analyses of the source code</li> <li>2.3.5 Software testing process</li> </ul>                                                                                                                                                                                                                                                                                                           | 8<br>8<br>9<br>9<br>10                       |

| 2.4  | <ul> <li>What Are the Main Challenges in the Development of Airborne Software?</li> <li>2.4.1 Avoiding multiple descriptions of the software</li> <li>2.4.2 Preventing ambiguity and lack of accuracy in specifications</li> <li>2.4.3 Avoiding low-level requirements and coding errors</li> <li>2.4.4 Allowing for an efficient implementation of code on target</li> <li>2.4.5 Finding specification and design errors as early as possible</li> <li>2.4.6 Lowering the complexity and cost of updates</li> <li>2.4.7 Improving verification efficiency</li> <li>2.4.8 Providing an efficient way to store Intellectual Property (IP)</li> </ul> | 12<br>12<br>13<br>13<br>13<br>14<br>14<br>14 |

| 3. M | odel-Based Development with SCADE Suite and KCG                                                                                                                                                                                                                                                                                                                                                                                                                     | 15                                                       |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 3.1  | What Is SCADE?                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                       |

| 3.2  | SCADE Modeling Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16                                                       |

|      | <ul> <li>3.2.1 Familiarity and accuracy reconciled</li> <li>3.2.2 SCADE node</li> <li>3.2.3 Block diagrams for continuous control</li> <li>3.2.4 Safe State Machines for discrete control</li> <li>3.2.5 Mixed continuous/discrete control</li> <li>3.2.6 Cycle-based intuitive computation model</li> <li>3.2.7 SCADE data typing</li> <li>3.2.8 SCADE Suite as a model-based development environment</li> <li>3.2.9 SCADE modeling and safety benefits</li> </ul> | 16<br>17<br>18<br>21<br>22<br>22<br>23<br>23<br>23<br>24 |

| 4. S | oftware Development Activities with SCADE Suite                                                                                                                                                                                                                                                                                                                                                                                                                     | 27                                                       |

| 4.1  | Overview of Software Development Activities                                                                                                                                                                                                                                                                                                                                                                                                                         | 27                                                       |

| 4.2  | Software Requirements Process with SCADE                                                                                                                                                                                                                                                                                                                                                                                                                            | 28                                                       |

| 4.3  | Software Design Process with SCADE                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29                                                       |

| 4.4  | <ul><li>4.3.1 Architecture design</li><li>4.3.2 SCADE low-level requirements development</li><li>Software Coding Process</li></ul>                                                                                                                                                                                                                                                                                                                                  | 30<br>31<br>34                                           |

| 4.5  | <ul><li>4.4.1 Code generation from SCADE data flow diagrams</li><li>4.4.2 Code generation from SCADE SSMs</li><li>Software Integration Process</li></ul>                                                                                                                                                                                                                                                                                                            | 35<br>37<br>39                                           |

|      | <ul> <li>4.5.1 Integration aspects</li> <li>4.5.2 Input/output</li> <li>4.5.3 Integration of external data and code</li> <li>4.5.4 SCADE scheduling and tasking</li> </ul>                                                                                                                                                                                                                                                                                          | 39<br>39<br>39<br>40                                     |

| 4.6  | Teamwork                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 43                                                       |

| 5. S | oftware Verification Activities                                                                                                                                                                                                                                                                                                                                                     | 45                                           |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 5.1  | Overview                                                                                                                                                                                                                                                                                                                                                                            | 45                                           |

| 5.2  | Verification of the SCADE High-Level Requirements                                                                                                                                                                                                                                                                                                                                   | 45                                           |

|      | <ul><li>5.2.1 Verification objectives for the HLR</li><li>5.2.2 Verification methods for HLR</li><li>5.2.3 Verification summary for HLR</li></ul>                                                                                                                                                                                                                                   | 45<br>46<br>47                               |

| 5.3  | Verification of the SCADE Low-Level Requirements and Architecture                                                                                                                                                                                                                                                                                                                   | 47                                           |

|      | <ul> <li>5.3.1 Verification objectives</li> <li>5.3.2 SCADE model accuracy and consistency</li> <li>5.3.3 Compliance with design standard</li> <li>5.3.4 Traceability from SCADE LLR to HLR</li> <li>5.3.5 Verifiability</li> <li>5.3.6 Compliance with high-level requirements</li> <li>5.3.7 Partitioning</li> <li>5.3.8 Verification summary for LLR and architecture</li> </ul> | 47<br>48<br>48<br>48<br>49<br>49<br>53<br>53 |

| 5.4  | Verification of Coding Outputs and Integration Process                                                                                                                                                                                                                                                                                                                              | 54                                           |

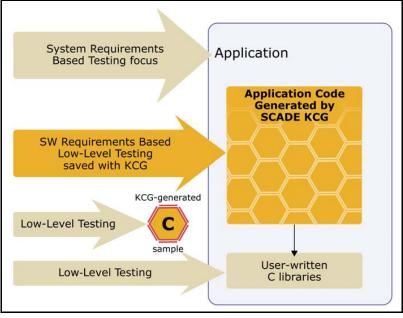

| 5.5  | <ul><li>5.4.1 Verification objectives</li><li>5.4.2 Impact of code generator qualification</li><li>5.4.3 Verification summary</li><li>The Combined Testing Process</li></ul>                                                                                                                                                                                                        | 54<br>54<br>55<br>55                         |

|      | <ul><li>5.5.1 Verification objectives</li><li>5.5.2 Divide-and-conquer approach</li><li>5.5.3 Combined testing process organization</li><li>5.5.4 Verification summary</li></ul>                                                                                                                                                                                                    | 55<br>56<br>56<br>58                         |

| 6. V | erification of the Verification Activities                                                                                                                                                                                                                                                                                                                                          | 59                                           |

| 6.1  | Verification Objectives                                                                                                                                                                                                                                                                                                                                                             | 59                                           |

| 6.2  | Verification of Test Procedures and Test Results                                                                                                                                                                                                                                                                                                                                    | 59                                           |

| 6.3  | HLR Coverage Analysis                                                                                                                                                                                                                                                                                                                                                               | 59                                           |

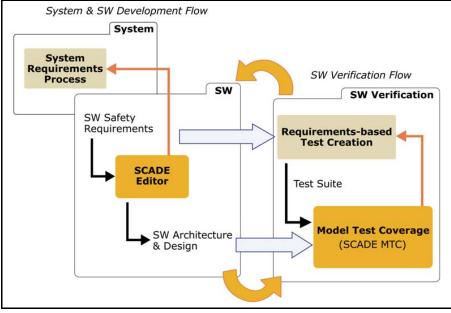

| 6.4  | LLR Coverage Analysis with MTC                                                                                                                                                                                                                                                                                                                                                      | 60                                           |

|      | 6.4.1 Objectives and coverage criteria                                                                                                                                                                                                                                                                                                                                              | 60                                           |

|       | 6.4.2 LLR coverage analysis with SCADE Suite MTC | 62       |

|-------|--------------------------------------------------|----------|

| 6.5   | Structural Coverage of the Source Code           | 66       |

|       | 6.5.1 Control structure coverage                 | 66       |

| 6.6   | 6.5.2 Data coupling and control coupling         | 67<br>68 |

| 0.0   | Summary of Verification of Verification          | 68       |

| Арр   | endixes and Index                                | 69       |

| A R   | eferences                                        | 71       |

| B A   | cronyms and Glossary                             | 73       |

| C D   | 0-178B Qualification of SCADE KCG 4.2            | 77       |

| C-1   | What Does Qualification Mean and Imply?          | 77       |

| C-2   | Development of SCADE KCG 4.2                     | 77       |

| C-3   | SCADE KCG 4.2 Life-Cycle Documentation           | 78       |

| D TI  | ne Compiler Verification Kit (CVK)               | 79       |

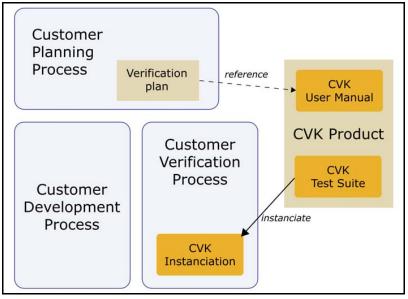

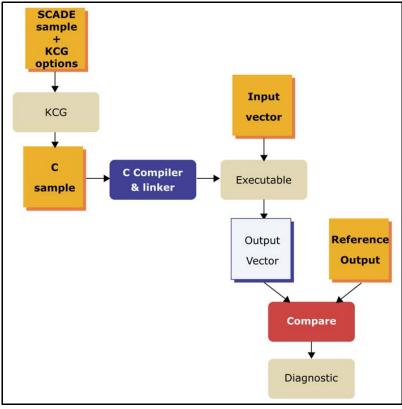

| D-1   | CVK Product Overview                             | 79       |

| D-2   | Motivation for Sample-Based Testing              | 81       |

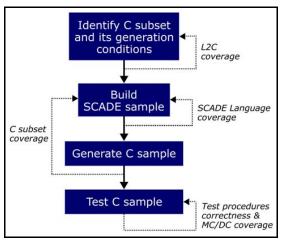

| D-3   | Strategy for Developing CVK                      | 82       |

| D-4   | Use of CVK                                       | 83       |

| INDEX | (                                                | 87       |

## List of Figures

| Figure 2.1:  | Relationship between ARP 4754 and DO-178B processes             | 4  |

|--------------|-----------------------------------------------------------------|----|

| Figure 2.2:  | DO-178B life-cycle processes structure                          | 6  |

| Figure 2.3:  | DO-178B development processes                                   | 7  |

| Figure 2.4:  | DO-178B testing processes                                       | 10 |

| Figure 3.1:  | SCADE addresses the applicative part of software                | 15 |

| Figure 3.2:  | Control engineering view of a Controller                        | 16 |

| Figure 3.3:  | Software engineering view of a Controller                       | 16 |

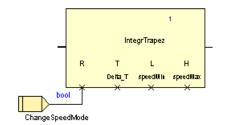

| Figure 3.4:  | Graphical notation for an integrator node                       | 17 |

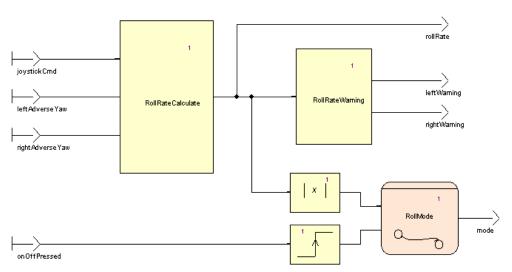

| Figure 3.5:  | A SCADE block diagram for roll management                       | 18 |

| Figure 3.6:  | Detection of a causality problem                                | 19 |

| Figure 3.7:  | Functional expression of concurrency in SCADE                   | 20 |

| Figure 3.8:  | Initialization of flows                                         | 20 |

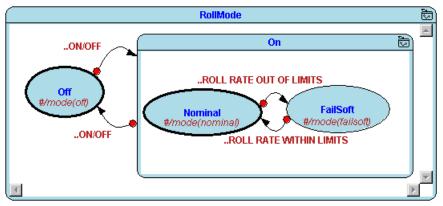

| Figure 3.9:  | Safe State Machine for RollMode                                 | 21 |

| Figure 3.10: | The cycle-based execution model of SCADE Suite                  | 22 |

| Figure 3.11: | Model-based development with SCADE Suite and KCG 4.2            | 24 |

| Figure 4.1:  | Software development processes with SCADE Suite                 | 27 |

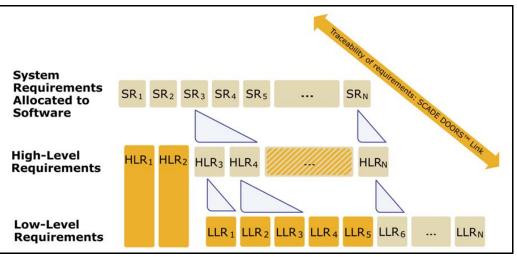

| Figure 4.2:  | Development of high-level and low-level requirements with SCADE | 28 |

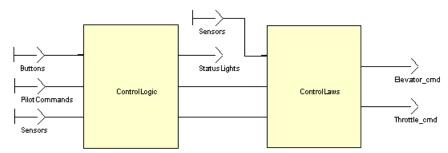

| Figure 4.3:  | Top-level view of a simple flight control system                | 29 |

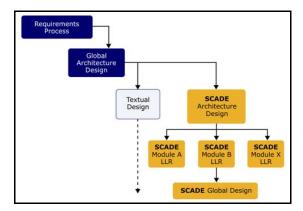

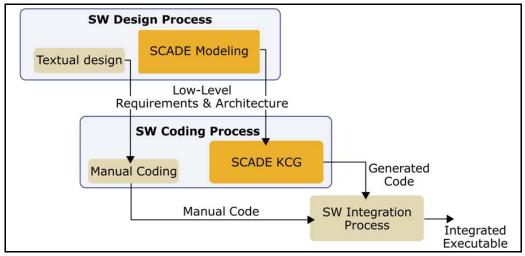

| Figure 4.4:  | The software design process with SCADE                          | 29 |

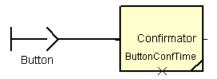

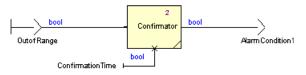

| Figure 4.5:  | Inserting a Confirmator in a Boolean input flow                 | 31 |

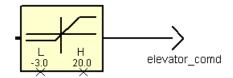

| Figure 4.6:  | Inserting a Limiter in an output flow                           | 31 |

| Figure 4.7:  | A first order filter                                            | 32 |

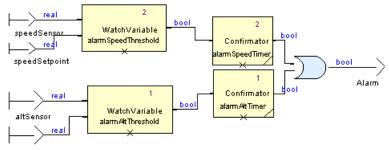

| Figure 4.8:  | Alarm detection logic                                           | 33 |

| Figure 4.9:  | Safe State Machine for RollMode management                      | 33 |

| Figure 4.10: | The software coding process with SCADE                          | 35 |

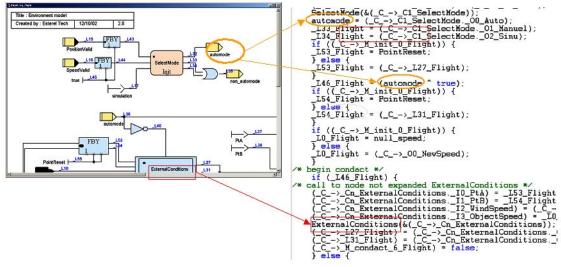

| Figure 4.11: | SCADE data flow to generated C source code traceability         | 36 |

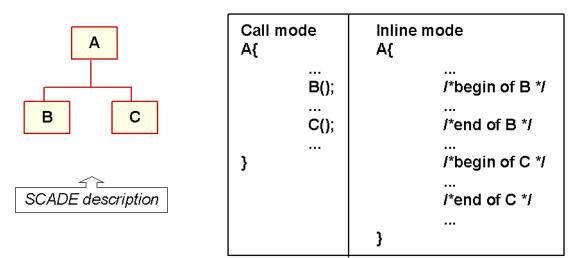

| Figure 4.12: | Comparing Call and Inline modes                                 | 37 |

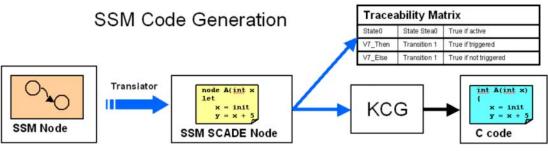

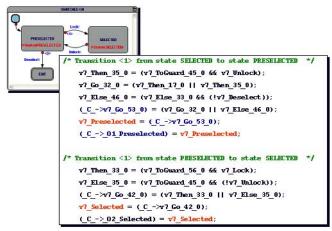

| Figure 4.13: | C code generation from SSMs                                     | 38 |

| Figure 4.14: | SCADE SSM to generated C source code traceability               | 38 |

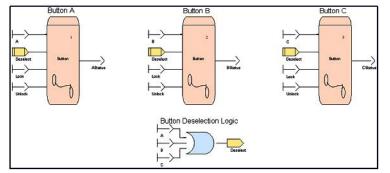

| Figure 4.15: | Three buttons in a parallel data flow                           | 39 |

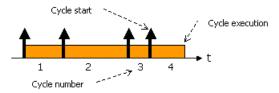

| Figure 4.16: | SCADE execution semantics                                       | 40 |

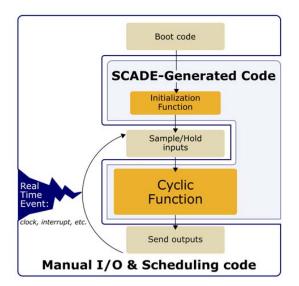

| Figure 4.17: | SCADE code integration                                          | 41 |

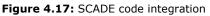

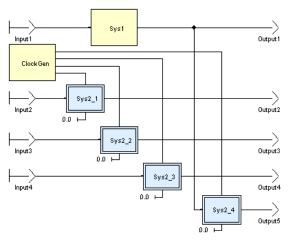

| Figure 4.18: | Modeling a birate system                                                           | 41 |

|--------------|------------------------------------------------------------------------------------|----|

| Figure 4.19: | Timing diagram of a bi-rate system                                                 | 42 |

| Figure 4.20: | Modeling distribution of the slow system over four cycles                          | 42 |

| Figure 4.21: | Timing diagram of the distributed computations                                     | 42 |

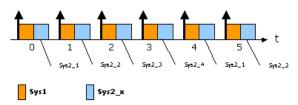

| Figure 4.22: | Typical teamwork organization                                                      | 44 |

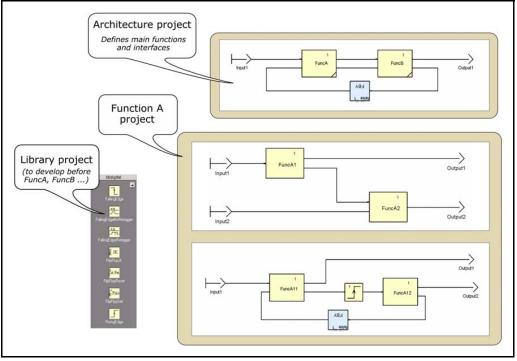

| Figure 5.1:  | Traceability between SCADE LLR and HLR using DOORSTM Link                          | 49 |

| Figure 5.2:  | Simulation makes it possible to "play with the software specification"             | 50 |

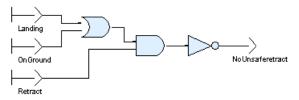

| Figure 5.3:  | Observer node containing landing gear safety property                              | 51 |

| Figure 5.4:  | Connecting the observer node to the landing gear controller                        | 51 |

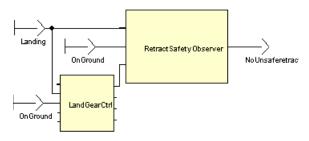

| Figure 5.5:  | Design Verifier workflow                                                           | 52 |

| Figure 5.6:  | The combined testing process with KCG                                              | 57 |

| Figure 6.1:  | Position of SCADE Suite Model Test Coverage (MTC)                                  | 63 |

| Figure 6.2:  | Using SCADE Suite Model Test Coverage (MTC)                                        | 64 |

| Figure 6.3:  | Non activated Confirmator                                                          | 65 |

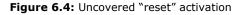

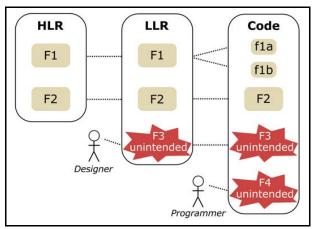

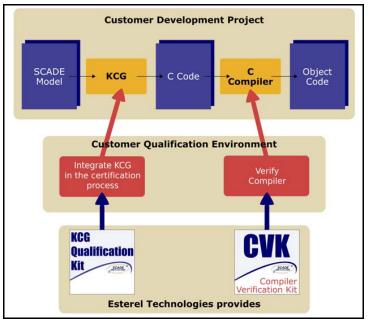

| Figure 6.4:  | Uncovered "reset" activation                                                       | 65 |

| Figure 6.5:  | Sources of unintended functions in a traditional process                           | 65 |

| Figure 6.6:  | Elimination of unintended functions with MTC and KCG                               | 66 |

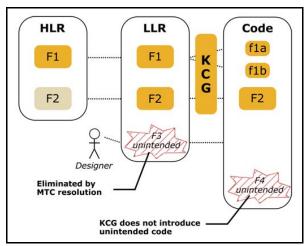

| Figure D.1:  | Role of KCG and CVK in the qualification of the customer's development environment | 80 |

| Figure D.2:  | Sequential structure of the generated code (without expansion)                     | 81 |

| Figure D.3:  | Strategy for developing and verifying CVK                                          | 83 |

| Figure D.4:  | Use of CVK items in the customer's processes                                       | 84 |

| Figure D.5:  | Position of CVK items in the compiler verification process                         | 85 |

## **List of Tables**

| Table 2.1: | Example of test cases                                                                 | 12 |

|------------|---------------------------------------------------------------------------------------|----|

| Table 3.1: | Components of SCADE functional modules: nodes                                         | 17 |

| Table 5.1: | DO-178B Table A-3                                                                     | 45 |

| Table 5.2: | DO-178B Table A-3 Objectives Achievement                                              | 47 |

| Table 5.3: | DO-178B Table A-4                                                                     | 47 |

| Table 5.4: | DO-178B Table A-4 Objectives Achievement                                              | 53 |

| Table 5.5: | DO-178B Table A-5                                                                     | 54 |

| Table 5.6: | DO-178B Table A-5 Objectives Achievement                                              | 55 |

| Table 5.7: | DO-178B Table A-6                                                                     | 55 |

| Table 5.8: | DO-178B Table A-6 Objectives Achievement                                              | 58 |

| Table 6.1: | DO-178B Table A-7                                                                     | 59 |

| Table 6.2: | DO-178B Table A-7 Objectives Achievement                                              | 68 |

| Table C.1: | Documents required for SCADE KCG 4.2 qualification audit by Certification Authorities | 78 |

| Table D.1: | Type of code generated from SCADE operators                                           | 82 |

## 1. Document Background, Objectives, and Scope

### 1.1 Background

A traditional situation in the avionics industry is that the function and architecture of an embedded computer system (*i.e.*, Flight Control, Braking, Cockpit Display, etc.) are defined by system engineers; the associated control laws are developed by control engineers using some informal notation or a semi-formal notation mostly based on schema-blocks and/or state machines; and the embedded production software is finally specified textually and coded by hand in C and Ada by software engineers.

In this context, qualified automatic code generation from formal models is a technology that may carry strong Return On Investment (ROI), while preserving the safety of the application. Basically, the idea is to describe the application through a software model, including the control laws as described above, and to automatically generate the C code from this model using a qualified code generator, in the sense of DO-178B, thus bringing the following advantages to the development life cycle:

- When a proper modeling approach is defined:

- It fulfills the needs of control engineers, typically using such notations as data flow diagrams and state machines.

- It fulfills the needs of software engineers by supporting the accurate definition of the

software requirements and efficient automatic code generation of software, having the qualities that are expected for such applications (*i.e.*, efficiency, determinism, static memory allocation, etc.).

- It allows setting up efficient new processes to ensure that safety criteria are met.

- It saves coding time, as this is automatic.

- It saves a significant amount of verification time, as the use of such tools guarantees that the generated source code agrees with the model.

- It allows identifying problems earlier in the development cycle, since most of the verification activities can be done at model level.

- It reduces the change cycle time, since modifications can be performed at model level and code can automatically be regenerated.

## **1.2 Objectives and Scope**

This document gives a careful explanation of the system and software life cycles as described in the ARP 4754 and DO-178B guidelines. It then explains how to use both the proper modeling techniques and automatic code generation from models to obtain drastic productivity improvements.

The document is organized as follows:

<u>Section 2.</u> This section provides an introduction to the regulatory guidelines of ARP 4754 and DO-178B that are used when developing embedded avionics software. It then describes the main challenges in the development of safety-critical applications, in terms of specification, verification, and efficiency of the resulting software.

Section 3. This section presents an overview of the SCADE Suite methodology and tools. It first demonstrates how SCADE maintains the highest-quality standards, while reducing costs based on a "correct-by-construction" approach and the use of a qualified automatic code generator, according to the following points:

- A unique and accurate software description, which enables the prevention of many specification or design errors, can be shared among project participants.

- The early identification of most remaining design errors makes it possible to fix them in the requirements/design phase rather than in the code testing or integration phase.

- Qualified code generation not only saves writing the code by hand, but also the cost of verifying it.

<u>Section 4.</u> This section is devoted to the software development activities using SCADE tools, including the use of the KCG 4.2 qualified code generator. It also explains how SCADE-generated code can be integrated on target, including when it has to interact with an RTOS (Real Time Operating System).

<u>Section 5.</u> and <u>Section 6.</u> These sections present the verification activities that take place when SCADE is used, including model-level verification with the Simulator, the Design Verifier, and the Model Test Coverage tool, as well as specific verification activities aimed at detecting compiler errors.

Appendix A lists the references.

<u>Appendix B</u> is a glossary of terms.

<u>Appendix C</u> details the KCG 4.2 qualification process.

<u>Appendix D</u> details the Compiler Verification Kit (CVK).

## 2. Development of Safety-Related Airborne Software

### 2.1 ARP 4754 and DO-178B Guidelines

### 2.1.1 Introduction

The avionics industry requires that safety critical software be assessed according to strict certification authority<sup>1</sup> guidelines before it may be used on any commercial airliner. ARP 4754 and DO-178B are guidelines used both by the companies developing airborne equipment and by the certification authorities.

### 2.1.2 ARP 4754

ARP 4754 was defined in 1996 by the SAE (Society of Automotive Engineers).

This document discusses the certification aspects of highly integrated or complex systems installed on an aircraft, taking into account the overall aircraft operating environment and functions. The term "highly integrated" refers to systems that perform or contribute to multiple aircraft-level functions. The guidance material in this document was developed in the context of Federal Aviation Regulations (FAR) and Joint Airworthiness Requirements (JAR) Part 25. In general, this material is also applicable to engine systems and related equipment.

ARP 4754 addresses the total life cycle for systems that implement aircraft-level functions. It excludes specific coverage of detailed systems, including software and hardware design processes beyond those of significance in establishing the safety of the implemented system. More detailed coverage of the software aspects of design are dealt with in the DO-178B (RTCA)/ED12B (EUROCAE) document. Coverage of complex hardware aspects of design are dealt with in RTCA document DO-254.

### 2.1.3 DO-178B

DO-178B/ED-12 was first published in 1992 by RTCA (Requirements and Technical Concepts for Aviation) and EUROCAE (a non-profit organization addressing aeronautic technical problems). It was written by a group of experts from aircraft and aircraft equipment manufacturing companies and from certification authorities. It provides guidelines for the

1. For example, the United States Federal Aviation Administration (FAA), the European Aviation Safety Agency (EASA), Transport Canada, etc.

production of software for airborne systems and equipment. The objective of the guidelines is to ensure that software performs its intended function with a level of confidence in safety that complies with airworthiness requirements.

These guidelines specify:

- Objectives for software life-cycle processes.

- Description of activities and design considerations for achieving those objectives.

- Description of the evidence indicating that the objectives have been satisfied.

# 2.1.4 Relationship between ARP 4754 and DO-178B

ARP 4754 and DO-178B are complementary guidelines:

- ARP 4754 provides guidelines for the system-level processes.

- DO-178B provides guidelines for the software life-cycle processes.

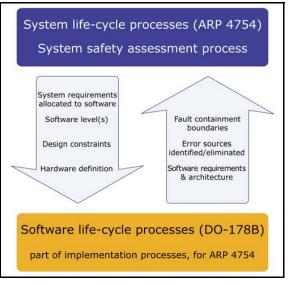

The information flow between the system and software processes are summarized in Figure 2.1.

Figure 2.1: Relationship between ARP 4754 and DO-178B processes

ARP 4754 (§A.2.1) identifies the relationships with DO-178B in the following terms:

"The point where requirements are allocated to hardware and software is also the point where the guidelines of this document transition to the guidelines of DO-178B (for software), DO-254 (for complex hardware), and other existing industry guidelines. The following data is passed to the software and hardware processes as part of the requirements allocation:

- a Requirements allocated to hardware.

- b Requirements allocated to software.

- c Development assurance level for each requirement and a description of associated failure condition(s), if applicable.

- d Allocated failure rates and exposure interval(s) for hardware failures of significance.

- e Hardware/software interface description (system design).

- f Design constraints, including functional isolation, separation, and partitioning requirements.

- g System validation activities to be performed at the software or hardware development level, if any.

- h System verification activities to be performed at the software or hardware development level."

### 2.1.5 Development assurance levels

ARP 4754 defines guidelines for the assignment of so-called Development Assurance Levels to the system, to its components, and to software, with regard to the most severe failure condition of the corresponding part.

ARP 4754 and DO-178B define in common five "Development Assurance Levels" as summarized in the following table:

| Level                                                                                                                          | Effect of anomalous behavior                                                                                              |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A                                                                                                                              | Catastrophic failure condition for the aircraft ( <i>e.g.</i> , aircraft crash).                                          |  |  |  |

| В                                                                                                                              | <b>B</b> Hazardous/severe failure condition for the aircraft ( <i>e.g.</i> , several persons could be injured)            |  |  |  |

| C Major failure condition for the aircraft (e<br>flight management system could be dow<br>pilot would have to do it manually). |                                                                                                                           |  |  |  |

| D                                                                                                                              | Minor failure condition for the aircraft ( <i>e.g.,</i> some pilot-ground communications could have to be done manually). |  |  |  |

| Level | Effect of anomalous behavior |

|-------|------------------------------|

|       |                              |

Е

No effect on aircraft operation or pilot workload (*e.g.*, entertainment features may be down).

This handbook mainly targets level A, B and C software.

### 2.1.6 Objective-oriented approach

The approach in DO-178B is based on the formulation of appropriate objectives and on the verification that these objectives have been achieved. The DO-178B authors acknowledged that objectives are more essential and stable than specific procedures. The ways of achieving an objective may vary from one company to another; and they may vary over time with the evolution of methods, techniques, and tools. DO-178B never states that one should use design method X, coding rules Y, or tool Z. DO-178B does not even impose a specific life cycle.

The general approach is the following:

- Ensure that appropriate objectives are defined. For instance:

- a Development assurance level of the software.

- b Design standards.

- Define procedures for the verification of the objectives. For instance:

- a Verify that design standards are met and that the design is complete, accurate, and traceable.

- b Develop and apply requirements-based test cases.

- Define procedures for verifying that the abovementioned verification activities have been performed satisfactorily. For instance:

- a Remarks of document reviews are answered.

- b Coverage of requirements by testing is achieved.

### 2.1.7 DO-178B processes overview

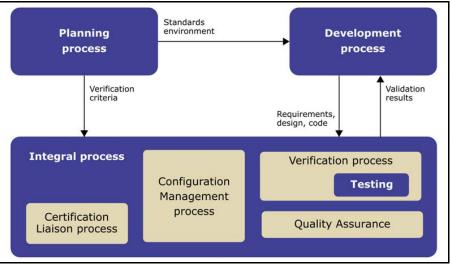

DO-178B structures activities as a hierarchy of "processes", as illustrated in <u>Figure 2.2</u>. The term "process" appears several times in the document. DO-178B defines three top-level groups of processes:

• The software planning processes that define and coordinate the activities of the software development and integral processes for a project.

These processes are beyond the scope of this handbook.

- The software development processes that produce the software product. These processes are the software requirements process, the software design process, the software coding process, and the integration process.

- The integral processes that ensure the correctness, control, and confidence of the software life-cycle processes and their outputs. The integral processes are the software verification process, the software configuration management process, the software quality assurance process, and the certification liaison process. The integral processes are performed concurrently with the software development processes throughout the software life cycle.

Figure 2.2: DO-178B life-cycle processes structure

In the remainder of this document we will focus on the development and verification processes.

### 2.2 DO-178B Development Processes

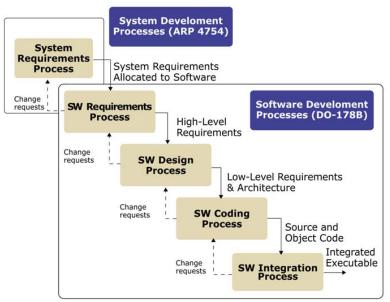

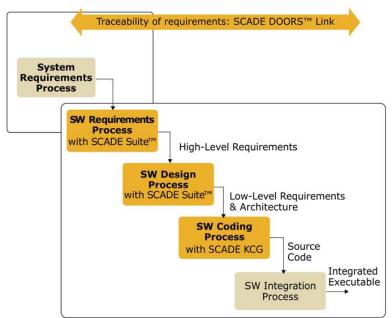

The software development processes, as illustrated below in <u>Figure 2.3</u>, are composed of:

• The software requirements process, which produces the high-level requirements (HLR);

- The software design process, which usually produces the low-level requirements (LLR) and the software architecture through one or more refinements of the HLR;

- The software coding process, which produces the source code and object code;

- The integration process, which produces object code and builds up to the integrated system or equipment.

Figure 2.3: DO-178B development processes

The high-level software requirements (HLR) are produced directly through analysis of system requirements and system architecture and their allocation to software. They include specifications of functional and operational requirements, timing and memory constraints, hardware and software interfaces, failure detection and safety monitoring requirements, as well as partitioning requirements.

The HLR are further developed during the software design process, thus producing the software architecture and the low-level requirements (LLR). These include descriptions

of the input/output, the data and control flow, resource limitations, scheduling and communication mechanisms, as well as software components. If the system contains "deactivated" code (see <u>Appendix B</u>), the description of the means to ensure that this code cannot be activated in the target computer is also required.

Through the coding process, the low-level requirements are implemented as source code.

The source code is compiled and linked by the integration process up to an executable code linked to the target environment.

At all stages traceability is required: between system requirements and HLR; between HLR and LLR; between LLR and code; and also between tests and requirements.

### 2.3 DO-178B Verification Processes

## **2.3.1 Objectives of software verification**

The purpose of the software verification processes is "to detect and report errors that may have been introduced during the software development processes." DO-178B defines verification

objectives, rather than specific verification techniques, since the later may vary from one project to another and/or over time.

Testing is part of the verification processes, but verification is not just testing: The verification processes also rely on reviews and analyses. Reviews are qualitative and generally performed once, whereas analyses are more detailed and should be reproducible (*e.g.*, compliance with coding standards).

Verification activities cover all the processes, from the planning process to the development process; there are even verifications of the verification activities.

# **2.3.2 Reviews and analyses of the high-level requirements**

The objective of reviews and analyses is to confirm that the HLRs satisfy the following:

- a Compliance with the system requirements.

- b Accuracy and consistency: each HLR is accurate and unambiguous and sufficiently detailed; requirements do not conflict with each other.

- c Compatibility with target computer.

- d Verifiability: each HLR has to be verifiable.

- e Compliance with standards as defined by the planning process.

- f Traceability with the system requirements.

- g Algorithm accuracy.

### **2.3.3 Reviews and analyses of the lowlevel requirements**

The objective of these reviews and analyses is to detect and report requirement errors that may have been introduced during the software design process. These reviews and analyses confirm that the software low-level requirements satisfy these objectives:

- a **Compliance with high-level requirements**: the software low-level requirements satisfy the software high-level requirements.

- b Accuracy and consistency

- c **Compatibility with the target computer**: no conflicts exist between the software requirements and the hardware/software features of the target computer, especially the use of resources (such as bus loading), system response times, and input/output hardware.

- d **Verifiability**: each low-level requirement can be verified.

- e **Compliance with the Software Design Standards** (defined by the software planning process).

- f **Traceability**: the objective is to ensure that all high-level requirements were taken into account in the development of the low-level requirements.

- g **Algorithm aspects**: ensure the accuracy and behavior of the proposed algorithms, especially in the area of discontinuities (*e.g.*, mode changes, crossing value boundaries).

- h **The SW architecture is compatible with the HLR**, it is consistent and compatible with the

target computer, is verifiable, and conforms to standards.

i Software partitioning integrity is confirmed.

# 2.3.4 Reviews and analyses of the source code

The objective is to detect and report errors that may have been introduced during the software coding process. These reviews and analyses confirm that the outputs of the software coding process are accurate, complete, and can be verified. Primary concerns include correctness of the code with respect to the LLRs and the software architecture, and compliance with the Software Code Standards. These reviews and analyses are usually confined to the source code. The topics should include:

- a **Compliance with the low-level requirements**: The source code is accurate and complete with respect to the software low-level requirements; no source code implements an undocumented function.

- b **Compliance with the software architecture**: The source code matches the data flow and control flow defined in the software architecture.

- c **Verifiability**: The source code does not contain statements and structures that cannot be verified, and the code does not have to be altered to test it.

- d **Compliance with standards**: The Software Code Standards (defined by the software planning process) were followed during the development of the code, especially complexity restrictions and code constraints that would be

consistent with the system safety objectives. Complexity includes the degree of coupling between software components, the nesting levels for control structures, and the complexity of logical or numeric expressions. This analysis also ensures that deviations to the standards are justified.

- e **Traceability**: The source code implements all software low-level requirements.

- f Accuracy and consistency: The objective is to determine the correctness and consistency of the source code, including stack usage, fixed-point arithmetic overflow and resolution, resource contention, worst-case execution timing, exception handling, use of non initialized variables or constants, unused

variables or constants, and data corruption due to task or interruption conflicts.

#### 2.3.5 Software testing process

Testing of avionics software has two complementary objectives. One objective is to demonstrate that the software satisfies its requirements. The second objective is to demonstrate with a high degree of confidence that all errors, which could lead to unacceptable failure conditions as determined by the system safety assessment process, have been removed.

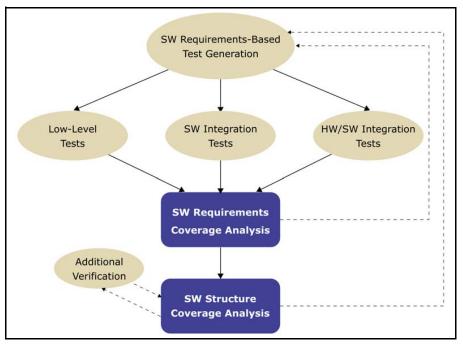

Figure 2.4: DO-178B testing processes

There are three types of testing activities:

- **Low-level testing**: to verify the implementation of software low-level requirements.

- **Software integration testing**: to verify the interrelationships between software requirements and components and to verify the implementation of the software requirements and software components within the software architecture.

- Hardware/software integration testing: to verify correct operation of the software in the target computer environment.

As shown in <u>Figure 2.4</u>, DO-178B dictates that all test cases, including low-level test cases, be requirements-based; namely that all test cases be defined from the requirements, and never from the code.

#### **TEST COVERAGE ANALYSIS**

Test coverage analysis is a two-step activity:

- Requirements-based test coverage analysis determines how well the requirement-based testing covered the software requirements. The main purpose of this step is to verify that <u>all requirements</u> have been implemented.

- 2 Structural coverage analysis determines which code structures were exercised by the requirements-based test procedures. The main purpose of this step is to verify that <u>only the requirements</u> have been implemented; for instance, there are <u>no</u> <u>unintended functions</u> in the implementation (DO-248, FAQ#43). Note that requirements coverage is an absolute prerequisite to this step.

#### STRUCTURAL COVERAGE RESOLUTION

If structural coverage analysis reveals structures that were not exercised, resolution is required:

- If it is due to shortcomings in the test cases, then test cases should be supplemented or test procedures changed.

- If it is due to inadequacies in the requirements, then the requirements must be changed and test cases developed and executed.

- If it is dead code (it cannot be executed, and its presence is an error), then this code should be removed and an analysis performed to assess the effect and the needs for reverification.

- If it is deactivated code (it cannot be executed, but its presence is not an error):

- If it is not intended to be executed in any configuration, then analysis and testing should show that the means by which such code could be executed are prevented, isolated, or eliminated.

- If it is only executed in certain configurations, the operational configuration for execution of this code should be established and additional test cases should be developed to satisfy coverage objectives.

### STRUCTURAL COVERAGE CRITERIA

The structural coverage criteria that have to be achieved depend on the software level:

- Level C: <u>Statement coverage is required</u>; this means that every statement in the program has been exercised.

- Level B: Decision coverage is required; this means that every decision has taken all possible outcomes at least once (*e.g.*, then/else for an "if" construct) and that every entry and exit point in the program has been invoked at least once.

- Level A: <u>MC/DC (Modified Condition/Decision</u> <u>Coverage) is required;</u> this means that:

- Every entry and exit point in the program has been invoked at least once.

- Every decision has taken all possible outcomes.

- Each condition in a decision has been shown to independently affect that decision's outcome (this is shown by varying just that condition, while holding fixed all other possible conditions).

For instance, the following fragment requires four test cases, as shown below in <u>Table 2.1</u>.

```

If A or (B and C)

Then do action1

Else do action2

Endif

```

| Case | Α     | В     | С     | Outcome |

|------|-------|-------|-------|---------|

| 1    | FALSE | FALSE | TRUE  | FALSE   |

| 2    | TRUE  | FALSE | TRUE  | TRUE    |

| 3    | FALSE | TRUE  | TRUE  | TRUE    |

| 4    | FALSE | TRUE  | FALSE | FALSE   |

#### Table 2.1: Example of test cases

## 2.4 What Are the Main Challenges in the Development of Airborne Software?

This section introduces the main challenges that have to be faced when developing safety-related airborne software.

## **2.4.1 Avoiding multiple descriptions of the software**

In such a development life cycle, the software is described in several phases and documents:

- Software high-level requirements (HLR)

- Software architecture design and low-level requirements (LLR)

- Software source code

At each step, it is important to avoid as much as possible rewriting the software description.

This rewriting would not only be expensive, it would also be error-prone. And there is a major risk of inconsistencies between different descriptions. This necessitates devoting a significant effort to verifying compliance of each level with the previous level. The purpose of many activities, as described in [DO-178B], is to detect the errors introduced during transformations from one written form to another.

# **2.4.2 Preventing ambiguity and lack of accuracy in specifications**

Requirements and design specifications are traditionally written in some natural language, possibly complemented by non formal figures and diagrams. It is an everyday experience that natural language is subject to interpretation, even when it is constrained by requirements standards. Its inherent ambiguity can lead to different interpretations depending on the reader.

This is especially true for the dynamic behavior: for instance, how to interpret the combination of fragments from several sections of a document, such as "A raises B," "if both B and C occur, then set D," "if D or Z are active, then reset A?"

### 2.4.3 Avoiding low-level requirements and coding errors

Coding is the last transformation in a traditional development life cycle. It takes as input the last formulation in natural language (or pseudocode).

The programmers generally have a limited understanding of the system, which makes it vulnerable to ambiguities in the specification. Moreover, the code they produce is generally not understandable by the author of the system or high-level requirements.

In the traditional approach, the combined risk of interpretation error and coding errors is so high that a major part of the life-cycle verification effort is consumed by code testing.

# 2.4.4 Allowing for an efficient implementation of code on target

Code that is produced must be simple, deterministic, and efficient. It should require as few resources as possible, in terms of memory and execution time. It should be easy and efficient to retarget to a given processor.

# 2.4.5 Finding specification and design errors as early as possible

A significant number of specification and design errors are only detected during software integration testing.

One reason is that the requirement/design specification is often ambiguous and subject to interpretation. Another reason is that it is difficult for a human reader to understand details regarding dynamic behavior of the software without being able to exercise it. And the main reason is that, in a traditional process, this is the first time where one can exercise the software. This is very late in the process.

When a specification error can only be detected during the software integration phase, the cost of fixing it is much higher than if it had been detected during the specification phase.

## 2.4.6 Lowering the complexity and cost of updates

There are many sources of changes in the software, ranging from bug fixing, function improvement to the introduction of new functions.

When something has to be changed in the software, all products of the software life cycle have to be updated consistently, and all verification activities must be performed accordingly.

### 2.4.7 Improving verification efficiency

The level of verification for safety-related airborne software is much higher than for other non safety-related commercial software. For Level A software, the overall verification cost (including testing) may account for up to 80% of the budget. Verification is also a bottleneck for the project completion. So, clearly, any change in the speed and/or cost of verification has a major impact on the project time and budget. The objective of this document is to show how to retain a complete and thorough verification and validation process, while dramatically improving the efficiency of this process. The methods we will describe reach at least the level of quality achieved by traditional means, by optimizing the whole development process.

## 2.4.8 Providing an efficient way to store Intellectual Property (IP)

A significant part of the aircraft or equipment company's know-how resides in its software. It is therefore of utmost importance to provide tools and methods to efficiently store and access Intellectual Property (IP) relative to these safetyrelated systems. Such IP vaults will contain:

- Textual system and software requirements

- Graphical models of the software requirements (*e.g.*, regulation laws)

- Source code

- Test cases

- Other

## 3. Model-Based Development with SCADE Suite and KCG

### 3.1 What Is SCADE?

#### SCADE ORIGIN AND APPLICATION DOMAIN

The name SCADE stands for "Safety-Critical Application Development Environment." This name is used both for the SCADE notation and for the SCADE Suite software development environment. Its purpose is to create a bridge between control engineering and software engineering activities.

SCADE has been designed from the beginning for the development of safety-critical software. It relies on the theory of languages for real-time applications and, in particular, on the Lustre and Esterel languages as described in [LUSTRE] and [Esterel] in <u>Appendix B</u>. From the beginning, it has been designed with companies developing safety-critical software.

SCADE has been used from the start on an industrial basis for the development of safetycritical software such as flight control (Airbus, Eurocopter), nuclear power plant control (Schneider Electric), and railway switching systems (CSEE Transport).

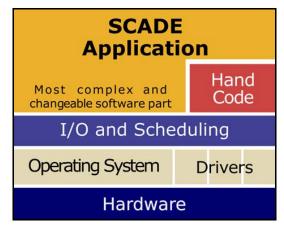

SCADE addresses the applicative part of hard real-time software, as illustrated in <u>Figure 3.1</u>. This is usually the most complex and

changeable aspect of software, containing complex decision logic, filters, and control laws. It typically represents 60% to 80% of the software embedded in an airborne computer.

Figure 3.1: SCADE addresses the applicative part of software

## A BRIDGE BETWEEN CONTROL ENGINEERING AND SOFTWARE ENGINEERING

Control engineers and software engineers typically use quite different notations and concepts:

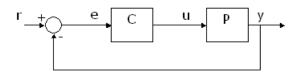

• Control engineers describe systems and their controllers using block diagrams and transfer functions (s form for continuous time, z form for discrete time), as shown below in Figure 3.2.

$X(z) = \sum_{n = -\infty}^{\infty} x(n) z^{-n}$  (bilateral z transform)

Figure 3.2: Control engineering view of a Controller

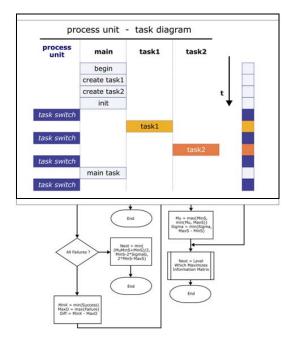

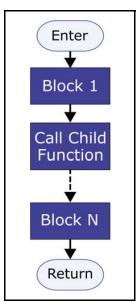

• Software engineers describe their programs in terms of tasks, flowcharts, and algorithms, as shown below in Figure 3.3.

Figure 3.3: Software engineering view of a Controller

These differences make translation from control engineering specifications to software engineering specifications complex, expensive, and error-prone.

To address this problem, SCADE offers rigorous software constructs that reflect control engineering constructs:

- Its data flow structure fits the block diagram approach.

- Its time operators fit the z operator of control engineering. For instance, z<sup>-1</sup>, the operator of control engineering (meaning a unit delay), has an equivalent operator called "pre" in SCADE.

## 3.2 SCADE Modeling Techniques

# **3.2.1 Familiarity and accuracy reconciled**

SCADE Suite uses two specification formalisms that are familiar to control engineers:

- Block diagrams to specify the algorithmic part of an application, such as control laws and filters.

- Safe State Machines (SSM) to model the behavior.

What the modeling techniques of SCADE add is a very rigorous view of these well-known but often insufficiently defined formalisms. SCADE has a formal foundation and provides a precise definition of concurrency; it ensures that all programs generated from SCADE behave deterministically. SCADE allows for automatic generation of C code from these two formalisms.

We will now describe more precisely their characteristics and the way an application designed in SCADE executes on a target platform.

### 3.2.2 SCADE node

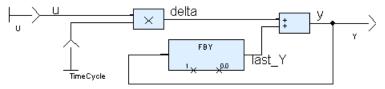

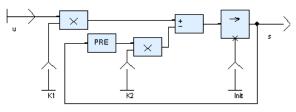

The basic building block in SCADE is called a node. A node is a user-defined function, built from lower-level nodes, down to predefined operators (*e.g.*, logical, arithmetic, delay, etc.) A node can be represented either graphically (see Figure 3.4), or textually (see Table 3.1 below).

Figure 3.4: Graphical notation for an integrator node

A node is a functional module made of the following components:

| Table 3.1: | Components | of SCADE | functional | modules: | nodes |

|------------|------------|----------|------------|----------|-------|

|------------|------------|----------|------------|----------|-------|

| Component                                                                              | ent Textual Notation for an Integrator Node                                         |                           |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------|

| Formal interface node IntegrFwd(U: real; hidden TimeCycle: real)<br>returns (Y: real); |                                                                                     | Arrows                    |

| Local variables<br>declarations                                                        |                                                                                     | Naming wires              |

| Equations                                                                              | <pre>delta = u * TimeCycle ; y = delta + last_Y ; last_Y = fby(y , 1 , 0.0) ;</pre> | Network of operator calls |

Actually, the textual notation is the semantic reference, which is stored in files and used by all tools; the graphical representation is a projection of the textual notation, taking into account secondary layout details.

The SCADE Editor supports a user-friendly structured editing mode for graphical and textual nodes.

A node is fully modular:

- There is a clear distinction between its interface and its body.

- There can be no side-effects from one node to another one.

- The behavior of a node does not depend on its context.

- A node can be used safely in several places in the same model or in another one.

# **3.2.3 Block diagrams for continuous control**

By "continuous control", we mean regular periodic computation such as: sampling sensors at regular time intervals, performing signalprocessing computations on their values, computing control laws and outputting the results. Data is continuously subject to the same transformation.

In SCADE, continuous control is graphically specified using block diagrams, such as the one illustrated in Figure 3.5 below.

Figure 3.5: A SCADE block diagram for roll management

Boxes compute mathematical functions, filters, and delays, while arrows denote data flowing between the boxes. Blocks that have no functional dependency compute concurrently, and the blocks only communicate through the flows. Flows may carry numeric, Boolean, or discrete values tested in computational blocks or acting on flow switches. SCADE blocks are fully hierarchical: blocks at a description level can themselves be composed of smaller blocks interconnected by local flows.

In <u>Figure 3.5</u> above, the RollCalculate block is hierarchical, and one can zoom into it using the SCADE Editor. Hierarchy makes it possible to break design complexity by a divide-andconquer approach and to design reusable library blocks.

SCADE is **modular**: the behavior of a node does not vary from one context to another.

The SCADE language is strongly typed, in the sense that each data flow has a type (Boolean, integer, real, arrays, etc.), and that type consistency in SCADE models is verified by the SCADE tools.

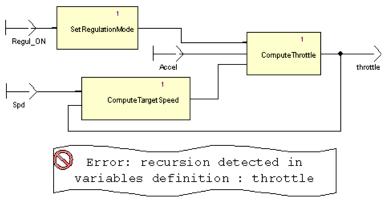

SCADE makes it possible to deal properly with issues of timing and causality. Causality means that if datum x depends on datum y, then y has to be available before the computation of x starts. A recursive data circuit poses a causality problem, as shown in Figure 3.6 below, where the "throttle" output depends on itself via the ComputeTargetSpeed and ComputeThrottle nodes. The SCADE semantic Checker detects this error and signals that this output has a recursive definition.

Figure 3.6: Detection of a causality problem

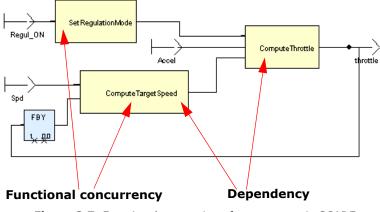

Inserting an FBY (delay) operator in the feedback loop solves the causality problem, since the input of the ComputeTargetSpeed block is now the value of "throttle" from the previous cycle, as shown in <u>Figure 3.7</u>.

Figure 3.7: Functional expression of concurrency in SCADE

The SCADE language provides a simple and clean expression of concurrency and functional dependency at the functional level, as follows:

- Blocks SetRegulationMode and ComputeTargetSpeed are functionally parallel; since they are independent, the relative computation order of these blocks does not matter (because, in SCADE, there are no sideeffects).

- ComputeThrottle functionally depends on an output of ComputeTargetSpeed. The SCADE Code Generator takes this into account: it generates code that executes

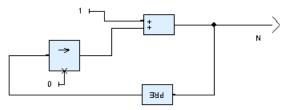

ComputeTargetSpeed before ComputeThrottle. The computation order is always up-to-date and correct, even when dependencies are very indirect and when the model is updated. The users do not need to spend time performing tedious and errorprone dependency analyses to determine the sequencing manually. They can focus on functions rather than on coding. Another important feature of the SCADE language is related to the initialization of flows (the -> operator), as illustrated in Figure 3.8, which models a counter.

Figure 3.8: Initialization of flows

The second argument of the + operator is 0 in step 1 (the initial value), and the previous value of flow N in steps 2, 3, ... In the absence of explicit initialization, SCADE emits warnings. Mastering initial values is indeed a critical subject for critical embedded software.

# **3.2.4 Safe State Machines for discrete control**

By "discrete control" we mean changing behavior according to external events originating either from discrete sensors and user inputs or from internal program events, for example, value threshold detection. Discrete control is used when the behavior varies qualitatively as a response to events. This is characteristic of modal human-machine interface, alarm handling, complex functioning mode handling, or communication protocols.

State machines have been very extensively studied in the past fifty years, and their theory is well understood. However, in practice, they have not been adequate even for medium-size applications, since their size and complexity tend to explode very rapidly. For this reason, a richer concept of hierarchical state machines has been introduced. SCADE hierarchical state machines are called Safe State Machines (SSMs).

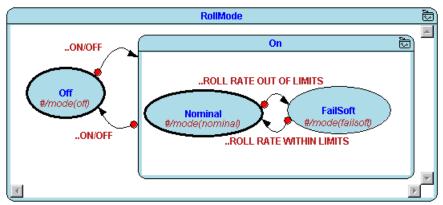

Figure 3.9: Safe State Machine for RollMode

SSMs are hierarchical. States can be either simple states or macro states, themselves recursively containing a full SSM. When a macro state is active, so are the SSMs it contains. When a macro state is exited by taking a transition out of its boundary, the macro state is exited and all the active SSMs it contains are preempted, whichever state they were in. State machines communicate by exchanging signals that may be scoped to the macro state that contains them. The definition of SSMs specifically forbids dubious constructs found in other hierarchical state machine formalisms: transitions crossing macro state boundaries, transitions that can be taken halfway and then backtracked, and so on. These are non modular, semantically ill defined, and very hard to figure out, hence inappropriate for safety-critical designs. They are usually not recommended by methodological guidelines.

## **3.2.5 Mixed continuous/discrete control**

Large applications contain cooperating continuous and discrete control parts. SCADE makes it possible to seamlessly couple both data flow and state machine styles. Most often, one includes SSMs into block-diagram design to compute and propagate functioning modes. Then, the discrete signals to which an SSM reacts and sends back, are simply transformed back and forth into Boolean data flows in the block diagram. The computation models are fully compatible. As an example, Figure 3.5 shows a data flow diagram where the RollMode block contains the Safe State Machine described in Figure 3.9.

## **3.2.6 Cycle-based intuitive computation model**

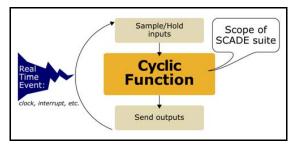

The cycle-based execution model of SCADE is a direct computer implementation of the ubiquitous sampling-actuating model of control engineering. It consists of performing a continuous loop of the form illustrated in Figure 3.10 below. In this loop, there is a strict alternation between environment actions and program actions. Once the input sensors are read, the cyclic function starts computing the cycle outputs. During that time, the cyclic function is *blind to environment changes*.<sup>2</sup> When the outputs are ready, or at a given time determined by a clock, the output values are fed back to the environment, and the program waits for the start of the next cycle.

Figure 3.10: The cycle-based execution model of SCADE Suite

In a SCADE block diagram specification, each block has a so-called clock (the event triggering its cycles) and all blocks act concurrently. Blocks can all have the same clock, or they can have different cycles, which subdivide a master cycle. At each of its cycle, a block reads its inputs and generates its outputs. If an output of block A is connected to an input of block B, and A and B have the same cycle, the outputs of A are used by B in the same cycle, unless an explicit delay is added between A and B. This is the essence of the semantics of SCADE.

SCADE SSMs have the very same notion of a cycle. For a simple state machine, a cycle consists of performing the adequate transition from the current state and outputting the transition output in the cycle, if any. Concurrent state machines communicate with each other, receiving the signals sent by other machines and

2. It is still possible for interruption service routines or other task to run, as long as they do not interfere with the cyclic function.

possibly sending signals back. Finally, block diagrams and SSMs in the same design also communicate at each cycle.

This cycle-based computation model carefully distinguishes between logical concurrency and physical concurrency. The application is described in terms of logically concurrent activities, block diagrams, or SSMs. Concurrency is resolved at code generation time, and the generated code remains standard sequential and deterministic *C* code, all contained within a very simple subset of this language. What matters is that the final sequential code behaves exactly as the original concurrent specification, which can be formally guaranteed. Notice that there is no overhead for communication, which is internally implemented using well-controlled shared variables without any context switching.

### 3.2.7 SCADE data typing

The SCADE language is strongly typed.

The following data types are supported;

- Predefined types: Boolean, Integer, Real, Character.

- Structured types:

- Structures make it possible to group data of different types. Example:

Ts = [x: int, y: real];

• Arrays group data of a homogeneous type. They have a static size. Example:

tab = real^3;

• Imported types that are defined in C or Ada (to interface with legacy software).

All variables are explicitly typed, and type consistency is verified by the SCADE semantic Checker.

#### **3.2.8 SCADE Suite as a model-based development environment**

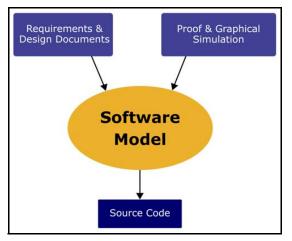

SCADE Suite is an environment for the development of safety-related avionics software. It supports a model-based development paradigm, as illustrated in Figure 3.11:

- The model is the software requirements: it is the unique reference in the project and it is based on a formal notation.

- Documentation is automatically and directly generated from the model: it is correct and up-to-date by construction.

- The model can be exercised by simulation using the same code as the embedded code.

- Formal proof techniques can be directly applied to the model to detect corner bugs or to prove safety properties.

- Code is automatically and directly generated from the model with the KCG 4.2 qualified automatic code generator: the code is correct and up-to-date by construction.

Figure 3.11: Model-based development with SCADE Suite and KCG 4.2

SCADE Suite applies the following "golden rules":

- Share unique, accurate specifications.

- **Do things once**: Do not rewrite descriptions from one activity to another; for instance, between software architecture and software system design, or between module design and code.

- **Do things right**: Detect errors in early stages and/or write "correct-by-construction" descriptions.

SCADE Suite enables the saving of a significant amount of verification effort, essentially because it supports a "correct-by-construction" process.

The remainder of this handbook explains how full benefit can be obtained using SCADE in a DO-178B project.

#### BENEFITS OF THE "DO THINGS ONCE" PRINCIPLE

The SCADE model formalizes a significant part of the software architecture and system design. It is written and maintained once in the project and shared among team members. Expensive and error-prone rewriting is thus avoided; interpretation errors are minimized. All members of the project team, from the specification team to the review and testing teams, will share the SCADE model as a reference.

This formal definition can even be used as a contractual requirement document with subcontractors. Basing the activities on an identical formal definition of the software may save a lot of rework, and acceptance testing is faster using simulation scenarios.