# NCERT Solutions for Class 12 Physics

## Chapter 14 Electronics Devices

#### **Question 1**.

In an n-type silicon, which of the following statement is true :

(a) Electrons are majority carriers and trivalent atoms are the dopants.

(b) Electrons are minority carriers and pentavalent atoms are the dopants.

(c) Holes are minority carriers and pentavalent atoms are the doplants.

(d) Holes are majority carriers and trivalent atoms are the dopants.

#### Answer:

(c) 'Holes are minority carriers and pentavalent atoms are the dopants in n type semiconductor.'

#### Question 2.

Which of the statements given in Exercise 1 is true for p-type semiconductors?

#### Answer:

(d) Holes are majority carriers and trivalent atoms are the dopants in p-type semiconductors.

#### Question 3.

Carbon, silicon and germanium have four valence electrons each. These are characterised by valence and conduction bands separated by energy band gap respectively equal to (Eg)c, (Eg)si and (Eg)Ge-

Which of the following statements is true?

(a) (Eg)Si < (Eg)Ge < (Eg)C

(b)(E)c<(Eg)Ge>(Eg)si

(c) (Eg)c > (Eg)si > (Eg)Ge

#### (d) (Eg)c = (Eg)si = (Eg)Ge

#### Answer:

(C) (Eg)c > (Eg)Si > (Eg)Ge. Energy band gap is maximum in carbon and least in germanium among the given elements.

#### **Question 4**.

In an unbiased p-n junction, holes diffuse from the p-region to n-region because

(a) free electrons in the n-region attract them.

(b) they move across the junction by the potential difference.

- (c) hole concentration in p-region is more as compared to n-region.

- (d) All the above.

#### Answer:

(c) hole concentration in p-region is more as compared to n-region because hole diffusion takes place from higher concentration to lower concentration.

#### **Question 5**.

When a forward bias is applied to a p-n junction, it

(a) raises the potential barrier

(b) reduces the majority carrier current to zero

- (c) lowers the potential barrier

- (d) none of the above.

#### Answer:

(c) lowers the potential barrier by cancelling the depletion layer.

#### **Question 6.**

#### For transistor action, which of the following statements are correct :

- (a) Base, emitter and collector regions should have similar size and doping concentrations.

- (b) The base region must be very thin and lightly doped.

(c) The emitter junction is forward biased and collector junction is reverse biased.

(d) Both the emitter junction as well as the collector junction are forward biased. **Answer:**

(b) and (c): The base region must be very thin, lightly doped and the emitter junction is forward biased whereas collector junction is reverse biased to avoid unnecessary diffusion of charge carrier in the base and also for proper amplification.

#### Question 7.

#### For a transistor amplifier, the voltage gain :

(a) remains constant for all frequencies.

- (b) is high at high and low frequencies and constant in the middle frequency range.

- (c) is low at high and low frequencies and constant at mid frequencies.

(d) None of the above.

#### Answer:

(c) is low at high and low frequencies and constant at mid frequencies as per frequency response of a transistor.

#### **Question 8**.

In half-wave rectification, what is the output frequency if the input frequency is 50 Hz. What is the output frequency of a full-wave rectifier for the same input frequency.

#### Answer:

A half wave rectifier rectifies only one half cycle of input A.C.

.'. frequency of the output A.C.

= frequency of input A.C. = 50 Hz A full wave rectifier rectifies both halve cycles of the A.C. input

.'. frequency of output A.C. = 2 x frequency of input A.C. = 2 x 50 = 100 Hz

#### **Question 9.**

For a CE-transistor amplifier, the audio signal voltage across the collector resistance of 2 kQ is 2 V. Suppose the current amplification factor of the transistor is 100, find the input signal voltage and base current, if the base resistance is 1 k $\Omega$ .

#### Answer:

Here  $R_0 = 2 k\Omega = 2000 \Omega$ ;  $\beta = 100$ ;  $R_i = 1$  $k\Omega = 1000 \Omega$ ;  $V_0 = 2V$ .  $\therefore$  voltage amplification factor

$$A_{0} = \frac{V_{o}}{V_{i}} = \beta \frac{R_{o}}{R_{i}}$$

$$\therefore \quad V_{i} \stackrel{\checkmark}{=} \frac{V_{o} \cdot R_{i}}{\beta R_{o}} = \frac{2 \times 1000}{100 \times 2000}$$

$$= 0.01 \text{ V}$$

Also

$$I_{b} = \frac{V_{i}}{R_{i}} = \frac{0.01}{1000}$$

$$= 1 \times 10^{-5} \text{ A}$$

$$= 1 \times 10^{-5} \times 10^{6} \text{ }\mu\text{A} = 10 \text{ }\mu\text{A}$$

#### **Question 10**.

Two amplifiers are connected one after the other in series (cascaded). The first amplifier has a voltage gain of 10 and the second has a voltage gain of 20. If the input signal is 0.01 volt, calculate the output ac signal.

#### Answer:

Here  $A_{\upsilon_1} = 10$  and  $A_{\upsilon_2} = 20$

$$\therefore$$

Net voltage gain  $A_{ij} = A_{ij} \times A_{ij}$

$$= 10 \times 20 = 200$$

Now using  $A_{\upsilon} = \frac{V_o}{V_i}$

$$\therefore \quad \mathbf{V}_o = \mathbf{A}_{\mathrm{v}} \ . \ \mathbf{V}_i = 0.01 \times 200 = 2 \ \mathbf{V}_i$$

#### **Question 11.**

A p-n photodiode is fabricated from a semiconductor with bandgap of 2.8 eV. Can it detect a wavelength of 6000 nm ?

#### Answer:

Here  $E_g = 2.8 \text{ eV} = 2.8 \times 1.6 \times 10^{-19} = 4.48 \times 10^{-19}$ <sup>19</sup> J ;  $\lambda = 6000 \text{ nm} = 6000 \times 10^{-9} \text{ m}$

$$\therefore \text{ energy, } \mathbf{E} = \frac{hc}{\lambda} = \frac{6.62 \times 10^{-34} \times 3 \times 10^8}{6000 \times 10^{-9}}$$

$$= 3.31 \times 10^{-20} \text{ J}$$

$$= \frac{3.31 \times 10^{-20}}{1.6 \times 10^{-19}} = 0.207 \, e\text{V}$$

Since the energy of the light photon is less than the bandgap energy of the p-n diode, it can not be detected.

#### Question 12.

The number of silicon atoms per m<sup>3</sup> is 5 x 10<sup>28</sup>. This is doped simultaneously with 5 x 10<sup>22</sup> atoms per m<sup>3</sup> of Arsenic and 5 x 10<sup>20</sup> per m<sup>3</sup> atoms of Indium. Calculate the number of electrons and holes. Given that  $n_i = 1.5 \times 10^{16} \text{ m}^3$ . Is the material n-type or p- type ?

#### Answer:

$$n_e = 5 \times 10^{22} - 5 \times 10^{20} = (5 - 0.05)10^{22}$$

= 4.95 × 10<sup>22</sup> m<sup>-3</sup>.

$$n_h = \frac{n_i^2}{n_e} = \frac{(1.5 \times 10^{16})^2}{4.95 \times 10^{22}}$$

= 4.55 × 10<sup>9</sup> m<sup>-3</sup>.

Since  $n \gg n_e$ , the semiconductor is an  $n_e$

Since  $n_e >> n_h$ , the semiconductor is an *n*-type semiconductor.

#### **Question 13**.

In an intrinsic semiconductor, the energy gap  $E_g$  is 1.2 eV. Its hole mobility is much smaller than electron mobility and independent of temperature. What are the ratio between conductivity at 600 K and that at 300 K? Assume that the temperature dependence of intrinsic carrier concentration  $n_i$  is given by

$$n_i = n_0 \exp\left(-\frac{E_g}{2k_BT}\right)$$

, where  $n_0$  is a constant.

#### Answer:

$$\frac{K_1}{K_2} = \frac{n_1}{n_2} = \frac{e^{\frac{-E_g}{2k_BT_1}}}{e^{\frac{-E_g}{2k_BT_2}}} = e^{\frac{E_g}{2k_B}} \left[\frac{1}{T_2} - \frac{1}{T_1}\right]$$

$$= \frac{1\cdot 2}{e^{2\times 8\cdot 6\times 10^{-5}}} \left[\frac{1}{300} - \frac{1}{600}\right]$$

$$= \frac{1\cdot 2}{e^{2\times 8\cdot 6\times 3\times 10^{-3}}} \left[\frac{1}{1} - \frac{1}{2}\right]$$

$$= \frac{1}{e^{8\cdot 6\times 10^{-2}}} = e^{11\cdot 6279}$$

$$= 1\cdot 12 \times 10^5 \approx 1 \times 10^5$$

Thus, conductivity of a semiconductor increases with rise in temperature.

#### Question 14.

In a P-n junction diode, the current I can be expressed as

$$I = I_0 \exp\left(\frac{eV}{2K_BT} - 1\right),$$

where  $I_0$  is reverse saturation current. V is the voltage across the diode and is positive for forwarding bias and negative for reverse bias, and I is the current through the diode,  $K_B$  is the Boltzmann constant (8.6 x 10<sup>-5</sup> eV/K) and T is the absolute temperature. If for a given diode  $I_0 = 5 x$ 10<sup>-12</sup> A and T = 300 K, then

(a) What will be the forward current at a forwarding voltage of 0.6 V?

(b) What will be the increase in the current if the voltage across the diode is increased to 0.7 V?

(c) What is the dynamic resistance?

(d) What will be the current if reverse bias voltage changes from 1 V to 2 V? **Answer:**

The statement of the given question is incorrect. The relation should be

#### **Question 15**.

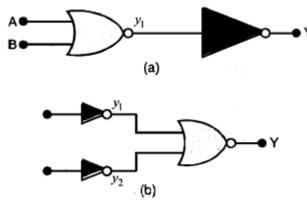

You are given the two circuits as shown in Figure. Show that circuit (a) acts as OR gate while circuit (b) acts as AND gate.

#### Answer:

In fig. (a),  $y_1 = \overline{A + B}$  and  $Y = \overline{y_1}$

$Y = \overline{A + B} = A + B$

(Boolean algebra)

Clearly fig. (a) represents an OR gate.

In fig. (b),  $Y = \overline{y_1 + y_2} = \overline{y_1} \cdot \overline{y_1}$ (Using de Morgan theorem) But  $y_1 = \overline{A}$  and  $y_2 = \overline{B}$  $\therefore$   $Y = \overline{y_1} \cdot \overline{y_1} = \overline{\overline{A}} \cdot \overline{\overline{B}} = A \cdot B$  which is an AND operation. Clearly fig. (b) represents an AND gate. Question 16.

Write the truth table for a NAND gate connected as given in Fig. Hence identify the exact logic operation carried out by these circuits.

#### Answer:

The NAND gate shown in the truth table has only one input. Therefore, the truth table is

| A | Α | $\mathbf{y} = \mathbf{A}.\mathbf{A}^{-}$ |

|---|---|------------------------------------------|

| 0 | 0 | 1                                        |

| 1 | 1 | 0                                        |

Since  $Y = A^{-}$  in this case, the circuit is actually a NOT gate with the truth table

| Α | Y |

|---|---|

|   |   |

| 0 | 1 |

|   |   |

| 1 | 0 |

|   |   |

#### Question 17.

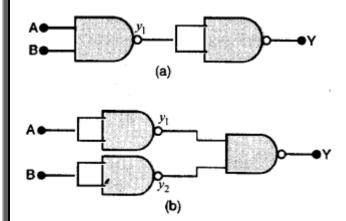

You are given two circuits as shown in Fig., which consist of NAND gates. Identify the logic operation carried out by the two circuits.

## Eduranka

#### Answer:

In the fig. (a),  $Y_1 = \overline{A \cdot B}$

$$Y = \overline{Y_1} = \overline{A \cdot B}$$

$$= A \cdot B$$

which is an AND operation.

Therefore, the fig. (a) represents an AND gate.

In fig. (b),  $Y_1 = \overline{A}, Y_2 = \overline{B}$   $Y = \overline{Y_1 \cdot Y_2} = \overline{\overline{A} \cdot \overline{B}}$   $= \overline{\overline{A}} + \overline{\overline{B}} = A + B$ = A + B which is an OR operation.  $\therefore$  Fig. (b) represents an OR gate.

#### **Question 18.**

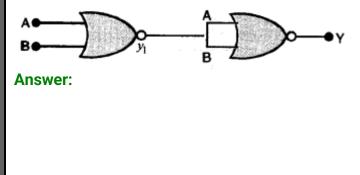

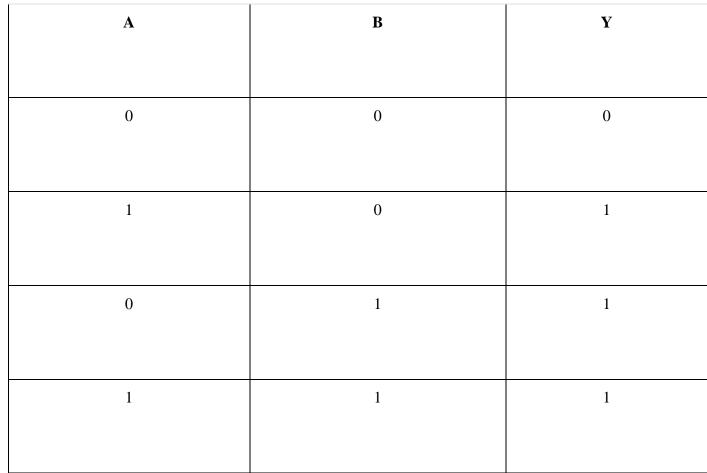

Write the truth table for circuit given in Fig. below consisting of NOR gates and identify the logic operation (OR, AND, NOT) which this circuit is performing.

Let  $y_1$  be the output which appears at the first operation of NOR gate.

Then  $y_1 = \overline{A + B}$  ...(1) This output is fed into an other NOR gate so that

$$Y = \overline{y_1 + y_1}$$

Now using Boolean Algebra,  $y_1 + y_1 = y_1$

*.*..

1

$$Y = \overline{y_1} = \overline{A + B}$$

(using eqn. (1))

= A + B which is an OR operation.

: the circuit is an OR gate and its truth lable is

#### Question 19.

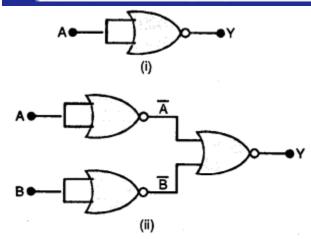

Write the truth table for the circuits given in Fig., consisting of NOR gates only. Identify the logic operations (OR, AND, NOT) performed by the two circuits

### Eduranko

#### Answer:

In fig. (i),  $Y = \overline{A + A}$ ... using Boolean algebra (De-Morgan theorem)

$Y = \overline{A} \cdot \overline{A} = \overline{A} \qquad (\because \overline{A} + \overline{B} = \overline{A} \cdot \overline{B})$

$\therefore$  this is a NOT operation. Therefore, fig. (i) represents a NOT gate.

In fig. (*ii*)  $Y = \overline{\overline{A} + \overline{B}} = \overline{\overline{A}} \cdot \overline{\overline{B}}$

(De Morgan theorem)

- =  $\mathbf{A} \cdot \mathbf{B}$  which is an AND operation.

- $\therefore$  the fig. (*ii*) represents an AND gate.