# Exceeding Expectations Using Intel® Processors

Nigel Forrester

## Today's talk

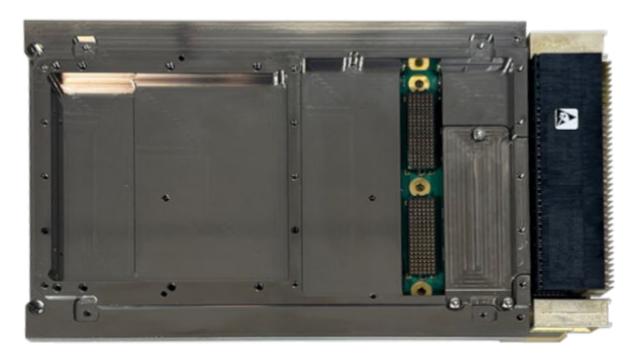

Looking from a vendor's perspective using Intel processor PICs as an example

Thinking about what customers need to do to maximize the performance of their applications

## Intel embedded processor swim lanes

Intel® Xeon® Processors

Intel® Core™ Ultra Processors

Intel Atom® Processors

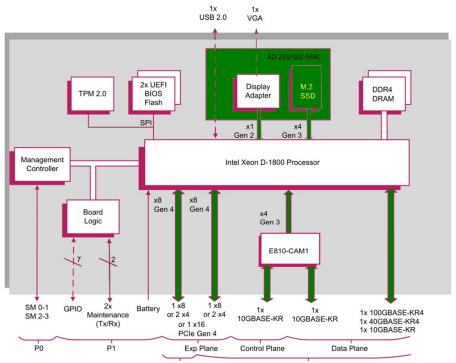

#### **Intel Xeon D Processors**

- Designed for maximum CPU performance

- All cores are equal

- All cores run at the same base frequency

- Higher power consumption ~45W to 130W

- Biggest challenge is in extracting max performance at a high card edge temperature

- The laws of physics limit what is achievable with a conduction-cooled 3U VPX PIC

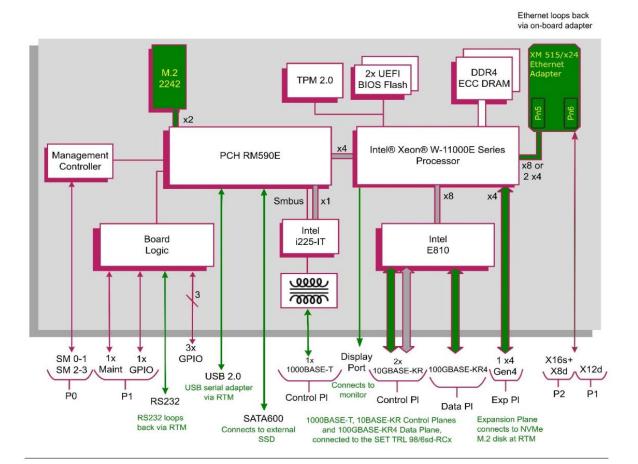

## Real examples

- TR MAx (2022)

- 10-core Xeon D-1746TER @ 67W

- All cores running at 2.0GHz

- Max card edge +70°C

- TR MDx (2024)

- 10-cores Xeon D-1848TER @ 57W

- All cores running at 1.9GHz

- Max card edge +85°C

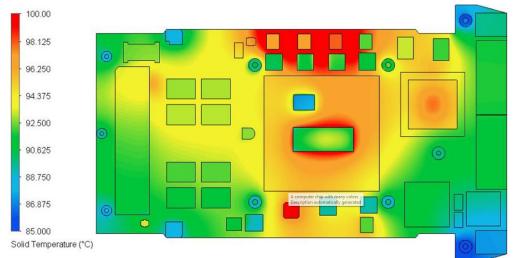

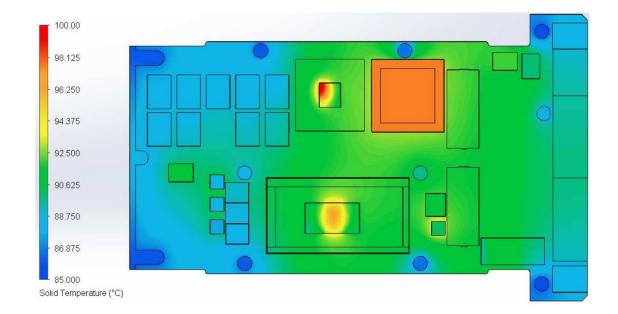

## **Xeon Thermal Testing**

- Hotspot analysis/measurement

- Low and High temperature storage and operating tests

## **Intel Xeon based PIC Summary**

- Relatively straightforward to qualify

- Fully deterministic with no throttling

- Ideal for Compute Intensive tasks

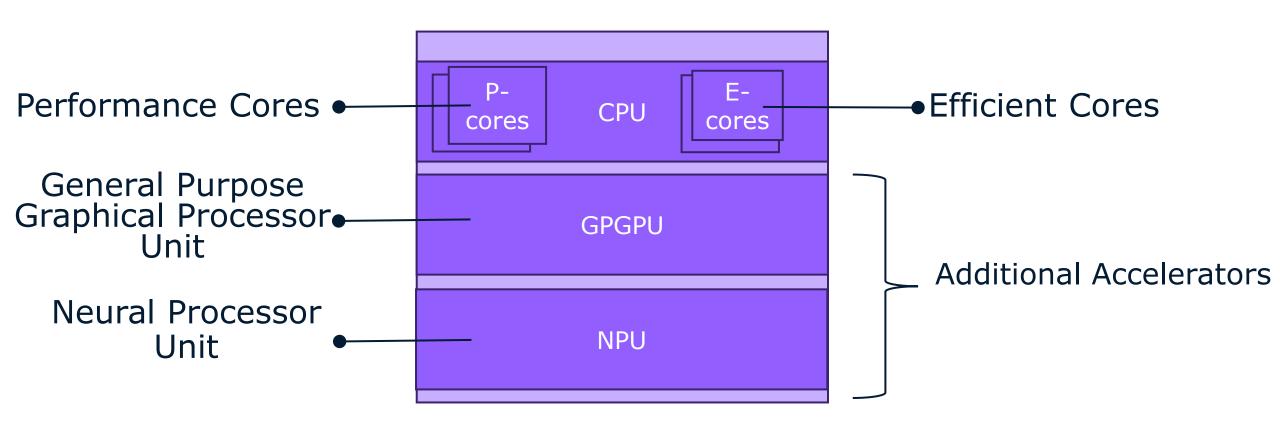

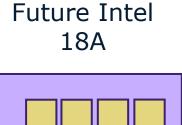

#### **Intel Core Ultra Processor**

Efficient Cores

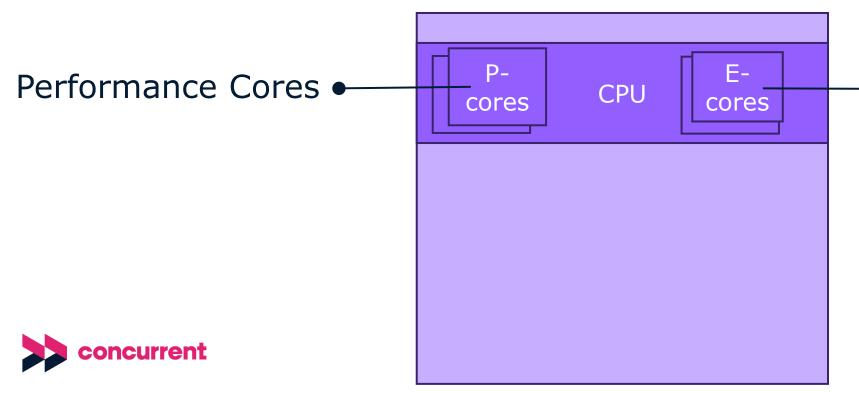

## **Hybrid CPU Architecture**

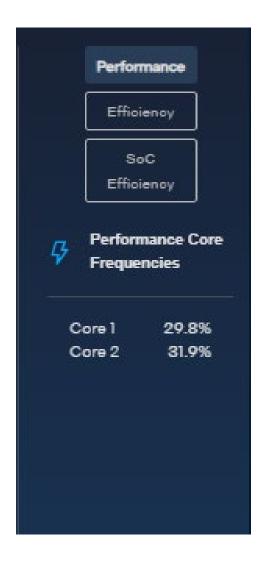

#### Performance Cores:

Physically larger, designed for highest frequencies Ideal for heavy single-threaded work Capable of hyper-threading

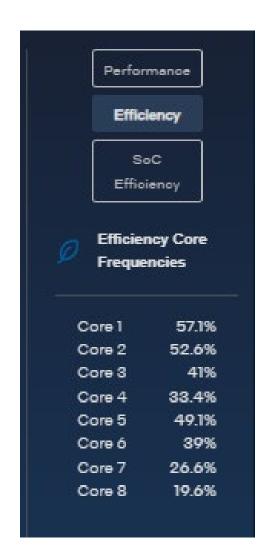

#### Efficient-cores:

Physically smaller, maximize performance-per-watt efficiency Ideal for scalable, multi-threaded performance

Optimized to run background tasks efficiently

Capable of running a single software thread

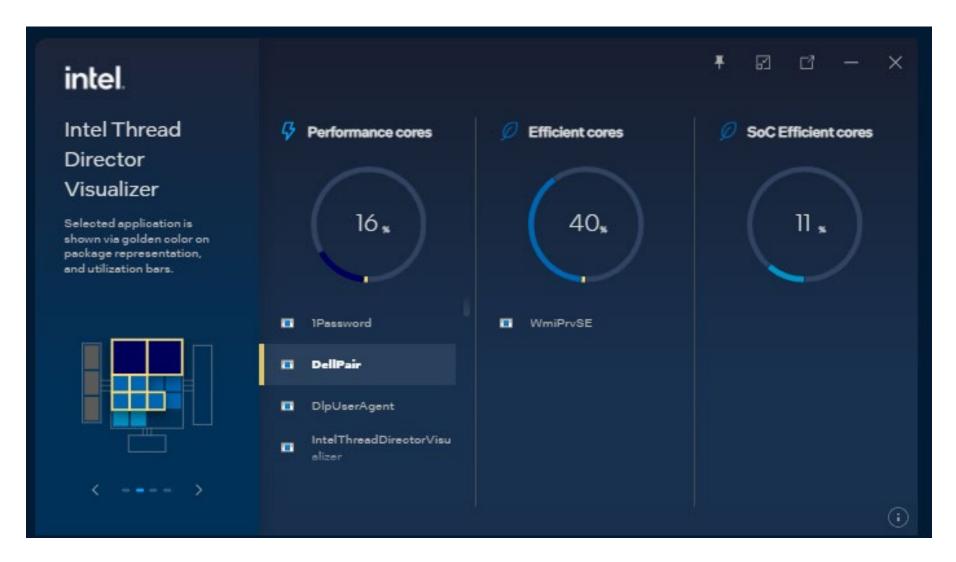

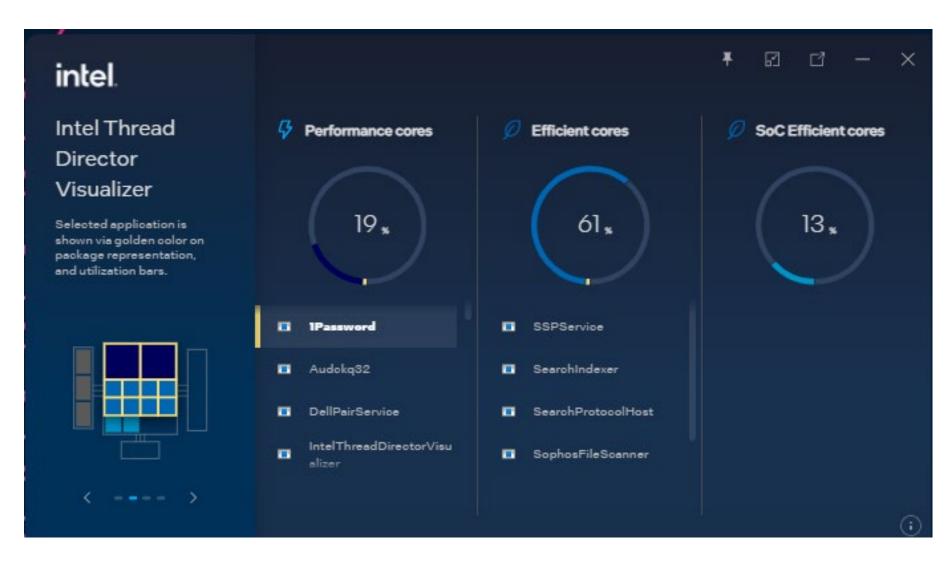

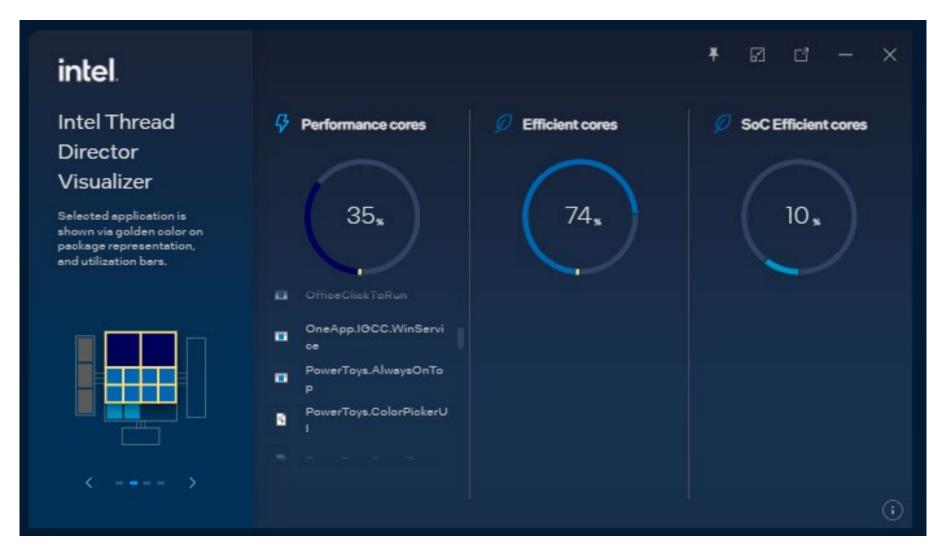

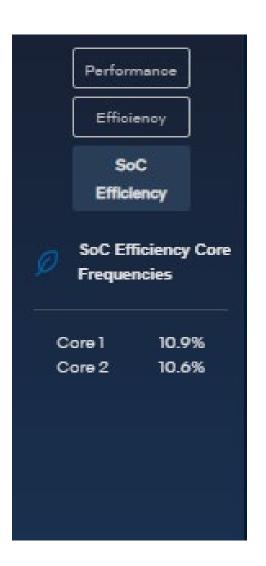

#### **Intel Thread Director**

- Monitors the instruction mix of each thread and the state of each core with nanosecond precision

- Provides runtime feedback to the OS (Windows/Linux) to make the optimal decision for any workload

- Dynamically adapts its guidance according to the Thermal Design Point (TDP) of the system, operating conditions, and power settings

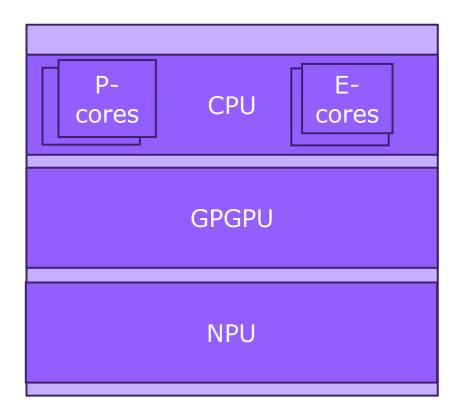

#### **Intel Core Ultra Processor**

## **AI Inferencing Applications**

## **Heterogeneous Computing Applications**

Write once in DPC++, deploy using any/all available compute resources

## **Core Processor Thermal Challenges**

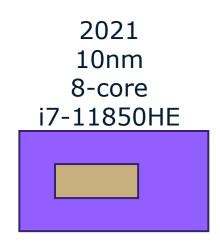

- Power density

- Similar overall power

- More CPU cores concentrated into a much smaller area of the overall die

## **Core Processor Thermal Challenges cont.**

- Determining a realistic load

- Minimize CPU Throttling

## An example

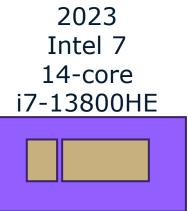

- TR LBE (2024)

- 14-cores i7-13800HE @ 35W

- Cores running around 1.6GHz

- Max card edge +85°C

## **Core testing**

## **Intel Core Ultra based PIC Summary**

- More challenging to qualify thermally

- Difficult to avoid throttling

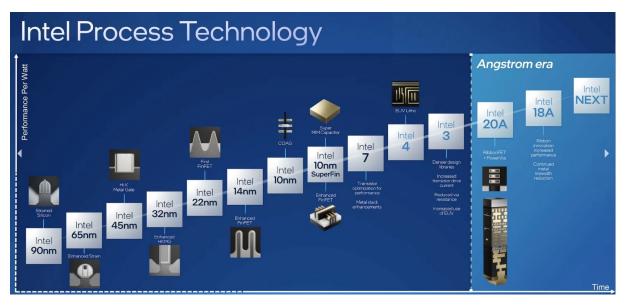

- New process nodes significantly increase power density

- Not easy to compare performance between vendors

# Questions?