## INTRODUCTION

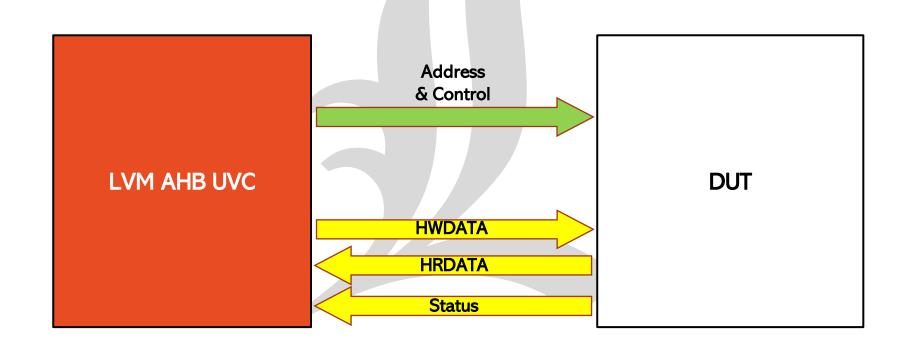

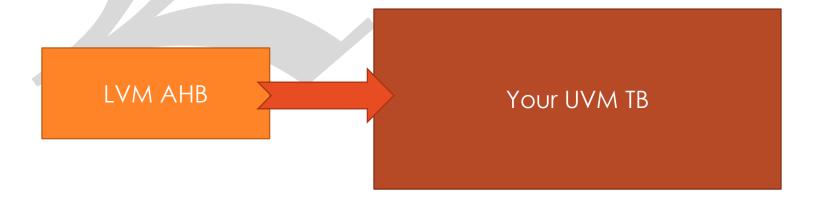

- This is an AHB UVC with full UVM compatibility.

- It has been coded to be robust, reusable, measurable, systematic and efficient, with easy debug-ability and user-friendly features.

- Objectives:

- To help create various AHB stimulus with ease (minimal codes).

- To shorten the time to bring up AHB UVM testbench with RAL.

- To provide users with high quality industry standard protocol checkers.

- To create an ideal platform for novice UVM users.

- To provide a low cost solution for AHB verification in the industry.

# THE LVM AHB

### EXAMPLE LVM AHB INSTALLATION

## WHY CHOOSING LVM VIP?

#### **User friendly**

Minimum lines of code to send packet.

Friendly for new UVM engineers.

API based UVC.

#### Reusable

Codes on lym VIP is highly reusable.

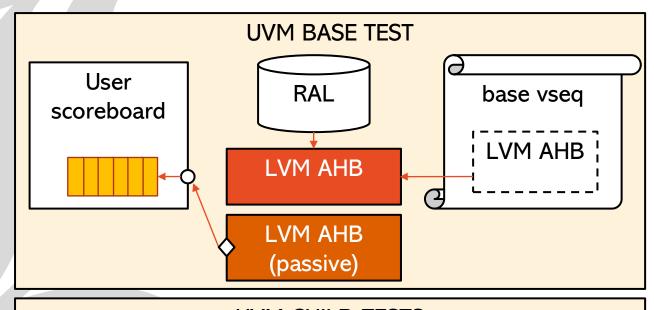

# Ease of Integration

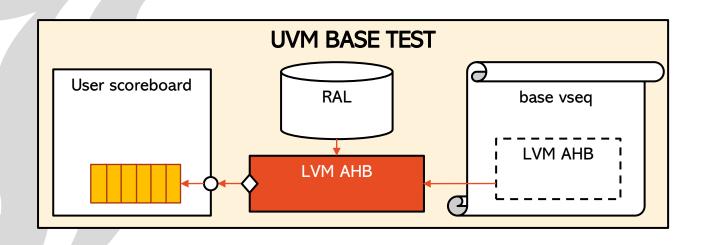

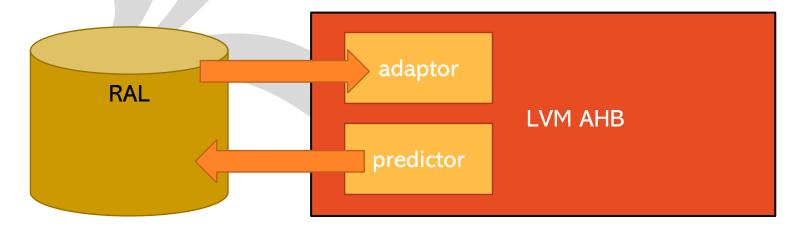

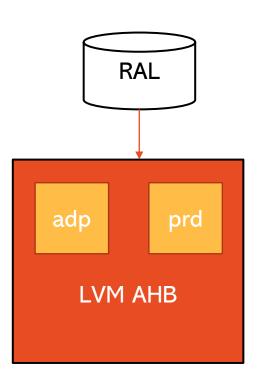

RAL-ready with adaptor and predictor.

Minimum steps to integrate.

#### Light weight

CPU efficient UVC.

#### Robust

Highly configurable. Parameterized signal width per instance.

# High debugability

Useful tracker log, interface signals.

#### Performance Analyzer

Performance analyser

#### **Strengths**

# Setup and Hold X injection

Inject X outside setup and hold window.

# Register Partial Access

Embedded register partial access where user just need 2 lines of codes to start it

# Register Burst Access

Embedded register burst access where user just need ~4 lines of codes to start it

# Strong & Strict Checker

Industry standard checker

embedded.

Support X injection at Read and

Write DATA for inactive lanes.

Embedded memory checker, RAL

access OK checker

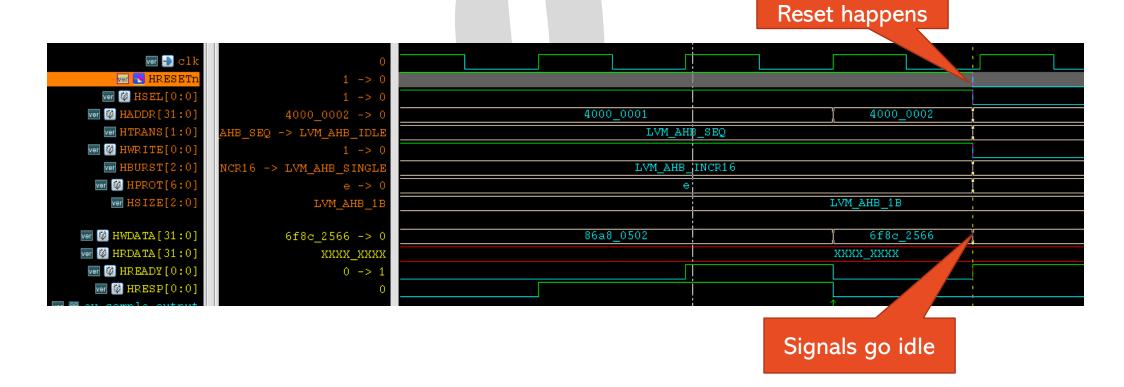

#### Reset aware

Support reset events.

# Ready testsuite

Provided multiple useful tests to verify AHB slaves DUT

# **USER FRIENDLY**

Integration and Configuration

### INTEGRATION & CONFIGURATION

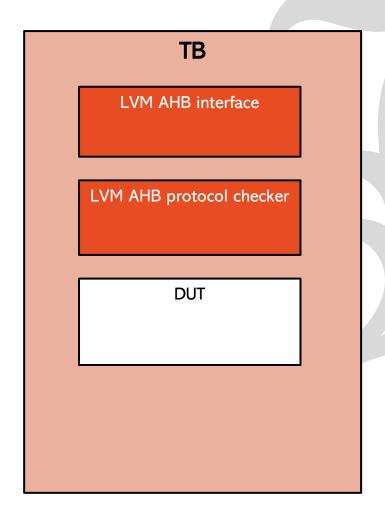

- Very easy to integrate, simpler than other vendor

- All steps are demonstrate in the self test testbench.

- Can configure different protocol per instance

- Can configure different signal width per instance

- Easily can on-off components on the fly.

- Just need to instantiate the UVC, no need to do anything on cfg class, sequence, adaptor, predictor etc

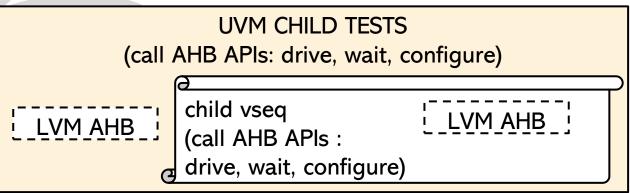

# **DRIVING PART**

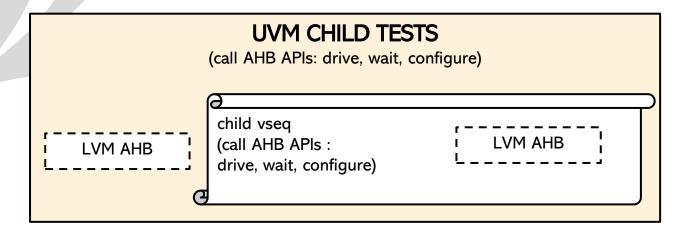

#### EASE OF DRIVING STIMULUS

- All fully pipelined.

- API based.

- Various API to control stimulus style

- Fully pipelined AHB traffic

- Wait and driving capabilities.

- Most API can be done in 1 line of code.

- Full examples at self-test uvm tests.

#### ADVANCED TECH WITH RAL

- Predictor and Adaptor are built in and connections syntax is ready.

- Support partial and full register access (individual accessible modes) for driving

- 8b accesses

- 16b accesses

- 32b accesses

- Predictor works for burst packets, and partial accesses packets

### SETUP AND HOLD X INJECTION

- Already supported X injection for window outside setup and hold time.

- Can be easily configured and can be turned OFF too.

### REUSABLE CODE

• As stimulus mostly done using UVC's API, the code is very reuse friendly, where just the UVC handle is needed.

```

m_ahb_env.s_write ( .HADDR(32'h2000_0000), .hwdata(32'h11111111) , .hresp(hresp), .hexokay(hexokay));

m_ahb_env.s_read ( .HADDR(32'h2000_0000), .hrdata(hrdata), .hresp(hresp), .hexokay(hexokay));

`uvm_info(msg_tag, $sformatf("hrdata='h%0h hresp='h%0h, hexokay='h%0h", hrdata, hresp, hexokay),UVM_DEBUG)

```

# **MONITORING PART**

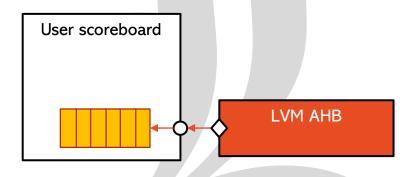

## SIMPLE SEQ ITEM RETRIEVAL

- Full code for seq item retrieval for all info needed is already part of example user scoreboard

- Already can be used for various high level scoreboard.

```

`uvm info(msg tag, $sformatf("Captured %0s transaction", captured item.HWRITE?"WRITE":"READ"), UVM MEDIUM)

`uvm info(msg tag, $sformatf("HBURST='h%0h HMASTLOCK='h%0h HPROT='h%0h HSIZE='h%0h HNONSEC='h%0h HEXCL='h%0h HMASTER='h%0h HAUSER='h%0h HWUSER='h%0h HRUSER='h%0h",

captured item.HBURST,

captured item. HMASTLOCK,

captured item. HPROT,

captured item. HSIZE,

captured item.HNONSEC,

// Per beat

captured item.HEXCL,

foreach (captured item.haddr[i]) begin

captured item.HMASTER

if(captured item.HWRITE == LVM AHB WRITE) begin

captured item. HAUSER,

captured item. HWUSER,

uvm info(msg tag, $sformatf("[Beat %-4d] HTRANS='h%0h HADDR='h%0h HWDATA='h%0h EFF='h%0h HRESP='h%0h",

captured item.HRUSER

, UVM MEDIUM)

captured item.htrans[i],

captured item.haddr [i],

captured item.HWDATA[i],

captured item.effective hwdata[i],

captured item. HRESP [i]

), UVM MEDIUM)

// the impact of the write for this beat

// it is printed for every 1 addr

`uvm info(msg tag, $sformatf("IMPACT"), UVM MEDIUM)

foreach (captured item.mem impact[i].addr[j])

`uvm info(msg tag, $sformatf("

%h <- %2h", captured item.mem impact[i].addr[j], captured item.mem impact[i].data[j]), UVM MEDIUM)</pre>

```

# **CHECKING PART**

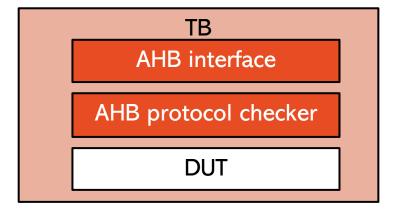

# EMBEDDED ARM PROTOCOL CHECKER

- Already integrated SVA from ARM for AHB protocol checker.

- Enhanced to become UVM\_ERROR when assertions fail.

ARM AHB protocol checker embedded (uvm)

LVM AHB

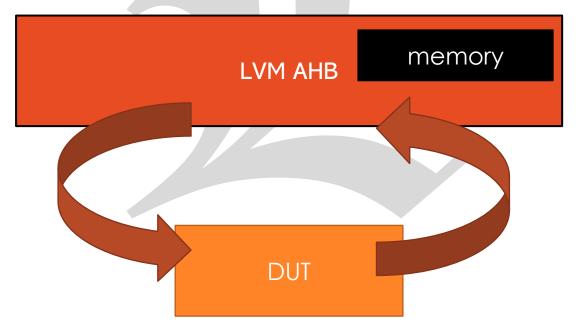

#### EMBEDDED MEMORY CHECKING

• Built in memory verification scoreboard, where

• all writes within memory range (configurable) will be keep tracked as new data (fulfil the conditions)

• All reads within memory range (configurable) will check data matching expectation (per last

written data)

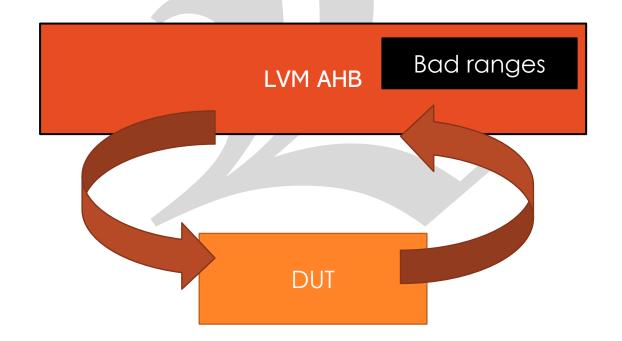

### OUT OF BOUND ADDRESS CHECKING

- Built in out of bound address verification scoreboard, where

- all writes outside valid address range will get HRESP = ERR (default value, user configurable)

- All reads outside valid address range will get HRESP = ERR (default value, user configurable)

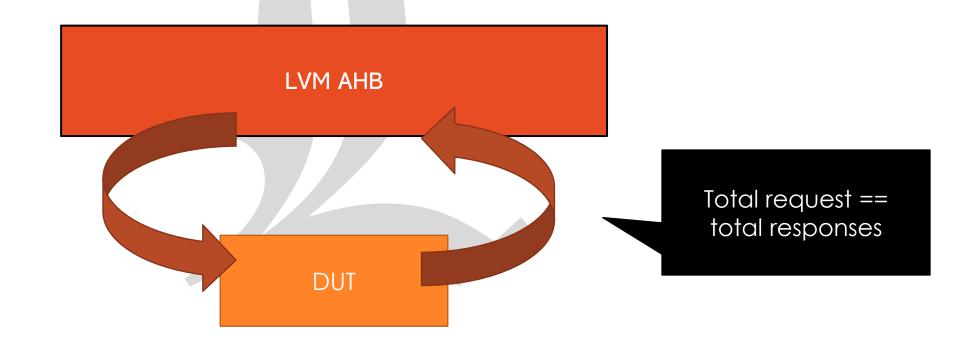

# AUTO ENSURE SLAVE COMPLETES ALL REQUESTS

• At the end of test, UVC will ensure slave does not missed out any read / write.

# **DEBUG PART**

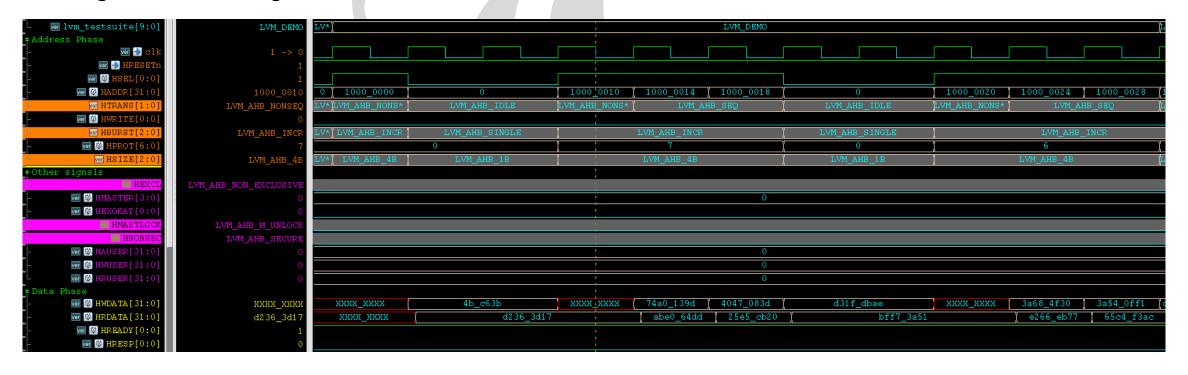

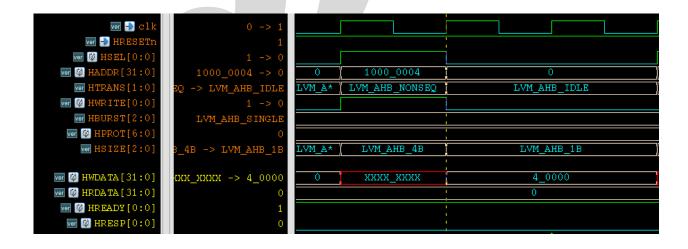

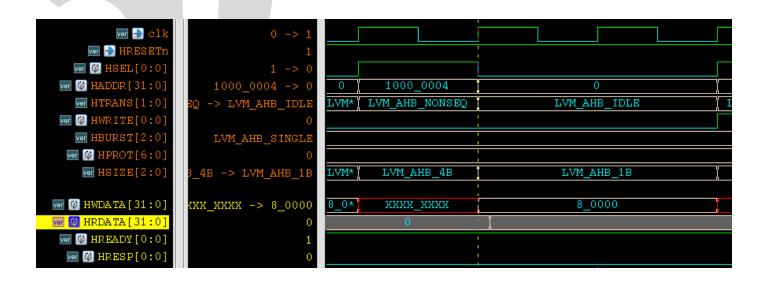

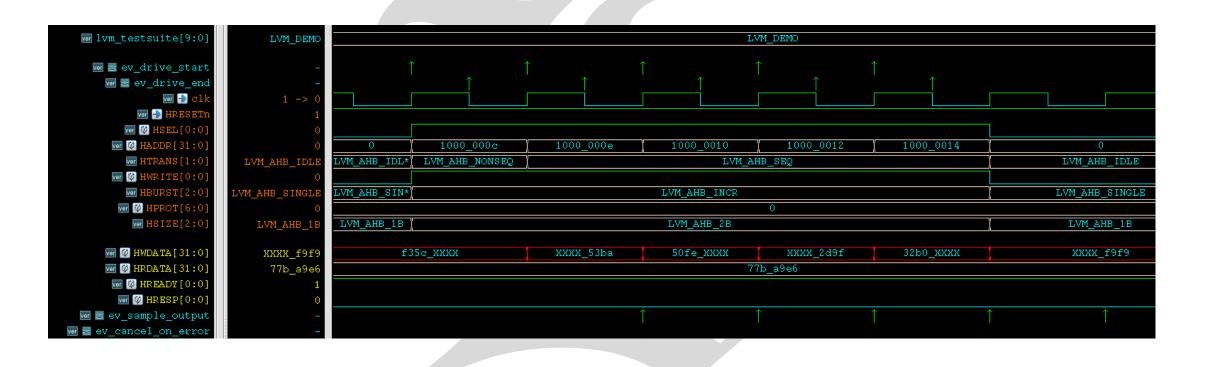

### **ENUM & DEBUG SIGNALS**

• Signals are designed in enum, to ease user to read the waveform

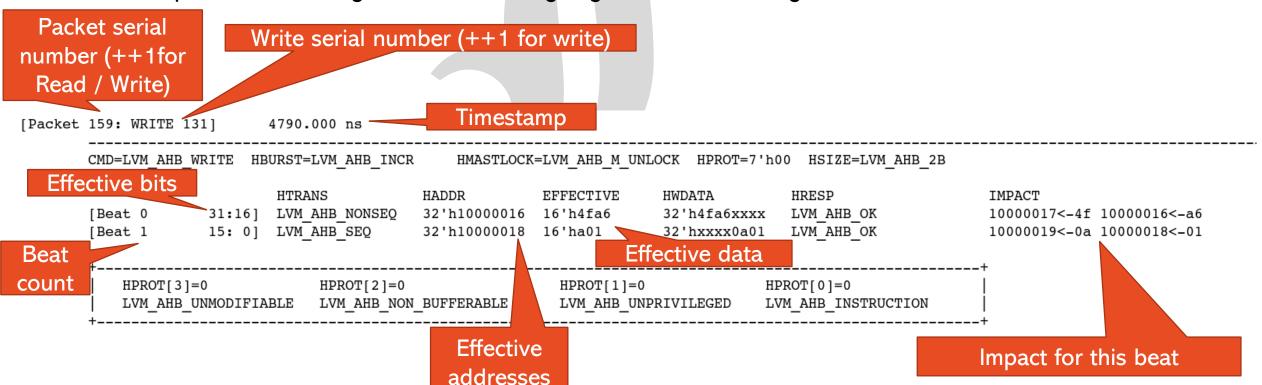

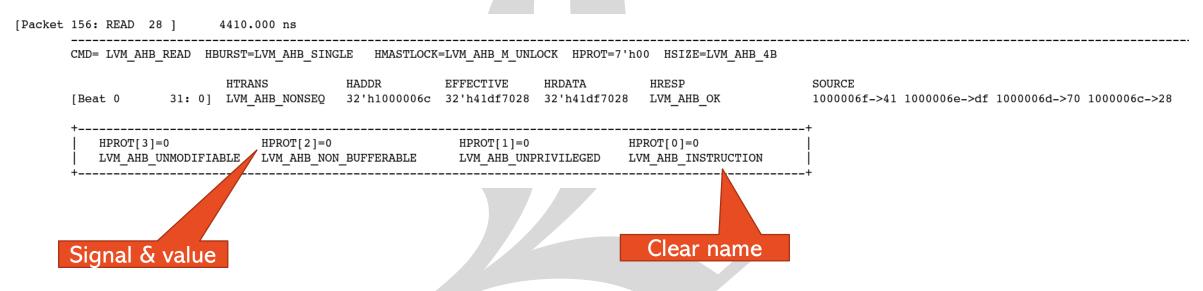

### COMPREHENSIVE TRACKER

- Full info for each packet in the AHB bus can be observed via tracker.

- Make the debug handy

```

[Packet 130: READ 2 ]

2890.000 ns

CMD= LVM_AHB_READ HBURST=LVM AHB INCR

HTRANS

HADDR

EFFECTIVE

HRDATA

HRESP

SOURCE

31: 0] LVM AHB NONSEQ

32'h10000010 32'habe064dd 32'habe064dd

[Beat 0

LVM AHB OK

10000013->ab 10000012->e0 10000011->64 10000010->dd

[Beat 1

31: 0] LVM AHB SEQ

32'h10000014 32'h25e5cb20 32'h25e5cb20

LVM AHB OK

10000017->25 10000016->e5 10000015->cb 10000014->20

LVM AHB OK

[Beat 2

31: 0] LVM AHB SEQ

32'h10000018 32'hbff73a51 32'hbff73a51

1000001b->bf 1000001a->f7 10000019->3a 10000018->51

HPROT[3]=0

HPROT[2]=1

HPROT[0]=1

HPROT[1]=1

LVM_AHB_DATA_ACCESS

LVM AHB UNMODIFIABLE LVM AHB BUFFERABLE

LVM AHB PRIVILEGED

[Packet 164: WRITE 136]

HMASTLOCK=LVM AHB M UNLOCK HPROT=7'h00 HSIZE=LVM_AHB_2B

CMD=LVM AHB WRITE HBURST=LVM AHB INCR

HADDR

HRESP

IMPACT

HTRANS

EFFECTIVE

HWDATA

[Beat 0

15: 0] LVM AHB NONSEQ

32'h10000040 16'hed73

32'hxxxxed73

LVM AHB OK

10000041<-ed 10000040<-73

[Beat 1

31:16] LVM AHB SEQ

LVM AHB OK

32'h10000042 16'h6c6a

32'h6c6axxxx

10000043<-6c 10000042<-6a

[Beat 2

15: 0] LVM AHB SEQ

32'h10000044 16'haeef

32'hxxxxaeef

LVM AHB OK

10000045<-ae 10000044<-ef

[Beat 3

31:16] LVM AHB SEQ

32'h10000046 16'h1bd

32'h01bdxxxx

LVM AHB OK

10000047<-01 10000046<-bd

HPROT[3]=0

HPROT[2]=0

HPROT[0]=0

LVM AHB UNMODIFIABLE LVM AHB NON BUFFERABLE

```

# END OF TEST MEMORY PRINTER END OF TEST SCOREBOARD PRINTER

• Print total read and total write, ensure test is not empty.

| AHB S | Scoreboard | Repor | t   |

|-------|------------|-------|-----|

|       | Reads      | :     | 129 |

|       | Writes     | :     | 129 |

|       | Checked    | :     | 129 |

# **TESTSUITE**

### THE BENEFITS FROM TESTSUITE

- Can verify various aspects, for example:

- Verify the data integrity, with full blast of randomized AHB packets

- Verify the response of every packet to meet expected value.

# PERFORMANCE ANALYZER

## PERFORMANCE ANALYZER

Performance

```

Performance Report

Chnl Total Total Average wait % Bus Performance thru waits wait / beat utilization

AHB 272 1350 4.963 17 WORST

```

# PARTIAL REGISTER ACCESS VERIFICATION

# PARTIAL REGISTER ACCESS VERIFICATION

- Can verify register partial access

- Full access is fully verified at uvm's bit bashing sequence

- LVM adds the coverage for partial accesses

## **BURST REGISTER ACCESS VERIFICATION**

# BURST REGISTER ACCESS VERIFICATION

- Can verify register burst access

- Single beat full access is fully verified at uvm's bit bashing sequence

- LVM adds the coverage for burst accesses

- This enable the bus read / write more than 1 registers in burst modes, where randomized burst size will be covered as well.

Example like below, where there are 4 burst packets (in 4 different colors) in 1B to program all the 6 x 32bits registers.

| Register O | BYTE 3 | BYTE 2 | BYTE 1 | BYTE O |

|------------|--------|--------|--------|--------|

| Register 1 | BYTE 3 | BYTE 2 | BYTE 1 | BYTE O |

| Register 2 | BYTE 3 | BYTE 2 | BYTE 1 | BYTE O |

| Register 3 | BYTE 3 | BYTE 2 | BYTE 1 | BYTE O |

| Register 4 | BYTE 3 | BYTE 2 | BYTE 1 | BYTE O |

| Register 5 | BYTE 3 | BYTE 2 | BYTE 1 | BYTE O |

## STRENGTH SUMMARY

- Robust

- Easy-to-control packet sending style: pipelined or gated styles.

- Fully parameterized UVC

- All the signal's width can be easily parameterized.

- Supports multiple instances with different parameters.

- User friendly

- Easy to use as driving, waiting and configuring are API-based.

- User need not deal with sequence for most of the time (user friendly for engineers new to UVM).

- Does not require in-depth UVM knowledge to use this UVC.

- Ease of configuration

- Component(s) can be turned off.

- Component(s) can be silenced.

- UVC can be configured via API.

- Examples of tests, scoreboard and sequence given as a handy reference for the users.

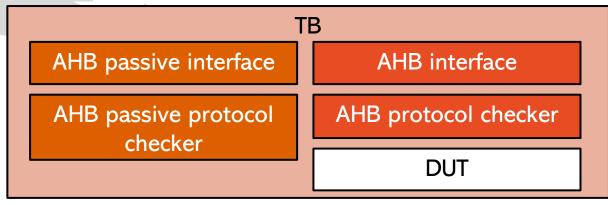

- Easy to configure the UVC in passive mode.

### STRENGTH SUMMARY

- Reusable

- Proven to be easily instantiable at module level testbench or SOC level testbench.

- Easy to reuse code that deals with the UVC.

- Ease of integration

- Minimum steps needed from integration to sending the first AHB packet.

- It is RAL ready.

- High debug-ability

- Tracker file: AHB transactions can be traced in the log file.

- Interface provides some debug signals.

- Strong checkers

- Equipped with industry standard protocol checks on the AHB bus.

- Equipped with memory verification scoreboard (background check read and write within address ranges)

- Reset aware feature

- The reset-aware UVC flushes the pending transactions if HRESETn goes active.

- Light weight

- Efficient use of variables for least memory space consumption over the simulation time.

- Setup and hold ready

- It can be configured to inject X outside setup and hold window.

### ENUM TYPE READY TO BE USED

```

// X injection or clocking block

typedef enum bit {

LVM_CLOCKING = 1'b0,

// Using old way of injecting the delay via clocking block

LVM_X_INJECTION = 1'b1

// Outside setup and hold time, X is injected

} LVM_SETUP_HOLD_em;

typedef enum bit {

LVM_MASTER = 1'b1,

LVM_SLAVE = 1'b0

} LVM_ROLE

```

```

// ON OFF

typedef enum bit {

= 1'b1, // ON

LVM ON

LVM OFF

= 1'b0 // OFF

} LVM ON OFF em;

// TRUE FALSE

typedef enum bit {

LVM TRUE

= 1'b1,

LVM FALSE

= 1'b0

} LVM TRUE FALSE em;

// RESET

typedef enum bit {

LVM RESET

= 1'b0,

LVM OUT OF RESET

= 1'b1

} LVM RESET em;

```

# ENUM TYPE READY TO BE USED

```

typedef enum logic [2:0] {

LVM_AHB_1B

= 0,

LVM AHB 2B

= 1,

= 2,

LVM AHB 4B

= 3,

LVM AHB 8B

LVM AHB 16B

=4,

LVM AHB 32B

= 5,

LVM AHB 64B

= 6,

LVM AHB 128B

= 7

} lvm ahb hsize em;

typedef enum logic {

LVM_AHB_READ

= 0,

LVM AHB WRITE

= 1

} lvm_ahb_op_em;

```

```

typedef enum bit {

LVM AHB OK

= 0,

LVM_AHB_HRESP_ERR

= 1

} lvm ahb hresp em;

typedef enum logic [2:0] {

LVM_AHB_SINGLE

= 0,

LVM AHB INCR

= 1,

LVM AHB WRAP4

= 2,

LVM AHB INCR4

= 3,

LVM_AHB_WRAP8

=4,

LVM AHB INCR8

= 5,

LVM AHB WRAP16

= 6,

LVM AHB INCR16

= 7

} lvm ahb hburst em;

```

# **UVC HIERARCHY PATHS**

- If user instantiates the LVM AHB UVC under test, the following paths will be valid:

- uvm\_test\_top.m\_ahb\_env

- uvm\_test\_top.m\_ahb\_env.agt

- uvm\_test\_top.m\_ahb\_env.agt.sqr

- uvm\_test\_top.m\_ahb\_env.agt.drv

- uvm\_test\_top.m\_ahb\_env.agt.mon

- uvm\_test\_top.m\_ahb\_env.cfg

- uvm\_test\_top.m\_ahb\_env.prd

- uvm\_test\_top.m\_ahb\_env.adp

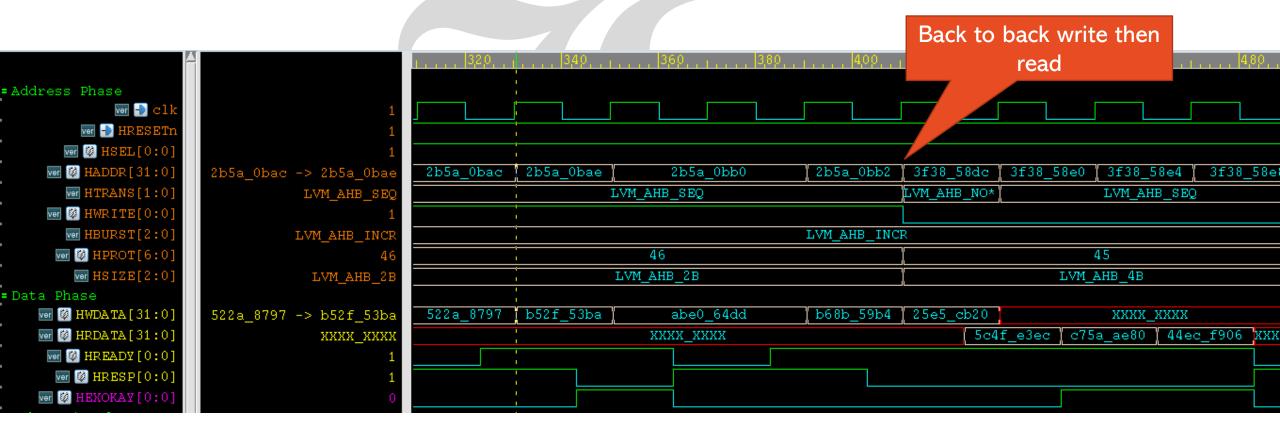

# AHB UVC COMPONENTS

- Driver (drv)

- Configurable sending style that can be changed on-the-fly:

- Ungated / Pipelined packets: Everything send in back-to-back.

- Gated packets: Wait for response, then proceed to send.

- Monitor (mon)

- Captures all AHB transactions and provides seq item port for user.

- Prints out tracker log file.

- Configuration (cfg)

- Contains all the configurable parameters and some APIs.

- Environment (env)

- Provider of all the user's API.

# AHB UVC COMPONENTS

- RAL adaptor (adp)

- Ready-to-use adaptor to convert user's RAL access commands into AHB transactions.

- RAL predictor (prd)

- Ready-to-use predictor to convert monitored AHB transactions into RAL update mechanism.

- Protocol Checkers (sva)

- Complete checker for protocol compliancy.

- SVA that flags error using "uvm\_error".

- Provides SVA coverage for user analysis.

#### CONFIGURABLE UVC

- LVM AHB UVC is designed to be fully configurable to meet the user's needs.

- All the configuration variables are located inside the config class.

- Most of the variables can be controlled by using API inside the env.

- Besides, this UVC is fully configurable using parameters for signal width.

- For details, please refer to "Step by Step Integration Guide".

# LVM POWERED API

| No | API name             | Example                                                                                                                                             |  |

|----|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1  | enter_reset          | <pre><env>.enter_reset; // This makes the UVC to enter reset state (auto done when HRESETn fall)</env></pre>                                        |  |

| 2  | exit_reset           | <pre><env>.exit_reset; // This makes the UVC to exit reset state (auto done when HRESETn rise)</env></pre>                                          |  |

| 3  | deactivate_UVC       | <pre><env>.deactivate_UVC; // Driver, monitor etc. stop their operation (called by enter_reset)</env></pre>                                         |  |

| 4  | activate_UVC         | <pre><env>.activate_UVC; // Driver, monitor etc. back to being operational (called by exit_reset)</env></pre>                                       |  |

| 5  | posedge_clk          | <pre><env>.posedge_clk; // Wait for next posedge of UVC clock // Clock info is shown in log file [m ahb cfg] clock period = 20.000 ns</env></pre>   |  |

| 6  | negedge_clk          | <pre><env>.negedge_clk; // Wait for next negedge of UVC clock  [m_ahb_cfg] window of 1 = 10.000 ns  [m_ahb_cfg] window of 0 = 10.000 ns</env></pre> |  |

| 7  | recompute_clk_period | <pre><env>. recompute_clk_period; // Restart the UVC clock frequency calculation</env></pre> [m_ahb_cfg] duty cycle = 50.0%                         |  |

# LVM POWERED API

| No | API name    | Example                                      |                            |

|----|-------------|----------------------------------------------|----------------------------|

| 1  | off_driver  | <env>.off_driver; // Turn OFF driver</env>   |                            |

| 2  | on_driver   | <env>.on_driver; // Turn ON driver</env>     | Useful when user           |

| 3  | off_monitor | <env>.off_monitor; // Turn OFF monitor</env> | makes this UVC as passive. |

| 4  | on_monitor  | <env>.on_monitor; // Turn ON monitor</env>   |                            |

| 5  | off_tracker | <env>.off_tracker; // Turn OFF tracker</env> |                            |

| 6  | on_tracker  | <env>.on_tracker; // Turn ON tracker</env>   |                            |

# **PROTOCOL**

• User can configure AHB5 properties for this UVC, using the following cmd:

```

ahb_env.cfg.AHB5_Extended_Memory_Types = LVM_TRUE;

ahb_env.cfg.AHB5_Secure_Transfers = LVM_TRUE;

ahb_env.cfg.AHB5_Exclusive_Transfers = LVM_TRUE;

ahb_env.cfg.AHB_User_Signals = LVM_TRUE;

```

- Default it is full AHB5 protocol.

- To enter AHB LITE protocol mode, these variable can be turned OFF.

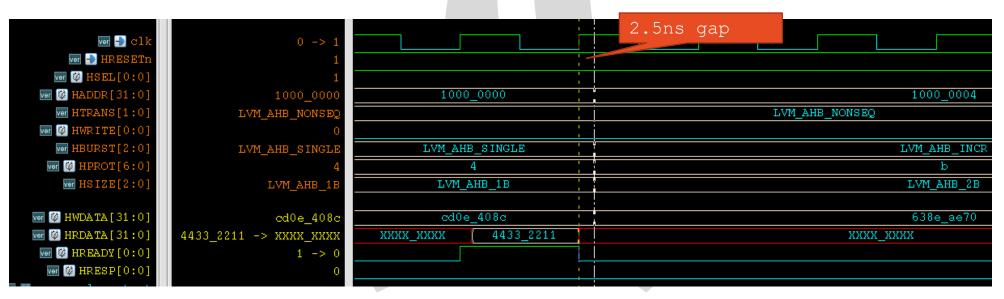

# **CLOCKING BLOCK CONFIGURATION**

- This UVC implements the standard clocking blocks.

- When configuring output (VIP → DUT) to be 2.5ns, the impact is as follows:

• The cmd:

```

m_ahb_env.set_hold_time (2500 ,"ps");

```

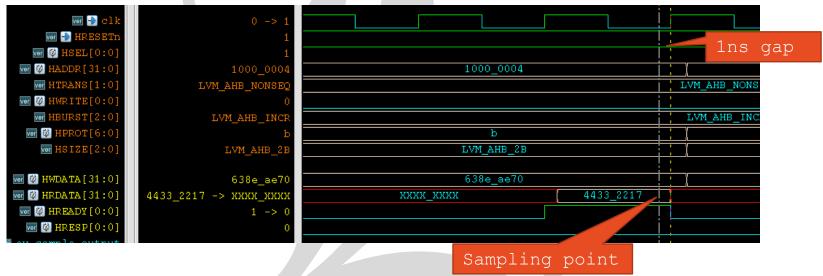

# **CLOCKING BLOCK CONFIGURATION**

• The default value chosen for input (DUT → VIP) is 1ns, the impact is as follows:

• This gap can be configured using the following cmd:

```

m_ahb_env.set_setup_time(1 ,"ns");

```

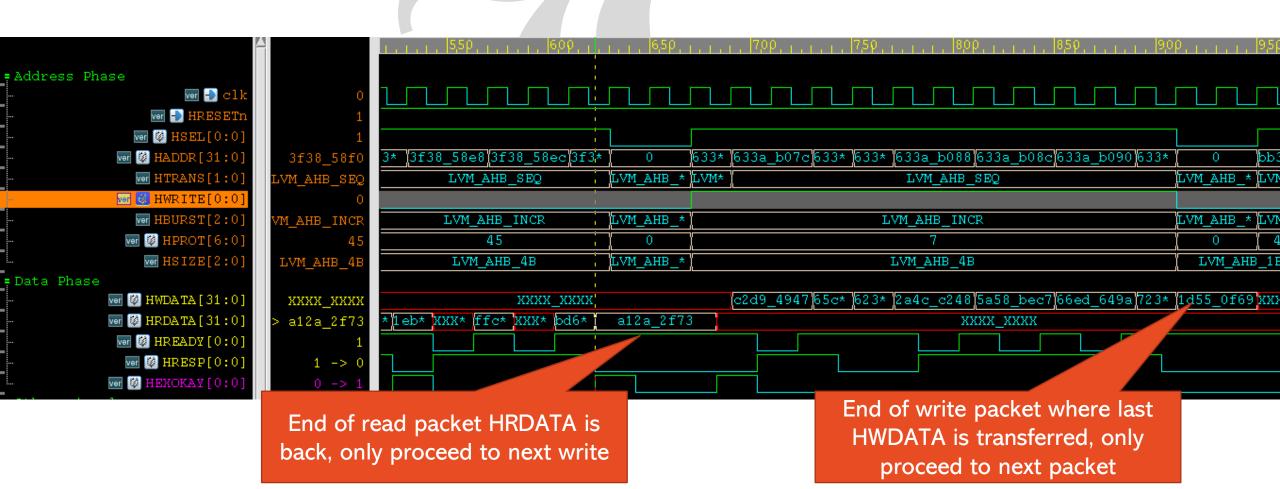

# DRIVER WAIT STYLE

- The driver can be configured by user to wait for the slave response after it has sent a packet. For example,

- After AHB read is sent, dry can be made to wait for all HRDATAs to come back with responses.

- After AHB write are sent, drv can be made to wait for all responses to come back.

| No | API name                 | Example                                                                                                                         |

|----|--------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 1  | drv_wait_output(LVM_ON)  | <pre><env>.drv_wait_output(LVM_ON); // Put driver to wait for response before sending next packet.</env></pre>                  |

| 2  | drv_wait_output(LVM_OFF) | <pre><env>.drv_wait_output(LVM_OFF);    // Put driver to continuously send stimulus regardless of the response from</env></pre> |

|    |                          | AHB slave.                                                                                                                      |

# PIPELINED TRANSACTION DRV\_WAIT\_OUTPUT(LVM\_OFF)

# WAIT FOR RESPONSE TRANSACTION DRV\_WAIT\_OUTPUT(LVM\_ON)

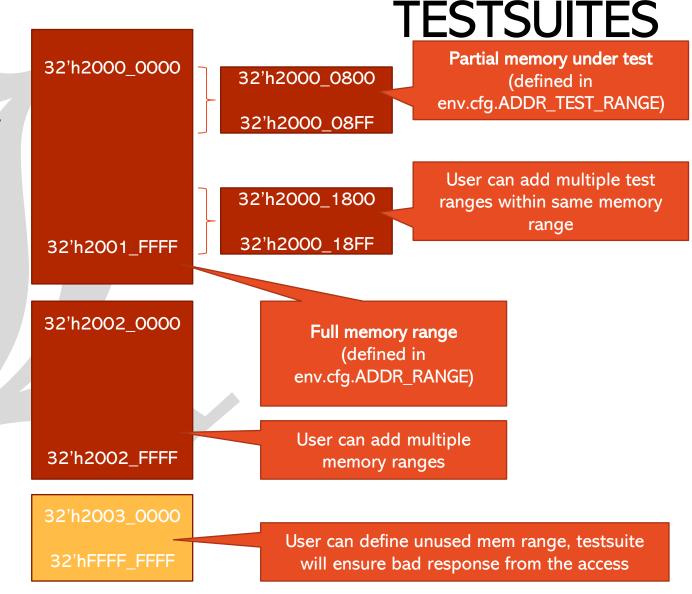

# CARE\_BOUNDARY

- This bit will define master UVC to follow the ADDR\_TEST\_RANGE (more details at "AHB testsuites" session), where the upper limit won't be crossed.

- Default is 1

- If user needs to send packet that cross the ADDR\_TEST\_RANGE upper limit, then can set this bit to O

```

m ahb env.cfg.care boundary = 1'b0; // default value is 1

```

# CHANCE\_OF\_BUSY & MAX\_BUSY

- chance\_of\_busy is percentage number that define the probability of master UVC to inject busy state during AHB packet sending.

- Default is O (will not inject busy)

- To enable the BUSY state

```

m_ahb_env.cfg.chance_of_busy = 10; // a value in percentage

```

- max\_busy define maximum clock number of master to be busy.

- Only effective when chance\_of\_busy != 0

- Default is 5 (5 clks max for busy state, randomized from 1-5)

```

m_ahb_env.cfg.max_busy = 5;

```

# CANCEL\_ON\_ERROR

- This int is probability of master UVC to cancel a stimulus during when it sees HRESP==ERROR

- Default is 0% (will not cancel)

- To enable the cancel mode

m ahb env.cfg.cancel on error = 50; // 50% chance to cancel

# LVM AHB SLAVE CONFIGURATION

- In the self test testbench, LVM slave UVC is connected to LVM master UVC.

- It is configurable to perform different kind of responses to master.

- The note for each variables are documented inside sim/makefile under "Plusargs" keyword

# LVM AHB SLAVE CONFIGURATION

- <slave\_env>.cfg.auto\_reply

- Default value = 1'b1

- Slave VIP will be returning HREADY, HRESP per ever\_ready, not\_ready\_clks, bad\_hresp, rand\_not\_ready, inject\_error.

- when <slave env>.cfg.auto\_reply == 1'b0, slave VIP will not be returning HREADY,

HRESP until user give value via API

<slave env>.drive\_HREADY(<user value: LVM\_AHB\_READY / LVM\_AHB\_NOT\_RDY>);

# HIGH DEBUG-ABILITY UVC

- To speed up the debug process, the UVC provides its user with high visibility of AHB bus traffic.

- The simulation with monitor = ON & tracker = ON will enable the tracker file dump

- It is a file that contains all the AHB transactions printed systematically.

- It is very useful for the user:

- A user who is new to this API can use this file to observe the effect of a testcode.

- For example, the use of "grep" for the keyword "READ" lets the user know how many reads are being done.

- During the debug process, it quickly pin-points the transaction that has problem, even before the user opens the waveform to check.

- User can easily know what is the write data that has taken effect in each beat (auto-generated by UVC after considering HSIZE, HADDR etc.).

- Same goes for the read data: the effective data makes it easy for the user to know the valid data value in each beat (auto-generated by UVC after considering HSIZE, HADDR etc.).

# TRACKER LOG

- LVM AHB provides high debugability by preparing log file for all AHB packets that goes through the bus and are captured by the monitor.

- This feature can be turned OFF: <env>.off\_tracker.

- File name: <testname>/<testname>\_<seed>.trk.log

- This path can be configured via <env>.cfg.LogFileName = <string>;

#### TRACKER LOG

• For read packet:

Packet serial number (++1for Read Read serial number (++1 for Read) ′ Write) **Details of Read** Timestamp [Packet 156: READ 28 ] 4410.000 ns CMD= LVM AHB READ HBURST=LVM AHB SINGLE HMASTLOCK=LVM\_AHB\_M\_UNLOCK HPROT=7'h00 HSIZE=LVM\_AHB\_4B Effective bits HTRANS HADDR EFFECTIVE HRDATA HRESP SOURCE 31: 0] LVM AHB NONSEQ [Beat 0 32'h1000006c 32'h41df7028\_ 32'h41df7028 LVM AHB OK 1000006f->41 1000006e->df 1000006d->70 1000006c->28 Effective data **Beat** HPROT[3]=0 HPROT[2]=0 HPROT[0]=0 HPROT[1]=0Source for this beat LVM AHB UNMODIFIABLE LVM AHB UNPRIVILEGED LVM AHB INSTRUCTION LVM AHB NON BUFFERABLE count

Effective address

#### TRACKER LOG

• For both read and write, the HPROT will be further presented in more readable form:

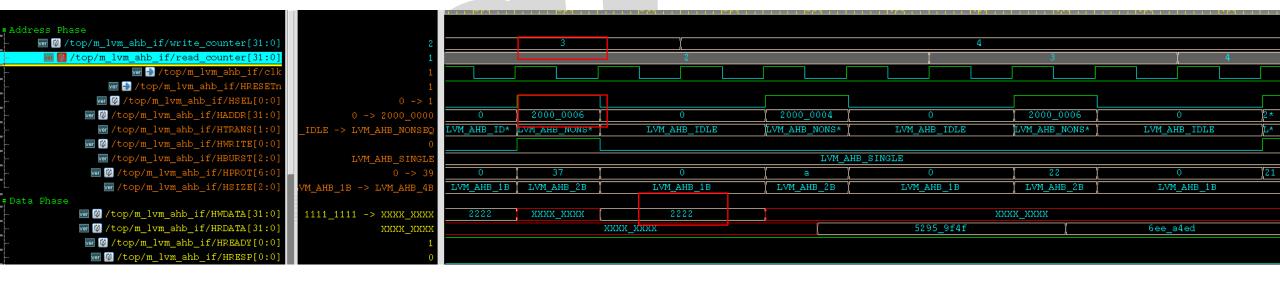

# READ AND WRITE COUNTER

- There are 2 signals to help user easily point to some specific AHB transactions in the waveform:

- read\_counter: Counts all the read packets.

- write\_counter: Counts all the write packets.

# WRITE COUNTER

[Packet 4 350.000 ns **EFFECTIVE** HWDATA/HRDATA HTRANS HADDR HEXOKAY IMPACT/SOURCE [Beat 0 31:16] LVM\_AHB\_NONSEQ 32'h20000006 16'h0 32'h00002222 LVM\_AHB\_HRESP\_OK LVM AHB HEX ERR 20000007<-00 20000006<-00

#### READ COUNTER

[Packet 6 READ 3 1 470.000 ns HAUSER=32'hf371d044 HWUSER=32'hca6bbad3 HRUSER=32'h3156dab7 CMD= LVM AHB READ HBURST=LVM AHB SINGLE HMASTLOCK=LVM\_AHB\_M\_UNLOCK HPROT=7'h22 HSIZE=LVM\_AHB\_2B HNONSEC=1'h0 **EFFECTIVE** HWDATA/HRDATA HTRANS HEXOKAY IMPACT/SOURCE [Beat 0 31:16] LVM\_AHB\_NONSEQ 32 h20000006 16'h6ee 32'h06eea4ed LVM AHB HEX ERR 20000007->06 20000006->ee

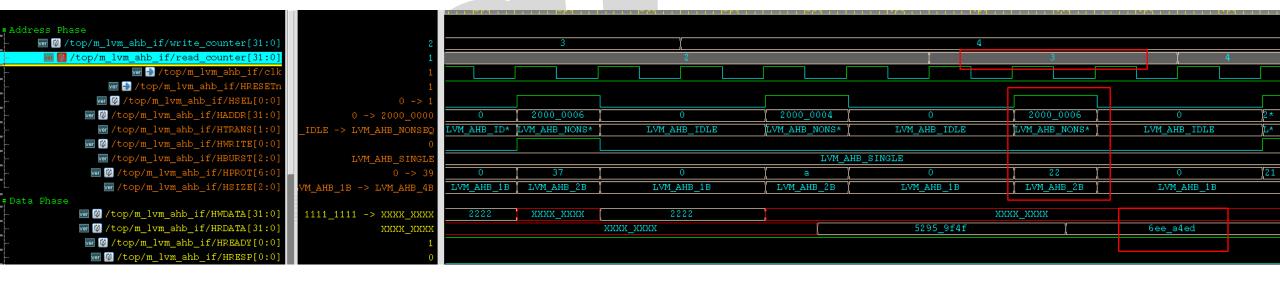

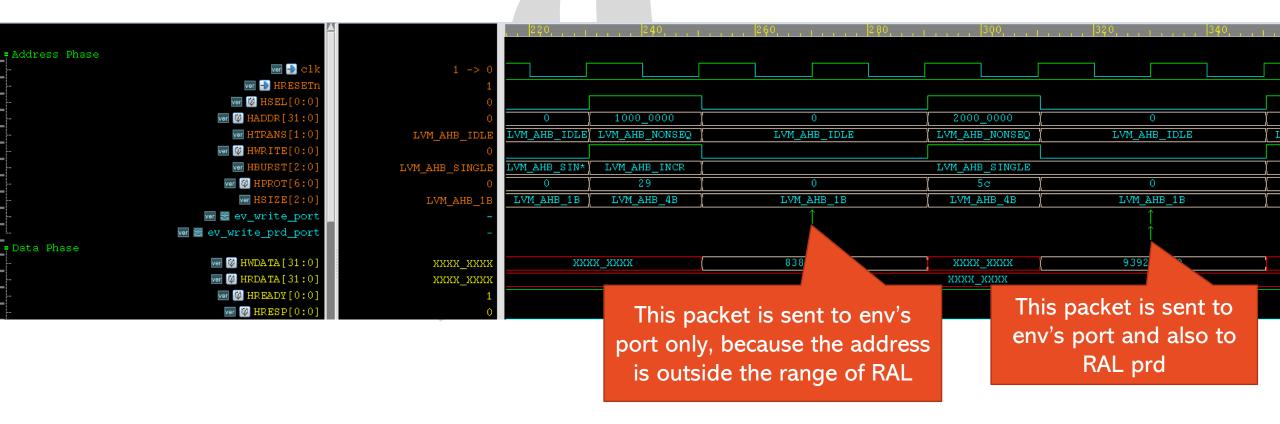

# PORT WRITE EVENTS

• For the user to easily identify the timing when the packet is written into env's port, the interface has the following events:

| No | Event name        | Purpose                                                              |

|----|-------------------|----------------------------------------------------------------------|

| 1  | ev_read_port      | Marks the time where AHB read packet is written into env's TLM port  |

| 2  | ev_read_prd_port  | Marks the time where AHB read packet is sent to RAL predictor        |

| 3  | ev_write_port     | Marks the time where AHB write packet is written into env's TLM port |

| 4  | ev_write_prd_port | Marks the time where AHB write packet is sent to RAL predictor       |

#### PORT WRITE EVENTS

Events for write packets

#### PORT WRITE EVENTS

Events for read packets

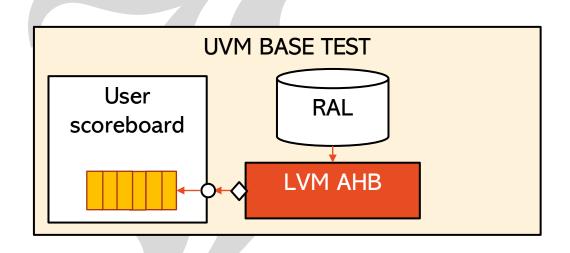

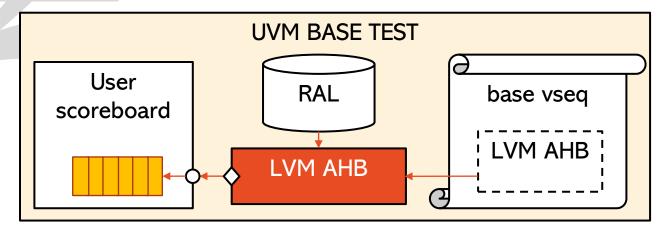

#### RAL READY AHB UVC

- The LVM's AHB is ready to work with RAL.

- It has built-in RAL adaptor and RAL predictor.

- To connect the AHB UVC with RAL, the following is to be done at connect phase:

```

// Passing in the urm

m_ahb_env.cfg.urm = urm;

if (m_ahb_env.cfg.has_prd)

m_ahb_env.prd.map = urm.default_map;

if (m_ahb_env.cfg.has_adp)

urm.default_map.set_sequencer(m_ahb_env.agt.sqr, m_ahb_env.adp);

```

Ref: tests/lvm\_ahb\_base\_test.sv

# RAL READ WRITE - DRV\_WAIT\_OUTPUT = ON

After the connection is done, user can use the RAL to perform the read/ write access:

```

<env>.drv_wait_output(LVM_ON);

urm.<regA>.read (status, mydata); // mydata will be loaded with correct read returned data

`uvm_info(msg_tag, $sformatf("HRESP=%h", m_ahb_env.cfg.ral_HRESP[0]), UVM_NONE) // retrieving HRESP

urm.<regB>.write(status, mydata);

`uvm_info(msg_tag, $sformatf("HRESP=%h", m_ahb_env.cfg.ral_HRESP[0]), UVM_NONE) // retrieving HRESP

// proceed only after write response is received

urm.<regB>.read (status, mydata);

// mydata is now the valid data after the write above to regB

```

Ref: tests/lvm\_ahb\_O1\_ral\_access\_test.sv

# RAL READ WRITE - DRV\_WAIT\_OUTPUT = OFF

If the user uses the drv\_wait\_output = LVM\_OFF, the effect is as below:

```

<env>.drv_wait_output(LVM_OFF);

urm.<regA>.read (status, mydata);

// mydata is X

urm.<regB>.write(status, mydata);

// Without waiting, this write is launched

urm.<regB>.read (status, mydata);

// At this point, mydata is X

// and this packet can happen earlier than the write packet above

```

• It is always recommended for the user to use <a href="mailto:drv\_wait\_output">drv\_wait\_output</a> == LVM\_ON during RAL access.

# RAL READY AHB UVC

- User can configure the UVC to send AHB packets with desired value for RAL generated packet.

- For example, when user enters the command urm.<regA>.read / write (...), the value of signals below can be easily controlled by calling the API below during runtime.

- Available variables to configure for RAL's access:

| No | Variable  | API command                                                 |                    |

|----|-----------|-------------------------------------------------------------|--------------------|

| 1  | HMASTLOCK | <pre><env>.cfg.ral_HMASTLOCK = <value>;</value></env></pre> |                    |

| 2  | HPROT     | <env>.cfg.ral_HPROT</env>                                   | = <value>;</value> |

| 3  | HNONSEC   | <env>.cfg.ral_HNONSEC</env>                                 | = <value>;</value> |

| 4  | HEXCL     | <env>.cfg.ral_HEXCL</env>                                   | = <value>;</value> |

| 5  | HMASTER   | <env>.cfg.ral_HMASTER</env>                                 | = <value>;</value> |

| 6  | HAUSER    | <env>.cfg.ral_HAUSER</env>                                  | = <value>;</value> |

| 7  | HWUSER    | <env>.cfg.ral_HWUSER</env>                                  | = <value>;</value> |

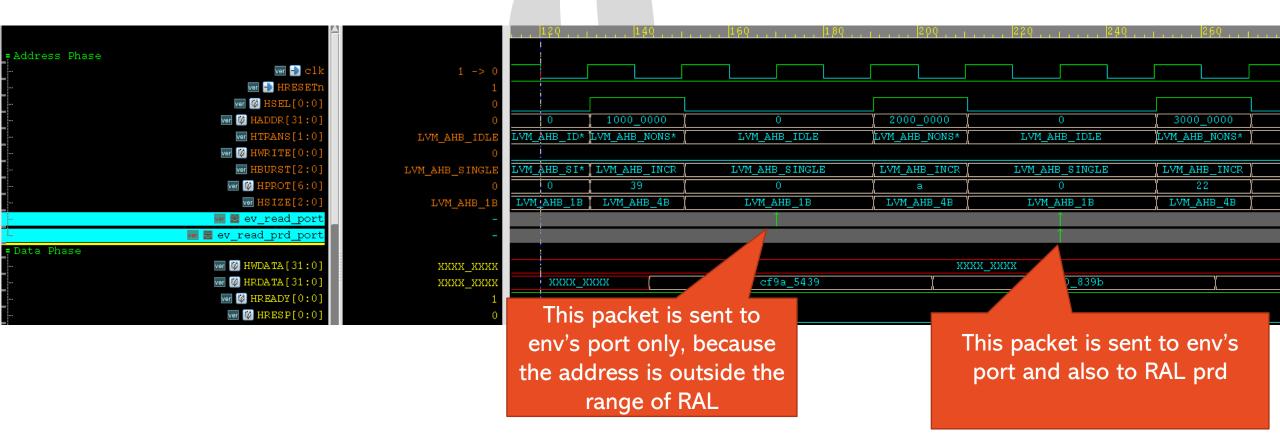

### RAL PREDICTION

• To increase the efficiency of the predictor operation, the predictor working range can be configured:

```

ral_max_addr : max address of the RAL

```

ral\_min\_addr : min address of the RAL

• The built-in RAL predictor works based on range specified by the user for these 2 variables:

```

urm.default_map.set_base_addr (32'h2000_0000);

m_ahb_env.cfg.add_RAL_ADDR_RANGE (

.start_addr (<ral_min_addr>),

.end_addr (<ral_max_addr>),

.expected_resp({LVM_AHB_OK}));

```

# ADP & PRD ON/OFF

- The adp or prd can be easily turned OFF by the user if not required.

- To turn OFF adaptor:

```

uvm_config_db#(bit)::set(this, "*m_ahb_env*", "has_adp", 1'b0);

```

To turn OFF predictor:

```

uvm_config_db#(bit)::set(this, "*m_ahb_env*", "has_prd", 1'b0);

```

Ref: tests/lvm\_ahb\_30\_no\_component\_test.sv

# ADDR AND DATA WIDTH CONFIGURATION

- User shall configure the UVM\_REG\_ADDR\_WIDTH and UVM\_REG\_DATA\_WIDTH properly matching the design.

- At compile cmd: (Ref: sim/makefile)

- +define+UVM\_REG\_DATA\_WIDTH=32 +define+UVM\_REG\_ADDR\_WIDTH=32

### FULL REG WRITE ACCESS

- This UVC supports full register write access as shown previously:

- urm.<regB>.write(status, mydata);

- It will do the hwrite.

- During write, HSIZE=4B for the case data width = 32

### FULL REG READ ACCESS

- This UVC support full register read access as shown previously:

- urm.<regA>.read (status, mydata);

- It will do the AHB read.

- It is always full access.

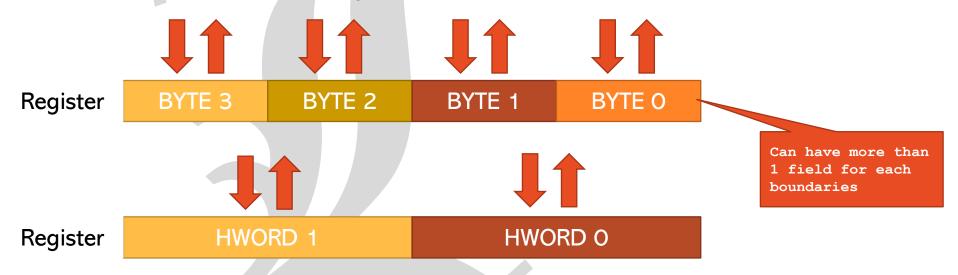

### PARTIAL REG WRITE ACCESS

- If user configures ral field that <u>align with byte boundary</u> as individual\_accessible = 1, then this UVC will send out AHB packet with corresponding HSIZE.

- For example, the field size below is 1 byte, aligned at byte lane 0:

```

B0 = uvm reg field::type id::create("B0");

B0.configure(

The size must be 8 bits

.parent

(this),

.size

(8),

.1sb pos

(0),

("RW"),

.access

.volatile

(0),

('0),

.reset

.has reset

(1),

.is rand

(1),

Must be individually accessible

.individually accessible (1)) +

```

### PARTIAL REG WRITE ACCESS

• When user does the reg.field.write (normally is reg.write), it will trigger the UVC to send out HWRITE with 1B as below:

urm.control 0.B0 .write (status, 32 'h99); ver 🜗 clk ver 🜗 HRESETn ver 🔯 HSEL[0:0] ver 🔯 HADDR [31:0] 0 -> 1000 0000 1000 005c 1000 0000 ver HTRANS[1:0] LVM AHB NONSEQ LVM AHB IDLE LVM AHB NONSEQ LVM AHB IDLE -> LVM\_AHB\_NONSEQ ver 🔯 HWRITE[0:0] ver HBURST[2:0] LVM\_AHB\_SINGLE LVM\_AHB\_SINGLE wer 🕼 HPROT[6:0] ver HSIZE[2:0] LVM AHB 4B LVM AHB 1B LVM\_AHB\_1B 🚾 🔯 HWDATA[31:0] 2222 -> XXXX XXXX 9999 0000 1111 2222 XXXX XXXX 2d5 bf71 ver 🔯 HRDATA[31:0] 2d5 bf71 ver 🔯 HREADY [0:0] wer 🔯 HRESP[0:0]

### PARTIAL REG WRITE ACCESS

- This means, user can easily access various byte boundary fields, for example:

- 8 bits, can be at byte 0, 1, 2 or 3 (provided fields are 8 bits wide and fill up whole byte)

- 16 bits, can be byte 1\_0, byte 2\_1, or byte 3\_2 (provided fields are 16 bits wide and fill up whole hword)

- However, if the fields are smaller than a byte, like case below, then this line cannot be used anymore to achieve byte access.

urm.<reg>.<field>.write (status,32'h99);

| 31:24 | 23:16 | 15:8 |    |    |    |    |

|-------|-------|------|----|----|----|----|

|       |       |      | f3 | f2 | f1 | fO |

To solve that problem, LVM adds the coverage for partial accesses

• It supports all IEEE field access types, while systematically verify the byte accesses, hword accesses of DUT.

- [BYTE verification] If there is/are fields that resides from bit 0 to 7, then it will do byte write to BYTE 0 with random data

- Then byte read to BYTE O to confirm the effect, considering the field access (RW, RO, W1C etc)

- Repeat above with various random data.

- Repeat for BYTE 1, 2, and 3

- If there are fields that reside from bit 0 to 15, then it will do hword write to HWORD 0 with random data

- Then hword read to HWORD 0 to confirm the effect, considering the field access (RW, RO, W1C etc)

- Repeat above with various random data.

- Repeat for HWORD 1

• To enable this, user just need to do so at the testcase:

```

// Example of skipping a field

urm.control_0_0C.B0.set_compare(UVM_NO_CHECK);

m_ahb_env.ral_partial_access.map = urm.default_map; // connect to your desired map to verify

m_ahb_env.ral_partial_access.start(null);

```

| [lvm_ral_partial]< Verifying HWORD 0 access >         |                             |        |       |         |          |          |

|-------------------------------------------------------|-----------------------------|--------|-------|---------|----------|----------|

| [lvm_ral_partial]                                     |                             |        |       |         |          |          |

| [lvm_ral_partial] LVM_HWORD 0 ADDR VECTO              | R FIELD_PATH                | ACCESS | RESET | DESIRED | MIRRORED | VOLATILE |

| [lvm_ral_partial] LVM_HWORD 0 32'h10000080 [ 0:       | 0] urm.control_80.b0        | RW     | 1'h0  | 1'h1    | 1'h1     | 0        |

| [lvm_ral_partial] LVM_HWORD 0 32'h10000080 [ 1:       | 1] urm.control_80.b1        | RW     | 1'h0  | 1'h1    | 1'h1     | 0        |

| [lvm_ral_partial] LVM_HWORD 0 32'h10000080 [ 2:       | 2] urm.control_80.b2        | RW     | 1'h0  | 1'h0    | 1'h0     | 0        |

| [lvm_ral_partial] LVM_HWORD 0 32'h10000080 [ 3:       | 3] urm.control_80.b3        | RW     | 1'h0  | 1'h0    | 1'h0     | 0        |

| [lvm_ral_partial] LVM_HWORD 0 32'h10000080 [15:       | 4] urm.control_80.b15_4     | RW     | 12'h0 | 12'hc1a | 12'hc1a  | 0        |

| [lvm_ral_partial]                                     |                             |        |       |         |          |          |

| [lvm_ral_partial] HWORD write addr='h10000080         |                             |        |       |         |          |          |

| [lvm_ral_partial] Correct! HWORD Read addr='h10000080 |                             |        |       |         |          |          |

| [lvm_ral_partial] Correct! FULL Read addr='h10000080  |                             |        |       |         |          |          |

| [lvm_ral_partial] HWORD write addr='h10000080         |                             |        |       |         |          |          |

| [lvm_ral_partial] Correct! HWORD Read addr='h10000080 |                             |        |       |         |          |          |

| [lvm_ral_partial] Correct! FULL Read addr='h10000080  | -                           |        |       |         |          |          |

| [lvm_ral_partial] HWORD write addr='h10000080         |                             |        |       |         |          |          |

| [lvm_ral_partial] Correct! HWORD Read addr='h10000080 | -                           |        |       |         |          |          |

| [lvm_ral_partial] Correct! FULL Read addr='h10000080  | -                           |        |       |         |          |          |

| [lvm_ral_partial] HWORD write addr='h10000080         |                             |        |       |         |          |          |

| [lvm_ral_partial] Correct! HWORD Read addr='h10000080 | -                           |        |       |         |          |          |

| [lvm_ral_partial] Correct! FULL Read addr='h10000080  | data='hc4c2be0e as expected |        |       |         |          |          |

|                                                       |                             |        |       |         |          |          |

| [lvm_ral_partial] Verifyi       | ng BYTE 3 access >      |                             |        |       |         |          |          |

|---------------------------------|-------------------------|-----------------------------|--------|-------|---------|----------|----------|

| [lvm_ral_partial]               |                         |                             |        |       |         |          |          |

| [lvm_ral_partial] LVM_BYTE      | 3 ADDR VECTOR           | R FIELD_PATH                | ACCESS | RESET | DESIRED | MIRRORED | VOLATILE |

| [lvm_ral_partial] LVM_BYTE      | 3 32'h10000080 [28:28   | 3] urm.control_80.b28       | RW     | 1'h0  | 1'h0    | 1'h0     | 0        |

| [lvm_ral_partial] LVM_BYTE      | 3 32'h10000080 [29:29   | e] urm.control_80.b29       | RW     | 1'h0  | 1'h0    | 1'h0     | 0        |

| '                               | 3 32'h10000080 [30:30   | · _                         | RW     | 1'h0  | 1'h0    | 1'h0     | 0        |

| [lvm_ral_partial] LVM_BYTE      | 3 32'h10000080 [31:31   | l] urm.control_80.b31       | RW     | 1'h0  | 1'h0    | 1'h0     | 0        |

| [lvm_ral_partial]               |                         |                             |        |       |         |          |          |

| [lvm_ral_partial] BYTE          |                         |                             |        |       |         |          |          |

| [lvm_ral_partial] Correct! BYTE |                         |                             |        |       |         |          |          |

| [lvm_ral_partial] Correct! FULI | _ Read addr='h10000080  | data='h44c2c1a3 as expected |        |       |         |          |          |

| [lvm_ral_partial]               |                         |                             |        |       |         |          |          |

| · ,                             | E write addr='h10000083 |                             |        |       |         |          |          |

| [lvm_ral_partial] Correct! BYTE |                         |                             |        |       |         |          |          |

| [lvm_ral_partial] Correct! FULI | . Read addr='h1000008(  | data='hf4c2c1a3 as expected |        |       |         |          |          |

| [lvm_ral_partial]               |                         |                             |        |       |         |          |          |

| · ·                             | E write addr='h10000083 |                             |        |       |         |          |          |

| [lvm_ral_partial] Correct! BYTE |                         |                             |        |       |         |          |          |

| [lvm_ral_partial] Correct! FULI | Read addr='h10000080    | data='hb4c2c1a3 as expected |        |       |         |          |          |

| [lvm_ral_partial]               |                         |                             |        |       |         |          |          |

| [lvm_ral_partial] BYTE          |                         |                             |        |       |         |          |          |

| [lvm_ral_partial] Correct! BYTE |                         | -                           |        |       |         |          |          |

| [lvm_ral_partial] Correct! FULI | Read addr='h10000080    | data='hc4c2c1a3 as expected |        |       |         |          |          |

| [lvm_ral_partial]               |                         |                             |        |       |         |          |          |

|                                 |                         |                             |        |       |         |          |          |

- Apart from partial register access, LVM add register burst access verification.

- Single beat full access is fully verified at uvm's bit bashing sequence

- Example: [LEFT] 4 burst write packets (in 4 different colors) in 1B to program all the 6 x 32bits registers.

- [RIGHT] Then 3 burst read packet in 1B to read all registers and check the data to match expected values.

| Register O | BYTE 3 | BYTE 2 | BYTE 1 | BYTE O |

|------------|--------|--------|--------|--------|

| Register 1 | BYTE 3 | BYTE 2 | BYTE 1 | BYTE O |

| Register 2 | BYTE 3 | BYTE 2 | BYTE 1 | BYTE O |

| Register 3 | BYTE 3 | BYTE 2 | BYTE 1 | BYTE O |

| Register 4 | BYTE 3 | BYTE 2 | BYTE 1 | BYTE O |

| Register 5 | BYTE 3 | BYTE 2 | BYTE 1 | BYTE O |

| Register O | BYTE 3 | BYTE 2 | BYTE 1 | BYTE O |

|------------|--------|--------|--------|--------|

| Register 1 | BYTE 3 | BYTE 2 | BYTE 1 | BYTE O |

| Register 2 | BYTE 3 | BYTE 2 | BYTE 1 | BYTE O |

| Register 3 | BYTE 3 | BYTE 2 | BYTE 1 | BYTE O |

| Register 4 | BYTE 3 | BYTE 2 | BYTE 1 | BYTE O |

| Register 5 | BYTE 3 | BYTE 2 | BYTE 1 | BYTE O |

- Example: [LEFT] there are 3 burst packets (in 3 different colors) in 2B to program all the 6 x 32bits registers.

- [RIGHT] Then 3 burst read packet in 2B to read all registers and check the data to match expected values.

| Register 0 | HWORD 1 | HWORD 0 |

|------------|---------|---------|

| Register 1 | HWORD 1 | HWORD 0 |

| Register 2 | HWORD 1 | HWORD 0 |

| Register 3 | HWORD 1 | HWORD 0 |

| Register 4 | HWORD 1 | HWORD 0 |

| Register 5 | HWORD 1 | HWORD 0 |

| Register O | HWORD 1 | HWORD 0 |

|------------|---------|---------|

| Register 1 | HWORD 1 | HWORD 0 |

| Register 2 | HWORD 1 | HWORD 0 |

| Register 3 | HWORD 1 | HWORD 0 |

| Register 4 | HWORD 1 | HWORD 0 |

| Register 5 | HWORD 1 | HWORD 0 |

- Example: [LEFT] there are 3 burst packets (in 3 different colors) in 4B to program all the 6 x 32bits registers.

- [RIGHT] Then 3 burst read packet in 4B to read all registers and check the data to match expected values.

| Register 0 | WORD |

|------------|------|

| Register 1 | WORD |

| Register 2 | WORD |

| Register 3 | WORD |

| Register 4 | WORD |

| Register 5 | WORD |

| Register O | WORD |

|------------|------|

| Register 1 | WORD |

| Register 2 | WORD |

| Register 3 | WORD |

| Register 4 | WORD |

| Register 5 | WORD |

To enable this, user just need to do so at the testcase:

```

// Example of skipping a field

urm.control 0 0C.B0.set compare(UVM NO CHECK);

urm.control 0 0C.B1.set compare(UVM NO CHECK);

// Sequence configuration

m ahb env.ral burst access.support partial = 1;

// 1 means support 1B, 2B accesses (smaller than bus size access)

m ahb env.ral burst access.max beats num

// this is the max number of beats that the sequence will launch.

= 16;

// connect the map to be verified

m ahb env.ral burst access.map

= urm.default map; // connect to your desired map to verify

// User may let it randomized, or fix to certain desired size

m ahb env.ral burst access.bytes per beat = 'z;

// Randomize bytes per beat, user can put 1/2/4/8

m ahb env.ral burst access.start(null);

```

| [lvm_ral_burst] | WRITE | Beat=0 | addr=' | h10000060 | size=LVM HWORD | data='h31aa |

|-----------------|-------|--------|--------|-----------|----------------|-------------|

| [lvm ral burst] | WRITE | Beat=1 | addr=' | h10000062 | size=LVM HWORD | data='h170d |

| [lvm ral burst] | WRITE | Beat=2 | addr=' | h10000064 | size=LVM HWORD | data='hadb5 |

| [lvm ral burst] | WRITE | Beat=3 | addr=' | h10000066 | size=LVM HWORD | data='h7dc1 |

| [lvm ral burst] |       |        |        |           | _              |             |

| [lvm ral burst] | WRITE | Beat=0 | addr=' | h10000068 | size=LVM HWORD | data='hccf4 |

| [lvm_ral_burst] | WRITE | Beat=1 | addr=' | h1000006a | size=LVM_HWORD | data='h465f |

| [lvm_ral_burst] |       |        |        |           |                |             |

| [lvm_ral_burst] | WRITE | Beat=0 | addr=' | h1000006c | size=LVM_HWORD | data='h7e70 |

| [lvm_ral_burst] | WRITE | Beat=1 | addr=' | h1000006e | size=LVM_HWORD | data='hff7f |

| [lvm_ral_burst] |       |        |        |           |                |             |

| [lvm_ral_burst] | WRITE | Beat=0 | addr=' | h10000080 | size=LVM_HWORD | data='hac55 |

| [lvm_ral_burst] |       |        |        |           |                |             |

| [lvm_ral_burst] | WRITE | Beat=0 | addr=' | h10000082 | size=LVM_HWORD | data='hea04 |

| [lvm_ral_burst] |       |        |        |           |                |             |

| [lvm_ral_burst] | READ  | Beat=0 | addr=' | h10000000 | size=LVM_HWORD | data=7024   |

| [lvm_ral_burst] | READ  | Beat=1 | addr=' | h10000002 | size=LVM_HWORD | data=b3fa   |

| [lvm_ral_burst] | READ  | Beat=2 | addr=' | h10000004 | size=LVM_HWORD | data=4401   |

| [lvm_ral_burst] | READ  | Beat=3 | addr=' | h10000006 | size=LVM_HWORD | data=a3eb   |

| [lvm_ral_burst] | READ  | Beat=4 | addr=' | h10000008 | size=LVM_HWORD | data=2b82   |

| [lvm_ral_burst] | READ  | Beat=5 | addr=' | h1000000a | size=LVM_HWORD | data=e5c2   |

| [lvm_ral_burst] | READ  | Beat=6 | addr=' | h1000000c | size=LVM_HWORD | data=8797   |

| [lvm_ral_burst] | READ  | Beat=7 | addr=' | h1000000e | size=LVM_HWORD | data=454    |

| [lvm_ral_burst] | READ  | Beat=8 | addr=' | h10000010 | size=LVM_HWORD | data=ef73   |

| [lvm_ral_burst] | READ  | Beat=9 | addr=' | h10000012 | size=LVM_HWORD | data=53e1   |

| [lvm ral burst] |       |        |        |           |                |             |

Example of multiple burst writes in HWORD size and covering 1 and more registers

Example of 1 burst read in HWORD size and covering more registers

## BURST AHB PACKET TO RAL TARGET

# BACKGROUND AHB READ DATA CHECK

- For all the writes with address fall within user specific range, this UVC will capture the impact of the write data, considering all write packet parameters, like HADDR, HSIZE etc.

- For example, user set UVC to be as such:

```

m_ahb_env.cfg.got_mem = 1'b1; // this bit turn on the background data check mechanism

m_ahb_env.cfg.add_ADDR_RANGE(.start_addr(32'h1000_0000), .end_addr(32'h1000_1000));

// memory start & end addresses (support >1 entry)

```

- This means all the AHB write with address range falls between 32'h1000\_0000 and 32'h1000 1000 will cause UVC to update embedded memory.

- The data will be the expected data when the read happens for the address within the range.

- UVC will check each data when user set got\_mem == 1, and uvm\_error will be flagged if data is mismatched.

# BACKGROUND AHB READ DATA CHECK

• If user has initial value for the memory, then can update the UVC scoreboard (backdoor) first using the following API:

```

for(bit [31:0] addr=32'h1000_0000 ; addr<=32'h1000_0FFF ; addr+=4)

m_ahb_env.cfg.mem.store_4_data(addr,32'h0000_0000); // Addr and Data

```

- Then the write impact and read check will be working based on these initialized values.

- Note:

- store\_8\_data (8 bytes), store\_2\_data (2 bytes) and store\_1\_data (1 byte) can be used as well

# FRONTDOOR MEMORY INITIALIZATION

- To verify AHB memory, user commonly will initialize the memory with random value, via frontdoor write.

- The API below will initialize the memory within the range with AHB writes (multiple single beat AHB write)

m\_ahb\_env.frontdoor\_init\_mem;

### END OF TEST MEMORY PRINTING

At the end of test, the UVC can be programmed to print the full content of the memory when

```

m_ahb_env.cfg.got_mem = 1'b1;

```

It is based on the writes that happen throughout the test.

|                            |                  |                | RACKER                                       |                |          |          |          |          |       |          |          |          |          |   |                      |                      |                      |                      |   |                      |                      |                      |                      |                |

|----------------------------|------------------|----------------|----------------------------------------------|----------------|----------|----------|----------|----------|-------|----------|----------|----------|----------|---|----------------------|----------------------|----------------------|----------------------|---|----------------------|----------------------|----------------------|----------------------|----------------|

| <br> <br> -                | NO               | İ              | ADDR                                         | İ              | f        | е        | d        | С        | İ     | b        | а        | 9        | 8        | Ì | 7                    | 6                    | 5                    | 4                    | İ | 3                    | 2                    | 1                    | 0                    | -+<br> <br> -+ |

| <br>                       | 1<br>2<br>3<br>4 | <br>           | 00000000<br>00000010<br>01000000<br>01000010 | <br>           | 9B<br>D6 | 8C<br>45 | 80<br>19 | 06<br>8A | 1 1 1 | A8<br>43 | D5<br>DE | A6<br>DA | 56<br>B1 |   | 49<br>E6<br>E1<br>46 | 87<br>60<br>1C<br>63 | 96<br>44<br>14<br>9E | 6B<br>49<br>80<br>5B |   | 72<br>1B<br>50<br>6E | 8D<br>50<br>A9<br>4E | B6<br>47<br>6E<br>BF | 39<br>1E<br>69<br>37 | <br>           |

| <br> <br> <br> <br> <br> - | 5<br>6<br>7      | <br> <br> <br> | 02000000<br>02000010<br>03000000<br>03000010 | <br> <br> <br> | 01       | 53       | BE       | CD       | 1     | A2       | В0       | 2A       | 80       | 1 | B6<br>29             | 7E<br>06<br>AB       | 83<br>89<br>B7       | 4B                   | 1 | 58<br>4C             | 0B<br>AF<br>7D       | E9<br>28<br>9C       | B4<br>82             | <br> <br>      |

This feature can be turned OFF by

```

m_ahb_env.cfg.end_of_test_mem_print = 1'b0;

```

### END OF TEST MEMORY PRINTING

• Based on user preference, the size per line can be configured:

m\_ahb\_env.cfg.mem\_print\_size = 128; // support 32,64,128

• Example below on left is 64b version, right is 32b version

| MEM | MEMORY TRACKER |    |    |    |            |    |           |    |           |    |  |  |  |  |

|-----|----------------|----|----|----|------------|----|-----------|----|-----------|----|--|--|--|--|

| ++  |                |    |    |    |            |    |           |    |           |    |  |  |  |  |

| Ι   | NO   ADDR      | 7  | 6  | 5  | 4          | 3  | 2         | 1  | 0         | 1  |  |  |  |  |

| ++  |                |    |    |    |            |    |           |    |           |    |  |  |  |  |

| Ι   | 1   00000000   | 49 | 87 | 96 | 6B         | 72 | 8D        | В6 | 39        | 1  |  |  |  |  |

| 1   | 2   00000008   | 9B | 8C | 80 | 06         | A8 | D5        | Α6 | 56        | 1  |  |  |  |  |

| 1   | 3   00000010   | E6 | 60 | 44 | 49         | 1B | 50        | 47 | 1E        | 1  |  |  |  |  |

| Ι   | 4   01000000   | E1 | 1C | 14 | 80         | 50 | Α9        | 6E | 69        | 1  |  |  |  |  |

| ++  |                |    |    |    |            |    |           |    |           |    |  |  |  |  |

| Ι   | 5   01000008   | D6 | 45 | 19 | <b>8</b> A | 43 | DE        | DA | <b>B1</b> | 1  |  |  |  |  |

| Ι   | 6   01000010   | 46 | 63 | 9E | 5B         | 6E | 4E        | BF | 37        | 1  |  |  |  |  |

| Ι   | 7   02000000   | B6 | 7E | 83 | 4B         | 58 | 0B        | E9 | B4        | 1  |  |  |  |  |

| Ι   | 8   02000008   | 01 | 53 | BE | CD         | A2 | B0        | 2A | 80        | -  |  |  |  |  |

| +   | +              | -+ |    |    |            | -+ |           |    |           | -+ |  |  |  |  |

| Ι   | 9   02000010   | 29 | 06 | 89 | B4         | 4C | AF        | 28 | 82        | 1  |  |  |  |  |

| Ι   | 10   03000000  | E4 | AB | В7 | 03         | F6 | 7D        | 9C | 9C        | 1  |  |  |  |  |

| 1   | 11   03000008  | 83 | 5D | C4 | 5C         | 9D | <b>A8</b> | СВ | 2E        | 1  |  |  |  |  |

| Ι   | 12   03000010  | 9F | 04 | 45 | 4C         | 87 | B7        | E4 | 84        | 1  |  |  |  |  |

| +   | +              | -+ |    |    |            | -+ |           |    |           | -+ |  |  |  |  |

| MEMORY | TRACKER  |    |    |    |           |                  |

|--------|----------|----|----|----|-----------|------------------|

| NO     | ADDR     | 3  | 2  | 1  | 0         | - <del>-</del> - |

| 1      | 00000000 | 72 | 8D | В6 | 39        | i                |

| 2      | 00000004 | 49 | 87 | 96 | 6B        | ĺ                |

| 3      | 8000000  | A8 | D5 | Α6 | 56        | 1                |

| 4      | 0000000C | 9B | 8C | 80 | 06        | 1                |

| +      | -+       | +  |    |    |           | -+               |

| 5      | 00000010 | 1B | 50 | 47 | 1E        | -                |

| 6      | 00000014 | E6 | 60 | 44 | 49        | - 1              |

| 7      | 01000000 | 50 | Α9 | 6E | 69        | - 1              |

| 8      | 01000004 | E1 | 1C | 14 | 80        | -                |

| +      | -+       | +  |    |    |           | -+               |

| 9      | 01000008 | 43 | DE | DA | <b>B1</b> | -                |

| 10     | 0100000C | D6 | 45 | 19 | 8A        | ١                |

| 11     | 01000010 | 6E | 4E | BF | 37        | 1                |

| 12     | 01000014 | 46 | 63 | 9E | 5B        | 1                |

| +      | -+       | +  |    |    |           | -+               |

| 13     | 02000000 | 58 | 0B | E9 | B4        | -                |

| 14     | 02000004 | B6 | 7E | 83 | 4B        | - 1              |

| 15     | 02000008 | A2 | B0 | 2A | 80        | -1               |

| 16     | 0200000C | 01 | 53 | BE | CD        | - 1              |

| +      | -+       | +  |    |    |           | -+               |

### BACKDOOR MEM DATA RETRIEVAL

• User can retrieve the current stored data from memory database using the following API as well.

```

bit [31:0] my_spy_data;

my_spy_data = m_ahb_env.cfg.mem.get_4_data(32'h1000) ; // data from 1003,1002,1001,1000 addresses

my_spy_data = m_ahb_env.cfg.mem.get_2_data(32'h1000) ; // data from 1001,1000 addresses

my_spy_data = m_ahb_env.cfg.mem.get_1_data(32'h1000) ; // data from 1000 addresses

```

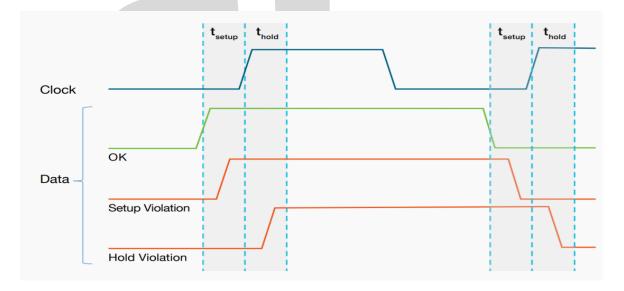

### **BACKGROUND**

- Setup time:

- signals must be stable for tsetup before the rising clock edge sampling.

- Hold time:

- signals must be stable for thold after the rising clock edge sampling.

Ref:

https://download.tek.com/document/55W\_61095\_O\_Identifying\_Setup-and-Hold\_AN\_03.pdf

### X INJECTION

- LVM AHB UVC has been programmed to be able to verify the setup and hold violations using X injection.

- This is most straight forward method.

ver 😐 HADDR

Windows outside setup and hold will be injected with X.

• If X propagates into the DUT, it implies that the DUT side does not meet the tsetup and thold

values.

| 🛭 🗱 clk                                                                      | 0 -> 1           | <u> </u>       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |        |  |

|------------------------------------------------------------------------------|------------------|----------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|--|

| [31:0]                                                                       | 2000_0001        | XXXX_XX*       | 2000_0000 | XXXX_XXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2000_0000 | хххх_х |  |

| [31:0]                                                                       | 0                | XXXX_Y         |           | XXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0         | жжж_х  |  |

| T[2:0]                                                                       |                  | 4 .            | 3         | <b>t</b> hold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3         | Х      |  |

| L[0:0]                                                                       |                  | <b>t</b> setup |           | A THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE STATE OF THE |           |        |  |

| [0:0]                                                                        | 0                |                |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |        |  |

| R[3:0]                                                                       | 0                | X              | 0         | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0         | X      |  |

| K[0:0]                                                                       | 0                |                |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |        |  |

| 0[0:0]                                                                       | 0                |                |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |        |  |