### LVM RAL PREDICTOR

Version 1.03 (July 2025)

### **Overview**

#### **Overview**

**About LVM RAL Predictor**

Before AND After of RAL Predictor

Benefits from the Log

Steps to Integrate LVM RAL Predictor

**Example LVM RAL Predictor INSTALLATION**

**Terms and Conditions**

**About LVM Verification Enterprise**

### **About LVM RAL Predictor**

#### WHAT IS RAL PREDICTOR FROM LVM

- Enhanced version of UVM RAL predictor

- Coded to be robust, and loaded with easy debug-ability and user-friendly features

- It is free!

#### **OBJECTIVES OF LVM RAL PREDICTOR**

- To help user see the effect of bus transaction towards RAL in best detail

- To help user to migrate from hard-coded RAL programming to UVM register model write and read style

- To ease the firmware coding with info like address and data

### **Before AND After of RAL Predictor**

# **BEFORE** UVM RAL Predictor original print

#### Read

[LVM\_PRED\_RD] Observed READ transaction to register urm.control\_0\_00: value='h5cd4b34b

#### **Write**

[LVM\_PRED\_WR] Observed WRITE transaction to register urm.control\_8: value='h2c252101 : updated value = 'h2c252101

### **Before AND After of RAL Predictor**

### **AFTER**

#### **LVM RAL Predictor**

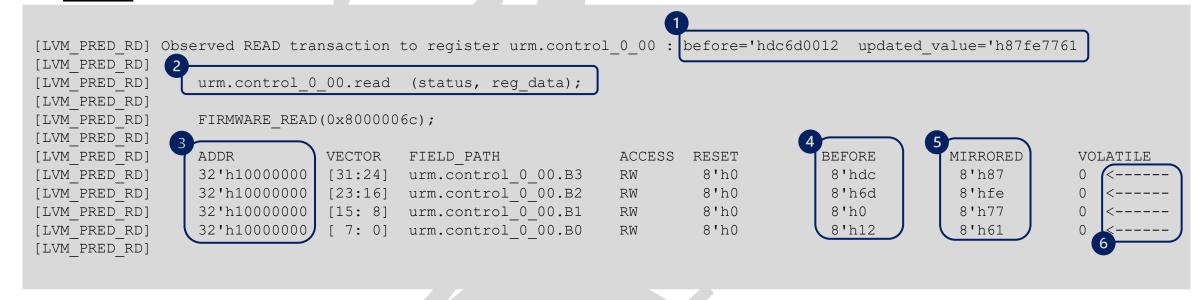

#### Read

- before != updated\_value if the read transaction is not launched from register model

- 2 Ready to be used code

- 3 Address for the register

- 4 Original mirrored value before the transaction

- **5** New Mirrored Value after the transaction

- 6 Arrow to highlight fields that get changed in this transaction

### **Before AND After of RAL Predictor**

### **AFTER** LVM RAL Predictor

#### **Write**

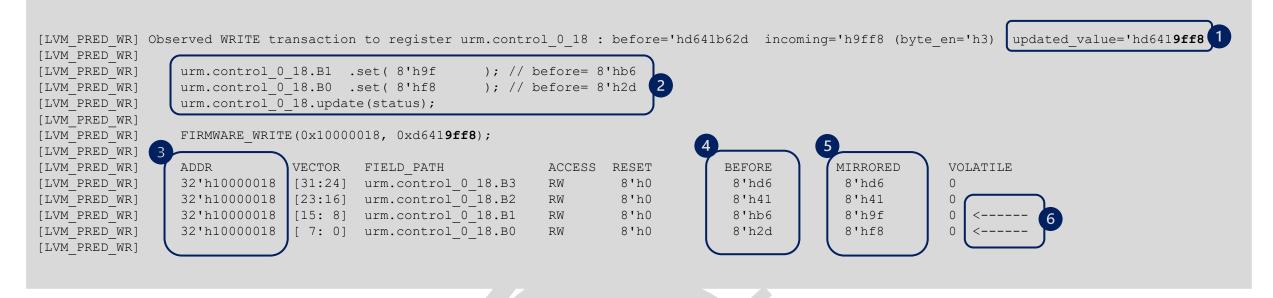

- 1 Final updated value

- 2 Ready to use code for register model access

- 3 Address for the register

- 4 Original value before the transaction

- 5 New Mirrored Value after the transaction

- 6 Arrow to highlight fields that get changed in this transaction

#### 1. Quick grep of field writing history

This grep cmd can quickly let you know the last written field value over time

```

grep urm.control 4.B3 2 <your log file> | grep '<----'</pre>

UVM INFO @ 3070.000 ns: uvm test top.m ahb env.prd

[LVM PRED WR]

32'h1000005c [31:16] urm.control 4.B3 2

16'h0

16'h0

16'hd2d0

UVM INFO @ 31690.000 ns: uvm test top.m ahb env.prd

[LVM PRED WR]

32'h1000005c [31:16] urm.control 4.B3 2

16'h0

16'hd2d0

16'h5555

UVM INFO @ 32330.000 ns: uvm test top.m ahb env.prd

[LVM PRED WR]

32'h1000005c [31:16] urm.control 4.B3 2

16'h0

16'h5555

16'h1111

UVM INFO @ 33710.000 ns: uvm test top.m ahb env.prd

32'h1000005c [31:16]

urm.control 4.B3 2

16'h0

16'h1111

16'h5555

[LVM PRED WR]

UVM INFO @ 37290.000 ns: uvm test top.m ahb env.prd

[LVM PRED WR]

32'h1000005c [31:16]

urm.control 4.B3 2

16'h0

16'h5555

16'h8888

UVM INFO @ 109590.000 ns: uvm test top.m ahb env.prd [LVM PRED WR]

32'h1000005c [31:16]

urm.control 4.B3 2

16'h0

16'h8888

16'h4444

UVM INFO @ 109950.000 ns: uvm test top.m ahb env.prd [LVM PRED WR]

32'h1000005c [31:16] urm.control 4.B3 2

16'h0

16'h4444

16'h6666

```

#### 2. Upgrade your code to register model style:

By referring to each PREDICTOR activity, the code here can be directly used:

```

[LVM_PRED_WR]

[LVM_PRED_RD]

[L

```

### **Benefits from the Log**

#### 3. Look out for code that is applicable for C for firmware:

By referring to each "FIRMWARE\_READ" or "FIRMWARE\_WRITE" code can be modified and used:

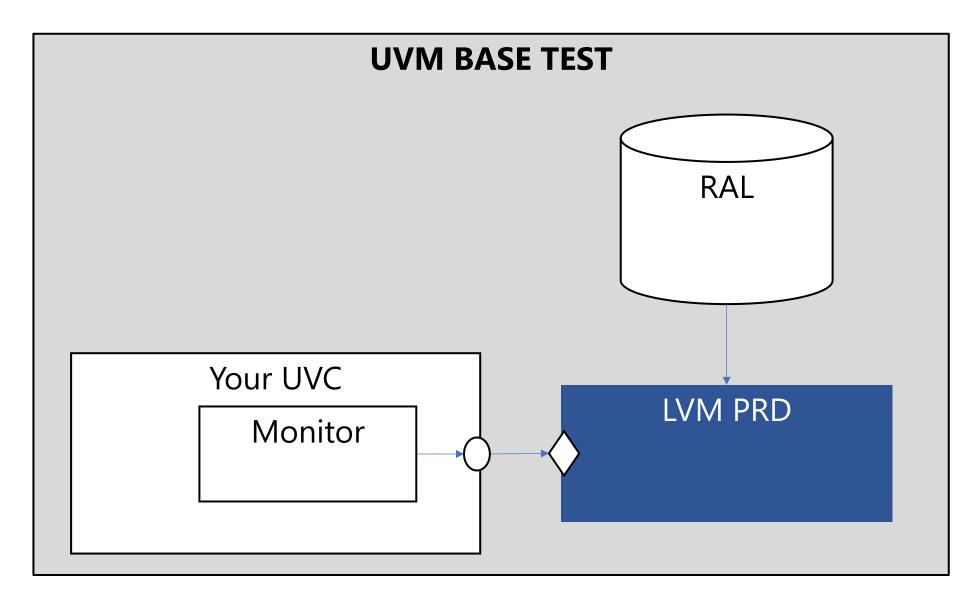

### **Steps to Integrate LVM RAL Predictor**

Scenario 1: If you are already using LVM VIPs, no action is needed.

#### Scenario 2: Else if you already instantiating the uvm\_reg\_predictor in your UVC

Step 1: Look for class that instantiate the uvm\_reg\_predictor, change it to lvm\_prd

Step 2: Look for package that include the class at step above and add lvm\_prd.svp into your uvc package in the step above, for example:

```

package <your package>;

...

include "lvm_prd.svp"

include "<your class that instantiate uvm_reg_predictor>"

...

endpackage

```

## **Steps to Integrate LVM RAL Predictor**

# Scenario 3: Else if you have register model in your TB, have ral adaptor but not using predictor yet

Step 1: Look for package that include the class at step before.

Step 2: Add lvm\_prd.svp into your uvc package in the step above, for example:

```

package <your package>;

...

`include "lvm_prd.svp"

`include "<your class that instantiate uvm_reg_adaptor>"

...

endpackage

```

## **Steps to Integrate LVM RAL Predictor**

# Scenario 3: Else if you have register model in your TB, have ral adaptor but not using predictor yet

Step 3: Look for a class that suitable to instantiate the predictor lvm\_prd, add the following codes at respective UVM phases

Pls use the seq item type matching your monitor

```

typedef lvm prd#(<your seq item class>)

<Your PRD type name>;

<Your PRD type name>

// UVC reg predictor

prd;

virtual function void build phase (uvm phase phase);

super.build phase (phase);

prd = <Your PRD type name>::type id::create("prd", this);

endfunction

virtual function void connect phase (uvm phase phase);

super.connect phase(phase);

prd.adapter = <your ral adaptor>;

= <your ral>.default map;

prd.map

<your UVC monitor port>.connect(prd.bus in);

endfunction

Monitor with seq item type matching your lvm_prd's seq item type

```

# **LVM RAL Predictor Verbosity Control**

User may configure the verbosity of the print out, where

# Controlled by `LVM\_PRD\_SUMMARY\_VERBOSITY

```

Observed READ transaction to register urm.control 0 00 : before='hdc6d0012 updated value='h87fe7761

[LVM PRED RD]

[LVM PRED RD]

[LVM PRED RD]

urm.control 0 00.read (status, reg data);

[LVM PRED RD]

FIRMWARE READ(0x8000006c);

[LVM PRED RD]

[LVM PRED RD]

[LVM PRED RD]

ACCESS

VECTOR

FIELD PATH

ADDR

RESET

BEFORE

MIRRORED

VOLATILE

8'h87

32'h10000000

[31:24]

urm.control 0 00.B3

8'h0

8'hdc

[LVM PRED RD]

RW

[LVM PRED RD]

32'h10000000

[23:16]

urm.control 0 00.B2

8'h0

8'h6d

8'hfe

RW

urm.control 0 00.B1

[LVM PRED RD]

[15: 8]

8'h0

8'h0

8 h77

32'h10000000

RW

[LVM PRED RD]

32'h10000000

[ 7: 0]

urm.control 0 00.B0

8'h0

8'h12

8'h61

RW

[LVM PRED RD]

```

Controlled by `LVM\_PRD\_DETAIL\_VERBOSITY

+define+LVM\_PRD\_SUMMARY\_VERBOSITY=UVM\_HIGH +define+LVM\_PRD\_DETAIL\_VERBOSITY=UVM\_HIGH

# **LVM RAL Predictor Verbosity Control**

Meanwhile, the RAL code and FIRMWARE code can be turned OFF totally as well

Can be turned OFF by +define+LVM\_PRD\_RAL\_CODE=0

| .VM_PRED_RD]<br>.VM_PRED_RD]              | urm.control_0_00.read (status, reg_data); |         |                     |        |                                            |                |                |          |  |

|-------------------------------------------|-------------------------------------------|---------|---------------------|--------|--------------------------------------------|----------------|----------------|----------|--|

| VM_PRED_RD]<br>VM_PRED_RD]<br>VM_PRED_RD] | FIRMWARE_READ(0x8000006c);                |         |                     | Ca     | Can be turned OFF by +define+LVM_PRD_FIRMW |                |                |          |  |

| VM PRED RD]                               | ADDR                                      | VECTOR  | FIELD PATH          | ACCESS | RESET                                      | BEFORE         | MIRRORED       | VOLATILE |  |

| VM PRED RD]                               | 32 <b>'</b> h10000000                     | [31:24] | urm.control 0 00.B3 | RW     | 8 <b>'</b> h0                              | 8'hdc          | 8 <b>'</b> h87 | 0 <      |  |

| /M PRED RD]                               | 32 <b>'</b> h10000000                     | [23:16] | urm.control 0 00.B2 | RW     | 8 <b>'</b> h0                              | 8'h6d          | 8'hfe          | 0 <      |  |

| /M PRED RD]                               | 32 <b>'</b> h10000000                     | [15: 8] | urm.control 0 00.B1 | RW     | 8 <b>'</b> h0                              | 8 <b>'</b> h0  | 8 <b>'</b> h77 | 0 <      |  |

| JM PRED RD]                               | 32 <b>'</b> h10000000                     | [ 7: 0] | urm.control 0 00.B0 | RW     | 8 <b>'</b> h0                              | 8 <b>'</b> h12 | 8 <b>'</b> h61 | 0 <      |  |

# **Example LVM RAL Predictor INSTALLATION**

### **Terms and Conditions**

#### **IMPORTANT NOTICE**

LVM reserves the right to make changes without further notice to any product or specifications herein.

LVM does not assume any responsibility for use of any its products for any particular purpose, nor does LVM assume any liability arising out of the application or use of any its products.

# **M** About LVM VIP

1. At LVM, our mission is to enhance the performance and efficiency of design verification work in the industry by providing ultra-high-quality, low-cost VIPs. We offer a range of AMBA VIPs and serial VIPs, including:

AXI4 / AXI4-LITE, AHB, APB, TCM, USART, JTAG, AXI Stream

- 2. To learn more about our services, please contact us at <a href="mailto:developer@lvmvip.com">developer@lvmvip.com</a>.

- 3. You can also visit our LinkedIn page at <a href="https://www.linkedin.com/in/lvm-vip-3444b21b5/">https://www.linkedin.com/in/lvm-vip-3444b21b5/</a>