## Sawblade Cyber Defense EDA

## **Cyber Security Cyber Defense**

Scott Winning – President / CEO

Sawblade Ventures, LLC

Austin, Texas

January 25, 2019

Sawblade Ventures, LLC

© 2015 Sawblade Ventures, LLC. All Rights Reserved

### **Sawblade Ventures Product Statement**

## **Sawblade Ventures Product:**

A fully functional patented method for improving cyber-security by integrating small flexible, re-configurable, distributed and networked hardware into microelectronic systems!

## **Sawblade Ventures History**

- Sawblade Ventures (SbV) began in January 2015.

- Sawblade Ventures, LLC is the managing partner of SaW Ventures, LP

- SbV is based on roadmap previously implemented by DAFCA, Inc

- Validation and Verification

DAFCA focus

- Cyber-Security

- DAFCA

- Began in 2003; Inactive in 2012

- SbV manages the technology including all rights, patents, IP, hardware and software previously owned by DAFCA.

- 10 years of research with over \$25M of investments in the IP

## **SbV Product Offering**

- SbV is offering a <u>HARDWARE</u> solution for securing integrated circuits.

- SbV can be used to augment other solutions including hardware and software techniques to improve security.

- SbV goes into the DNA of the chip, deep into the design.

- The best security is ..... <u>MORE</u> security!

## **SbV Product Offering**

## SbV includes:

- Patented methods for placing and configuring security

- Custom Digital IP library ClearBlue™ ReDi

- EDA tool used during design integration ClearBlue™

- Tutorial for use in building a secure chip with Sawblade

## **SbV Offering – The Basics**

### SbV Basics for System on Chip

#### Normal Design Flow

- Market need drives a product definition- any market

- Customer defines requirements, vendor develops spec

- Security definition can <u>not</u> be an afterthought

- SoC is designed using HDL/RTL/Verilog, chip is verified/Verilog

- Semiconductor process compiles into gates/transistors.

- DFT scan chains are added

- Timing, power, physical design is completed.

• <u>ALL WORKS per requirements and spec in this normal flow! Now,</u> Adding security

- Sawblade security is integrated and verified / only creator knows the secrets.

- Chip is re-verified for original functionality, timing, power *and security*.

- Tape out or FPGA programed and into production.

### 🗦 Sawblade Ventures, LLC

## **Application System Layers**

| Functional System Device |                                 |                |          |                                           |

|--------------------------|---------------------------------|----------------|----------|-------------------------------------------|

|                          | Network Communication           |                |          |                                           |

|                          | Encryption                      | Security API's | Security | Get to the<br>bottom of<br>the<br>problem |

|                          | Access Control & Authentication |                |          |                                           |

|                          | User Interface                  |                |          |                                           |

|                          | Device / Application API's      |                |          |                                           |

|                          | Operating System                |                |          |                                           |

|                          | Sensor / Instrument             |                |          |                                           |

|                          | Storage / Data                  |                |          |                                           |

|                          | Firmware                        |                |          |                                           |

|                          | SbV ->>> Chipset                |                |          |                                           |

|                          | SbV ->>> Base hardware modules  |                |          |                                           |

|                          | Eanth/Sama                      |                |          |                                           |

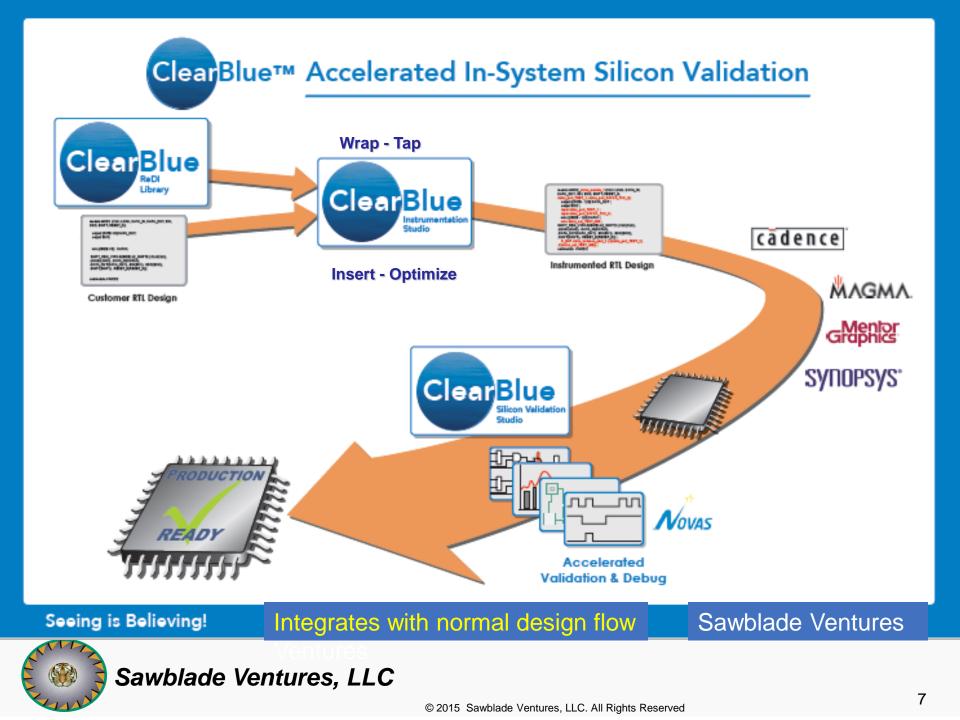

## **SbV ClearBlue™ Workflow**

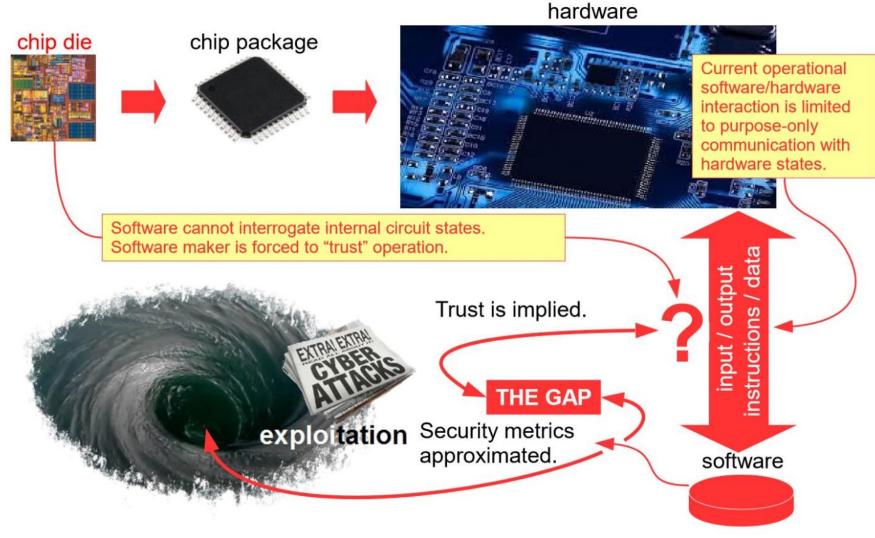

#### Electronic Systems Need Better Hardware Protection

### Sawblade Ventures, LLC

SbV predicate:

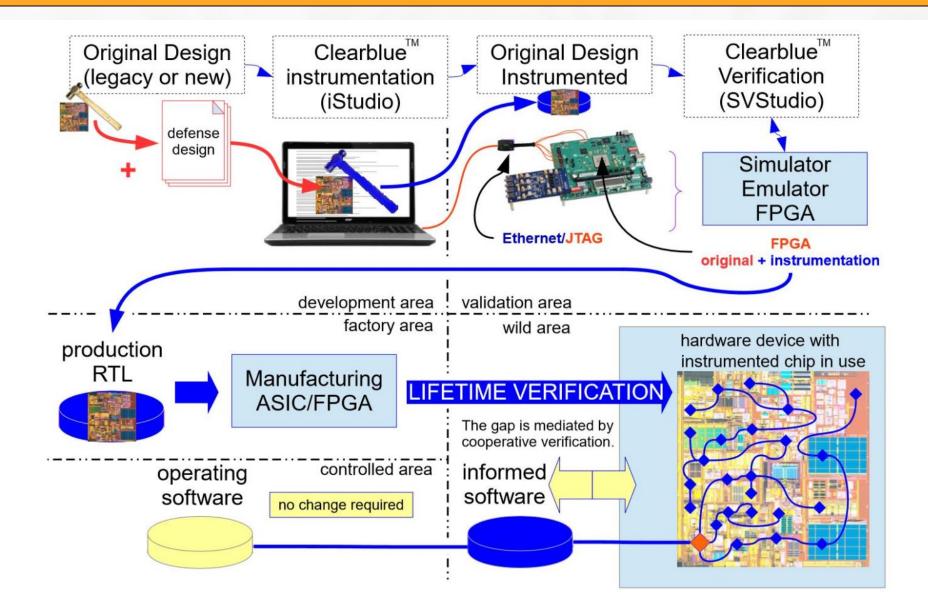

## **SbV How it Should work**

### New Design IC's – Adding Security

- Requirements are defined

- Assuming security is a critical need

- Architecture is defined / Specification written

- Security specification is a separate document

- Design is created, RTL, hardblocks, memories

- Design is verified through traditional methods

- Gates synthesized and verified.

- SbV security now can be added per specification

- RTL netlist is read into ClearBlue™ iStudio (EDA tool)

- IP blocks: Monitors, capture, trace, trigger engines inserted as per security strategy and spec.

- SVStudio is used to verify security scheme

- New netlist is created.

- Re-verification of base circuit, synthesis, timing, power, DFT

- Tape out

#### Sawblade Ventures, LLC

## **SbV How it Could work**

### New Design IC's – Design is in process.....

<u>OMG</u> – I have a weakness and we are about to tape out !!!

- **<u>STOP</u>** the tape out and prepare to **run Sawblade's ClearBlue™** !!!

- Define weakness plus some more thought of .... What else....

- Document the entry weakness

- SbV security is added per specification

- ➢ RTL netlist is read into ClearBlue™ EDA tool

- Monitors, capture, trace, trigger engines added

- SVStudio is used to verify security scheme

- New net list is created.

- Re-verification of base circuit, synthesis, timing, power, DFT

- Tape out with

- <u>MINIMAL TIME LOST</u>

- Gap Closed

#### Sawblade Ventures, LLC

## **SbV How it Could work**

### Modifying Existing Designed IC's

- At risk design features are identified

- Security specification is defined and documented

- SbV security is added per specification

- ➢ RTL netlist is read into ClearBlue™ EDA tool

- Monitors, capture, trace, trigger engines added

- SVStudio is used to verify security scheme

- New net list is created.

- Reverification of base circuit, synthesis, timing, power, DFT

- Tape out

Note: This can be done with same pin out / same package / same performance as before but now with *internal monitor and counter measures* added.

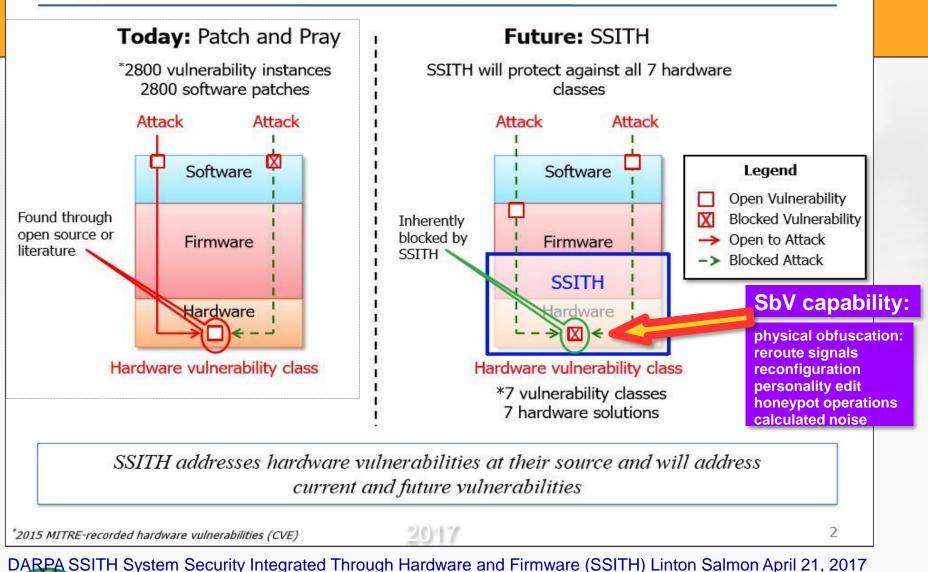

# **IT Industry Security Problem**

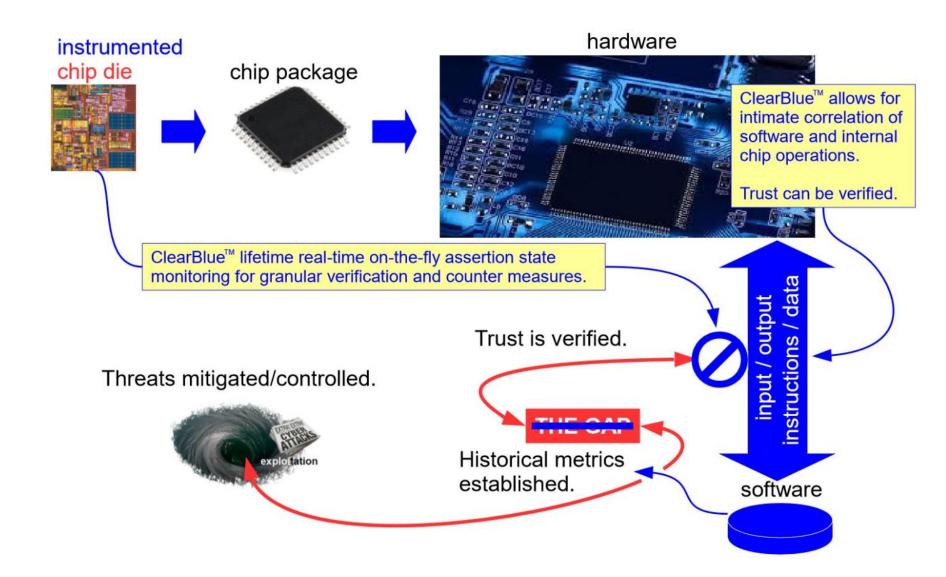

## **SbV ClearBlue™** Solution

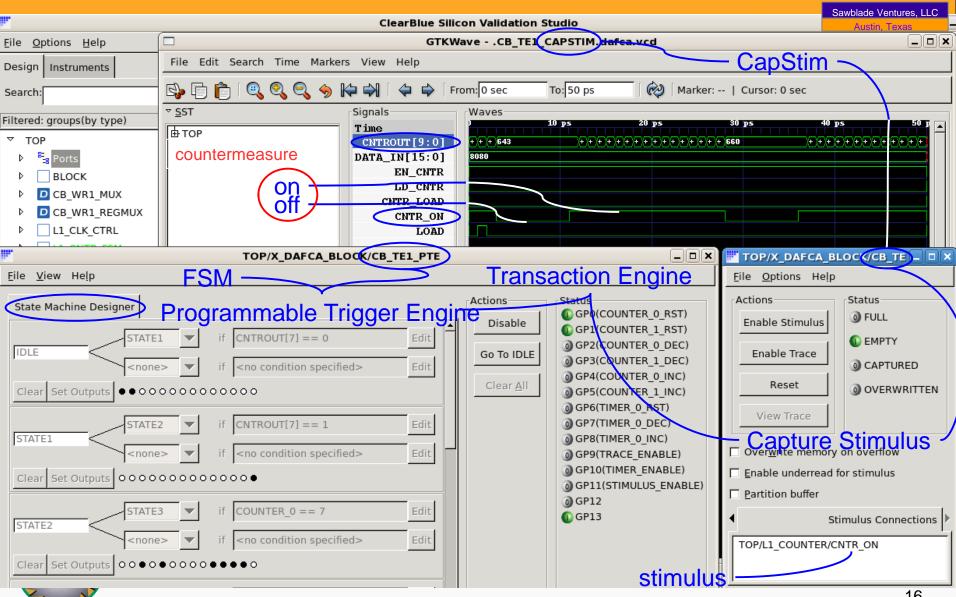

# Example SVStudio Run

MI

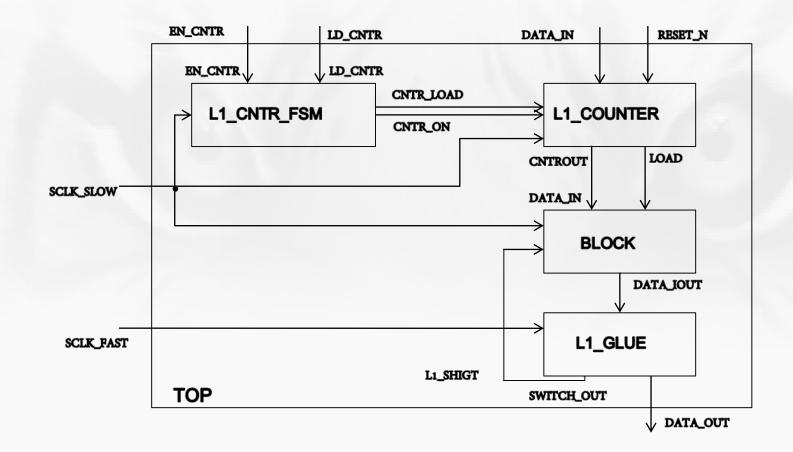

## **A Typical Circuit**

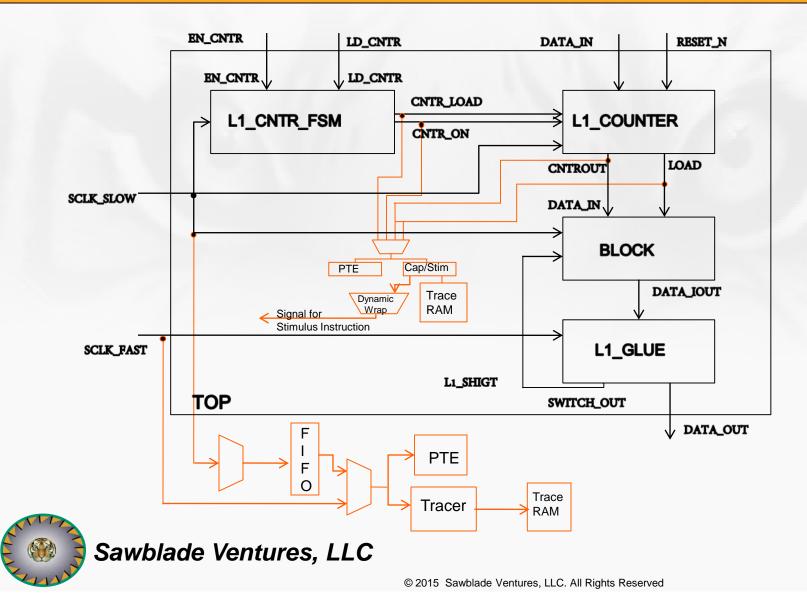

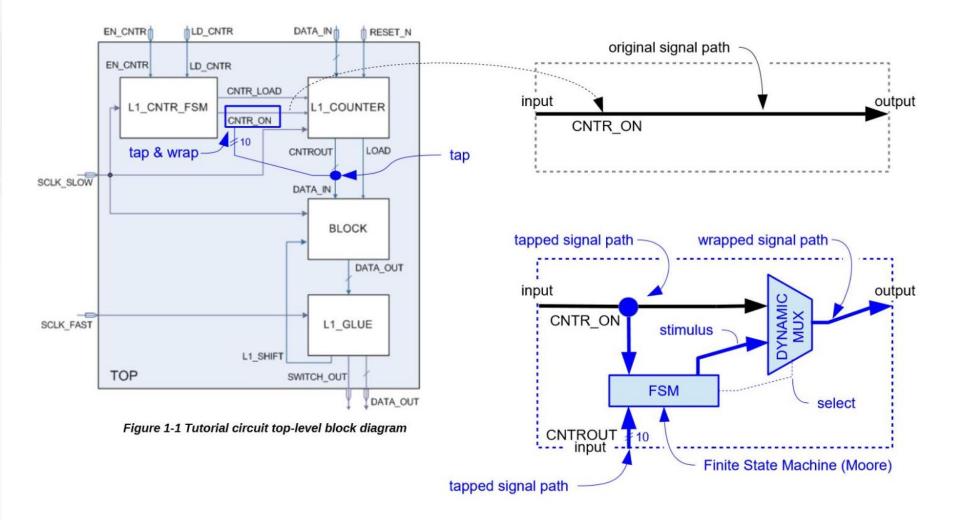

## **Typical Circuit with SbV Instruments Added**

## **Reconfiguration Circuit Example**

### **Sawblade Ventures, LLC**

## Cyber Security with Sawblade Ventures Small, distributed, integrated HARDWARE

## **END of Presentation**

Contact Sawblade Ventures, LLC:

https://sawbladeventures.com

6001 West William Cannon Dr. Ste 203A

Austin, Texas 78749

512-291-2168