## AY-3-8910/8912 PROGRAMMABLE SOUND GENERATOR DATA MANUAL

ARCHITECTURE

OPERATION

INTERFACING

MUSIC GENERATION

SOUND EFFECTS GENERATION

ELECTRICAL SPECIFICATIONS

TABLE OF CONTENTS—PAGE 2

FEBRUARY 1979

General Instrument Corporation and its book is subject to change without notice.

General Instrument Corporation cannot assume responsibility for the use of any circuits described herein.

## Table of Contents

| 1. | INT   | RODUCTION                                  |     |

|----|-------|--------------------------------------------|-----|

| •  | 1.1   | Description                                | 5   |

|    | 1.2   | Features                                   | 6   |

|    | 1.3   | Scope                                      | 6   |

| •  |       | CHITECTURE                                 |     |

| 2. | AH    | Basic Functional Blocks                    | 7   |

|    | 2.1   | Basic Functional Blocks                    | 7   |

|    |       | 2.1.1 Register Array                       | 10  |

|    |       | 2.1.2 Sound Generating Blocks              | 10  |

|    | 2.12  | 2.1.3 I/O Ports                            | 10  |

|    | 2.2   | Pin Assignments                            | 15  |

|    | 2.3   | Pin Functions                              | 14  |

|    | 2.4   | Bus Timing                                 | 14  |

|    | 2.5   | State Timing                               | 14  |

|    |       | 2.5.1 Address PSG Register Sequence        |     |

|    |       | 2.5.2 Write Data to PSG Sequence           | į.  |

|    |       | 2.5.3 Read Data from PSG Sequence          |     |

|    |       | 2.5.4 Write to/Read from I/O Port Sequence | 1.1 |

| 3. | OF    | PERATION                                   |     |

| -  | 3.1   | Tone Generator Control                     | 18  |

|    | 3.2   | Noise Generator Control                    | 20  |

|    | 3.3   | Mixer Control—I/O Enable                   | 2   |

|    | 3.4   | Amplitude Control                          | 22  |

|    | 3.5   | Envelope Generator Control                 | 2   |

|    |       | 3.5.1 Envelope Period Control              | 2   |

|    |       | 3.5.2 Envelope Shape/Cycle Control         | 2   |

|    | 3.6   | I/O Port Data Store                        | 20  |

|    | 3.7   | D/A Converter Operation                    | 25  |

|    |       | TERFACING                                  |     |

| 4  | . IIV | Introduction                               | 33  |

|    | 4.1   | Clock Generation                           | 3   |

|    | 4.2   | Audio Output Interface                     | 3   |

|    | 4.3   | External Memory Access                     | 3   |

|    | 4.4   | Microprocessor/Microcomputer Interface     | 3   |

|    | 4.5   | Interfacing to the PIC 1650                | 3   |

|    | 4.0   | 4.6.1 Write Data Routine                   | 3   |

|    |       | 4.6.2 Read Data Routine                    | 3   |

|    |       | 4.6.3 Read ROM Routine                     | 3   |

|    | 4.7   | Interfacing to the CP1600/1610             | 4   |

|    | 4.1   | 4.7.1 Write Data Routine                   | 4   |

|    |       | 4.7.2 Read Data Routine                    | 4   |

|    | 4.9   | Interfacing to the M6800                   | 4   |

|    | 4.0   | 4.8.1 Latch Address Routine                | 4   |

|    |       | 4.8.2 Write Data Routine                   | 4   |

|    |       | 4.8.3 Read Data Routine                    | 4   |

|    | 4.0   | Interfacing to the 8080 S100 Bus           | 4   |

|    | 4.5   | 4.9.1 Latch Address Routine                | 4   |

|    |       | 4.9.2 Write Data Routine                   | 4   |

|    |       | 4.9.3 Read Data Routine                    | 4   |

|                                          | 5. MUSIC GENERATION                                        |    |

|------------------------------------------|------------------------------------------------------------|----|

|                                          | 5.1 Note Generation                                        | 46 |

|                                          | 5.2 Tune Entry/Playback                                    | 48 |

|                                          | 5.3 Tune Variation                                         |    |

|                                          | 5.3.1 Octave Shift                                         |    |

|                                          | 5.3.2 Key                                                  |    |

|                                          | 5.3.3 Tempo                                                |    |

|                                          | 5.3.4 Chords                                               |    |

|                                          | 5.4 Sound Variation                                        |    |

|                                          | 5.4.1 Relative Channel Volume                              |    |

|                                          |                                                            |    |

|                                          | 5.4.2 Decay                                                |    |

|                                          | 5.4.3 Other Effects                                        |    |

|                                          | 5.5 Applications                                           |    |

|                                          | 5.5.1 Organ Envelope Generation                            |    |

|                                          | 5.5.2 Organ Rhythm Generation                              | 52 |

|                                          | 6. SOUND EFFECTS GENERATION                                |    |

|                                          | 6.1 Tone Only Effects                                      | E9 |

|                                          | 6.1 Tone Only Effects                                      | 50 |

|                                          | 6.2 Noise Only Effects                                     |    |

|                                          | 6.3 Frequency Sweep Effects                                |    |

|                                          | 6.4 Multi-Channel Effects                                  | 56 |

|                                          | 7. ELECTRICAL SPECIFICATIONS                               |    |

|                                          | 7.1 Maximum Ratings                                        | 57 |

|                                          | 7.2 Standard Conditions                                    |    |

|                                          |                                                            |    |

|                                          | 7.3 DC Characteristics                                     |    |

|                                          | 7.4 AC Characteristics                                     |    |

|                                          | 7.5 Package Outlines                                       | φU |

|                                          |                                                            |    |

| List of                                  | Fig. 1 Typical System Diagram                              | 6  |

| (1) 1 (1) (1) (1) (1) (1) (1) (1) (1) (1 | Fig. 2 PSG Block Diagram                                   |    |

| llustrations                             | Fig. 3 PSG Register Array                                  |    |

| แนงแ นแบแง                               | Fig. 4 AY-3-8910 Pin Assignments                           |    |

|                                          | Fig. 5 AY-3-8912 Pin Assignments                           |    |

|                                          | Fig. 6 Variable Amplitude Control                          |    |

|                                          | Fig. 7 Envelope Shape/Cycle Control                        |    |

|                                          | Fig. 8 Detail of Two Cycles of Fig. 7                      |    |

|                                          | Fig. 9 D/A Converter Output                                |    |

|                                          | Fig. 10 Single Tone with Envelope Shape/Cycle Pattern 1000 |    |

|                                          | Fig. 11 Single Tone with Envelope Shape/Cycle Pattern 1100 | 20 |

|                                          | Fig. 12 Single Tone with Envelope Shape/Cycle Pattern 1000 |    |

|                                          |                                                            |    |

|                                          | Fig. 13 Mixture of Three Tones with Fixed Amplitudes       | 31 |

|                                          | Fig. 14 System Block Diagram                               | 32 |

|                                          | Fig. 15 Clock Generation                                   | 33 |

|                                          | Fig. 16 Audio Output Interface                             |    |

|                                          | Fig. 17 External Memory Access                             | 35 |

|                                          | Fig. 18 Microprocessor/Microcomputer Interface             | 36 |

|                                          | Fig. 19 PIC 1650/AY-3-8910 System Example                  | 39 |

|                                          | Fig. 20 CP1600/1610/AY-3-8910 Interface                    | 41 |

|                                          | Fig. 21 M6800/AY-3-8910 Interface                          | 43 |

|                                          | Fig. 22 8080 S100 Bus/AY-3-8910 Interface                  | 45 |

|                                          | Fig. 23 Equal Tempered Chromatic Scale                     |    |

|                                          | Fig. 24 Chord Selection Chart                              |    |

|                                          | Fig. 25 Organ Envelope Generation                          | 51 |

|                                          | Fig. 26 Organ Rhythm Generation                            | 50 |

|                                          | Fig. 27 European Siren Sound Effect Chart                  |    |

|                                          | Fig. 28 Gunshot Sound Effect Chart                         |    |

|                                          | Fig. 29 Explosion Sound Effect Chart                       |    |

|                                          | rig. 29 Explosion Sound Effect Chart                       | 04 |

|                                          |                                                            |    |

## List of Illustrations (cont.)

| 30 | Laser Sound Effect Chart                                       | 55                                                                                                                                                                                                                                                                                                                                                                                         |

|----|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 | Whistling Bomb Sound Effect Chart                              | 55                                                                                                                                                                                                                                                                                                                                                                                         |

| 32 | Wolf Whistle Sound Effect Chart                                | 56                                                                                                                                                                                                                                                                                                                                                                                         |

|    |                                                                |                                                                                                                                                                                                                                                                                                                                                                                            |

| 34 | Analog Channel Output Test Circuit                             | 57                                                                                                                                                                                                                                                                                                                                                                                         |

| 35 | Current to Voltage Converter                                   | 57                                                                                                                                                                                                                                                                                                                                                                                         |

| 36 | Clock and Bus Signal Timing                                    | 58                                                                                                                                                                                                                                                                                                                                                                                         |

| 37 | Reset Timing                                                   | 58                                                                                                                                                                                                                                                                                                                                                                                         |

|    |                                                                |                                                                                                                                                                                                                                                                                                                                                                                            |

| 39 | Write Data Timing                                              | 59                                                                                                                                                                                                                                                                                                                                                                                         |

| 40 | Read Data Timing                                               | 59                                                                                                                                                                                                                                                                                                                                                                                         |

|    |                                                                |                                                                                                                                                                                                                                                                                                                                                                                            |

|    |                                                                |                                                                                                                                                                                                                                                                                                                                                                                            |

|    | 31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41 | 30 Laser Sound Effect Chart 31 Whistling Bomb Sound Effect Chart 32 Wolf Whistle Sound Effect Chart 33 Race Car Sound Effect Chart 34 Analog Channel Output Test Circuit 35 Current to Voltage Converter 36 Clock and Bus Signal Timing 37 Reset Timing 38 Latch Address Timing 39 Write Data Timing 40 Read Data Timing 41 40 Lead Dual In Line Packages 42 28 Lead Dual In Line Packages |

### 1 INTRODUCTION

It is apparent that any microprocessor is capable of producing acceptable sounds with only a transducer if the processor has no other tasks to perform while the sound is sustained. In real world microprocessor use, however, video games need refreshing, keyboards need scanning, etc. For example, in order to produce a single channel of ninth octave C (8372 Hz) the signal needs attention every sixty microseconds. Software required to produce this simple effect and still perform other activities would in the least be very complex if not impossible. In the extreme, random noise requires periodic attention even more frequently.

This need for software-produced sounds without the constant attention of the processor is now satisfied with the availability of the General Instrument AY-3-8910 and AY-3-8912 Programmable Sound Generators.

#### 1.1 Description

The AY-3-8910/8912 Programmable Sound Generator (PSG) is a Large Scale Integrated Circuit which can produce a wide variety of complex sounds under software control. The AY-3-8910/8912 is manufactured in GI's N-Channel Ion Implant Process. Operation requires a single 5V power supply, a TTL compatible clock, and a microprocessor controller such as the GI 16-bit CP1600/1610 or one of GI's PIC 1650 series of 8-bit microcomputers.

The PSG is easily interfaced to any bus oriented system. Its flexibility makes it useful in applications such as music synthesis, sound effects generation, audible alarms, tone signalling and FSK modems. The analog sound outputs can each provide 4 bits of logarithmic digital to analog conversion, greatly enhancing the dynamic range of the sounds produced.

In order to perform sound effects while allowing the processor to continue its other tasks, the PSG can continue to produce sound after the initial commands have been given by the control processor. The fact that realistic sound production often involves more than one effect is satisfied by the three independently controllable channels available in the PSG.

All of the circuit control signals are digital in nature and intended to be provided directly by a microprocessor/microcomputer. This means that one PSG can produce the full range of required sounds with no change in external circuitry. Since the frequency response of the PSG ranges from sub-audible at its lowest frequency to postaudible at its highest frequency, there are few sounds which are beyond reproduction with only the simplest electrical connections.

Since most applications of a microprocessor/PSG system would also require interfacing between the outside world and the microprocessor, this facility has been designed into the PSG. The AY-3-8910 has two general purpose 8-bit I/O ports and is supplied in a 40 lead package; the AY-3-8912 has one port and 28 leads.

# 1.2 ☐ Full software control of sound generation. ☐ Interfaces to most 8-bit and 16-bit microprocessors. ☐ Three independently programmed analog outputs. ☐ Two 8-bit general purpose I/O ports (AY-3-8910). ☐ One 8-bit general purpose I/O port (AY-3-8912). ☐ Single +5 Volt Supply.

#### 1.3 Scope

This Data Manual is intended to introduce the techniques needed to cause the AY-3-8910/8912 Programmable Sound Generator to perform in its intended fashion. All of the programs, programming, and hardware designs have been tested to ensure that the methods are practical rather than purely theoretical.

Although the techniques described will produce powerful results, the range of sounds to be synthesized is so vast and the PSG capabilities so varied that this guide should be viewed merely as an introduction to the applications possibilities of the PSG.

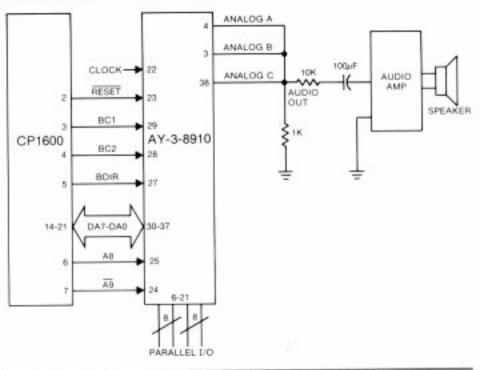

Fig. 1 TYPICAL SYSTEM DIAGRAM

#### 2 ARCHITECTURE

The AY-3-8910/8912 is a register oriented Programmable Sound Generator (PSG). Communication between the processor and the PSG is based on the concept of memory-mapped I/O. Control commands are issued to the PSG by writing to 16 memory-mapped registers. Each of the 16 registers within the PSG is also readable so that the microprocessor can determine, as necessary, present states or stored data values.

All functions of the PSG are controlled through its 16 registers which once programmed, generate and sustain the sounds, thus freeing the system processor for other tasks.

#### 2.1 Basic Functional Blocks

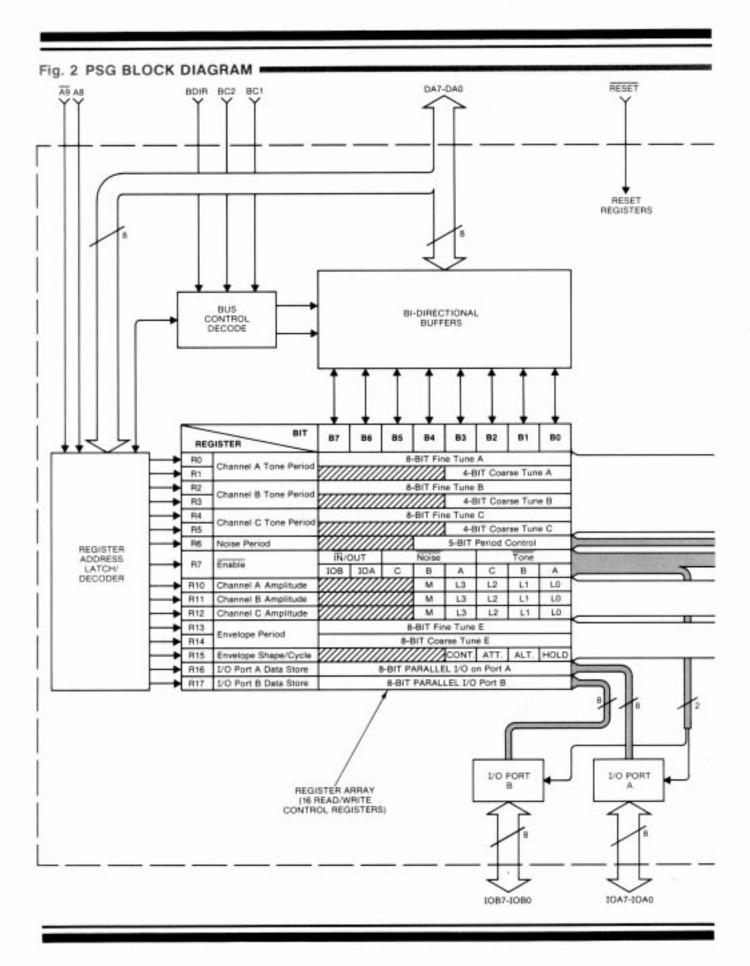

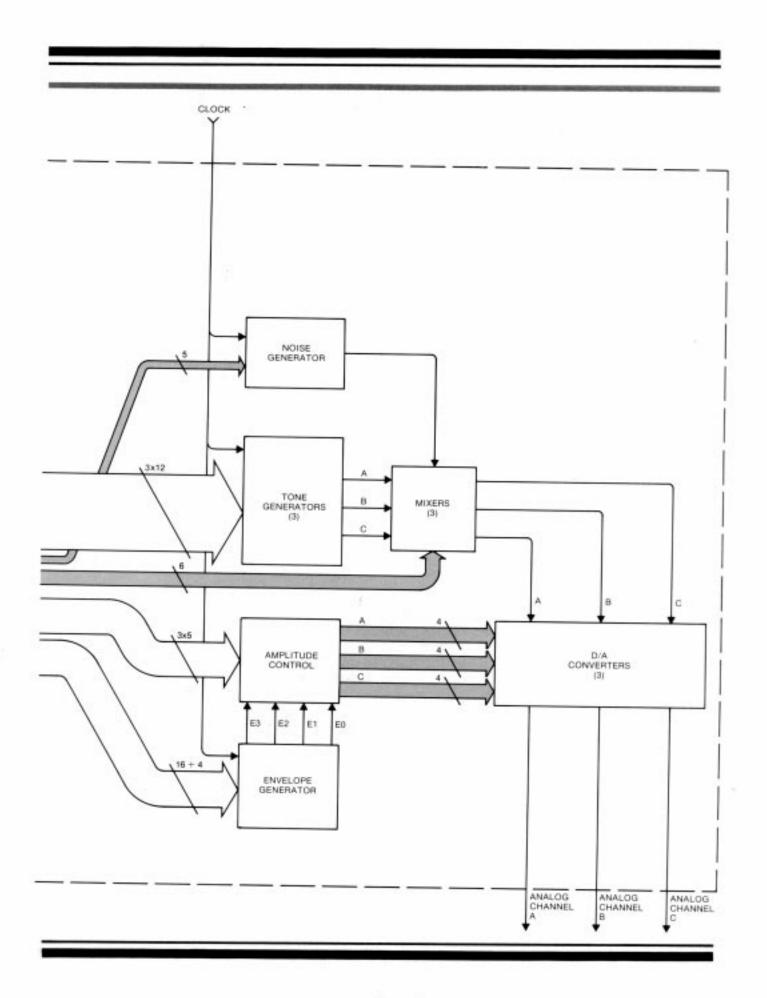

An internal block diagram of the PSG showing the various functional blocks and data flow is shown in Fig. 2.

#### 2.1.1 REGISTER ARRAY

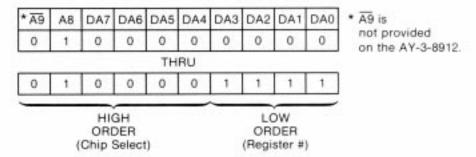

The principal element of the PSG is the array of 16 read/write control registers. These 16 registers look to the CPU as a block of memory and as such occupy a 16 word block out of 1,024 possible addresses. The 10 address bits (8 bits on the common data/address bus, and 2 separate address bits A8 and A9) are decoded as follows:

The four low order address bits select one of the 16 registers (R0-R17<sub>8</sub>). The six high order address bits function as "chip selects" to control the tri-state bidirectional buffers (when the high order address bits are "incorrect", the bidirectional buffers are forced to a high impedance state). High order address bits A9 A8 are fixed in the PSG design to recognize a 01 code; high order address bits DA7-DA4 may be mask-programmed to any 4-bit code by a special order factory mask modification. Unless otherwise specified, address bits DA7--DA4 are programmed to recognize only a 0000 code. A valid high order address latches the register address (the low order 4 bits) in the Register Address Latch/Decoder block. A latched address will remain valid until the receipt of a new address, enabling multiple reads and writes of the same register contents without the need for redundant re-addressing.

#### 2.1 Basic Functional Blocks (cont.)

Conditioning of the Register Address Latch/Decoder and the Bidirectional Buffers to recognize the bus function required (inactive, latch address, write data, or read data) is accomplished by the Bus Control Decode block.

The function of each of the 16 PSG registers and the data flow of each register's contents are shown in context in Fig. 2 and explained in detail in Section 3, "Operation". For reference purposes, the Register Array details are reproduced in Fig. 3.

#### 2.1.2 SOUND GENERATING BLOCKS

The basic blocks in the PSG which produce the programmed sounds include:

Tone Generators produce the basic square wave tone frequen-

cies for each channel (A,B,C)

Noise Generator produces a frequency modulated pseudo

random pulse width square wave output.

Mixers combine the outputs of the Tone Generators and the Noise Generator. One for each chan-

nel (A,B,C).

Amplitude Control provides the D/A Converters with either a

fixed or variable amplitude pattern. The fixed amplitude is under direct CPU control; the variable amplitude is accomplished by using

the output of the Envelope Generator.

Envelope Generator produces an envelope pattern which can be

used to amplitude modulate the output of

each Mixer.

D/A Converters the three D/A Converters each produce up to

a 16 level output signal as determined by the

Amplitude Control.

#### 2.1.3 I/O PORTS

Two additional blocks are shown in the PSG Block Diagram which have nothing directly to do with the production of sound—these are the two I/O Ports (A and B). Since virtually all uses of microprocessor-based sound would require interfacing between the outside world and the processor, this facility has been included in the PSG. Data to/from the CPU bus may be read/written to either of two 8-bit I/O Ports without affecting any other function of the PSG. The I/O Ports are TTL-compatible and are provided with internal pull-ups on each pin. Both Ports are available on the AY-3-8910; only I/O Port A is available on the AY-3-8912.