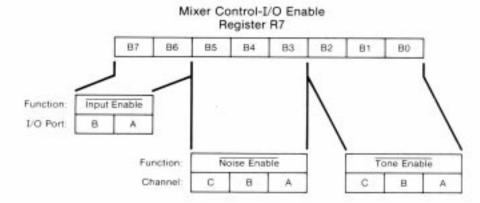

### 3.3 Mixer Control-I/O Enable

(Register R7)

3.3 Register 7. is a multi-function Enable register which controls the three Noise/Tone Mixers and the two general purpose I/O Ports.

The Mixers, as previously described, combine the noise and tone frequencies for each of the three channels. The determination of combining neither/either/both noise and tone frequencies on each channel is made by the state of bits B5--B0 of R7.

The direction (input or output) of the two general purpose I/O Ports (IOA and IOB) is determined by the state of bits B7 and B6 of R7.

These functions are illustrated in the following:

Noise Enable Truth Table:

Tone Enable Truth Table:

| R7 Bits |          |   | Noise Enabled |   |   | R7 Bits |        |    | Tone Enabled |   |   |

|---------|----------|---|---------------|---|---|---------|--------|----|--------------|---|---|

| B5      | B5 B4 B3 |   | on Channel    |   |   | B2      | 817.70 | В0 | on Channel   |   |   |

| 0       | 0        | 0 | C             | В | A | 0       | 0      | 0  | C            | В | A |

| 0       | 0        | 1 | C             | В | _ | 0       | 0      | 1  | C            | В | _ |

| 0       | 1        | 0 | C             | _ | A | 0       | 1      | 0  | C            |   | A |

| 0       | 1        | 1 | C             | - | _ | 0       | 1      | 1  | C            | _ | _ |

| 1       | 0        | 0 |               | В | A | 1       | 0      | 0  | _            | В | A |

| 1       | 0        | 1 | _             | В | - | 1       | 0      | 1  | _            | В | _ |

| 1       | 1        | 0 | _             | _ | A | 1       | 1      | 0  | -            | _ | A |

| 1       | 1        | 1 | _             | _ | - | 1       | 1      | 1  | -            | _ | _ |

|         |          |   |               |   |   |         |        |    |              |   |   |

I/O Port Truth Table:

| R7 | Bits | I/O Port Status |        |  |  |

|----|------|-----------------|--------|--|--|

| B7 | B6   | IOB             | IOA    |  |  |

| 0  | 0    | Input           | Input  |  |  |

| 0  | 1    | Input           | Output |  |  |

| 1  | 0    | Output          | Input  |  |  |

| 1  | 1    | Output          | Output |  |  |

NOTE: Disabling noise and tone does <u>not</u> turn off a channel. Turning a channel off can only be accomplished by writing all zeroes into the corresponding Amplitude Control register, R10, R11, or R12 (see Section 3.4).

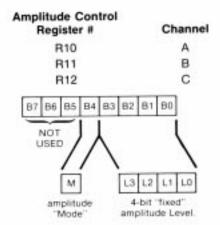

### 3.4 Amplitude Control

(Registers R10, R11, R12)

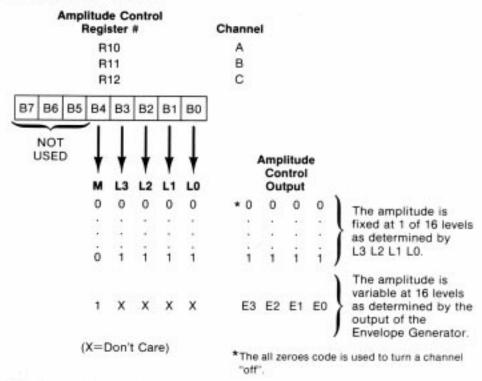

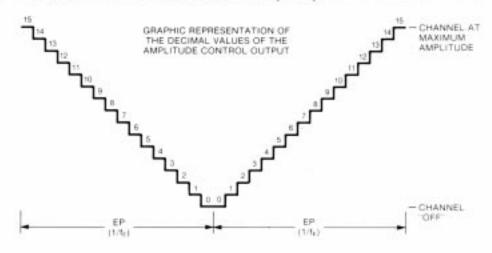

The amplitudes of the signals generated by each of the three D/A Converters (one each for Channels A, B, and C) is determined by the contents of the lower 5 bits (B4--B0) of registers R10, R11, and R12 as illustrated in the following:

The amplitude "mode" (bit M) selects either fixed level amplitude (M=0) or variable level amplitude (M=1). It follows then that bits L3-L0, defining the value of a "fixed" level amplitude, are only active when M=0. When fixed level amplitude is selected, it is "fixed" only in the sense that the amplitude level is under the direct control of the system processor (via bits D3-D0). Varying the amplitude when in this "fixed" amplitude mode requires in each instance the direct intervention of the system processor via an address latch/write data sequence to modify the D3-D0 data.

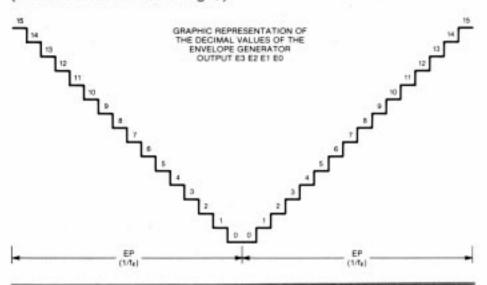

When M=1 (select "variable" level amplitudes), the amplitude of each channel is determined by the envelope pattern as defined by the Envelope Generator's 4-bit output E3 E2 E1 E0.

The amplitude "mode" (bit M) can also be thought of as an "envelope enable" bit; i.e., when M=0 the envelope is not used, and when M=1 the envelope is enabled. (A full description of the Envelope Generator function follows in Section 3.5).

The full chart describing all combinations of the 5-bit Amplitude Control is as follows:

Fig. 6 graphically illustrates a selection of variable level (envelopecontrolled) amplitude where the 16 levels directly reflect the output of the Envelope Generator. A fixed level amplitude would correspond to only one of the levels shown, with the level directly determined by the decimal equivalent of bits L3 L2 L1 L0.

### 3.5 Envelope Generator Control

(Registers R13, R14, R15)

To accomplish the generation of fairly complex envelope patterns, two independent methods of control are provided in the PSG: first, it is possible to vary the frequency of the envelope using registers R13 and R14; and second, the relative shape and cycle pattern of the envelope can be varied using register R15. The following paragraphs explain the details of the envelope control functions, describing first the envelope period control and then the envelope shape/cycle control.

#### 3.5.1 ENVELOPE PERIOD CONTROL (Registers R13, R14)

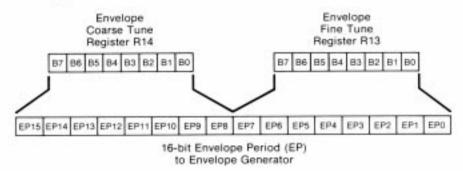

The frequency of the envelope is obtained in the PSG by first counting down the input clock by 256, then by further counting down the result by the programmed 16-bit Envelope Period value. This 16-bit value is obtained in the PSG by combining the contents of the Envelope Coarse and Fine Tune registers, as illustrated in the following:

Note that the 16-bit value programmed in the combined Coarse and Fine Tune registers is a <u>period</u> value—the higher the value in the registers, the lower the resultant envelope frequency.

Note also, that as with the Tone Period, the <u>lowest</u> period value is 000000000000001 (divide by 1); the <u>highest</u> period value is 111111111111111 (divide by 65,535<sub>10</sub>).

The envelope frequency equations are:

(a)

$$f_E = \frac{f_{OLOOK}}{256EP_{10}}$$

(b)  $EP_{10} = 256CT_{10} + FT_{10}$

Where:  $f_E = desired$  envelope frequency

$f_{CLOCK} = input$  clock frequency

$EP_{10} = decimal$  equivalent of the Envelope

Period bits EP15—EP0

$CT_{10} = decimal$  equivalent of the Coarse Tune

register bits B7--B0 (EP15--EP8)

$FT_{10} = decimal$  equivalent of the Fine Tune

register bits B7--B0 (EP7--EP0)

From the above equation it can bee seen that the envelope frequency can range from a low of  $\frac{f_{0.008}}{16.776,980_{11}}$  (wherein: EP<sub>10</sub>=65,535<sub>10</sub>) to a high of  $\frac{f_{0.008}}{256}$  (wherein: EP<sub>10</sub>=1). Using a 2 MHz clock, for example, would produce a range of envelope frequencies from 0.12 Hz to 7812.5 Hz.

To calculate the values for the contents of the Envelope Period Coarse and Fine Tune registers, given the input clock and the desired envelope frequencies, we rearrange the above equations, yielding:

(a)

$$\text{EP}_{10} = \frac{f_{\text{CLOCK}}}{256f_{\text{E}}}$$

(b)  $\text{CT}_{10} + \frac{FT_{10}}{256} = \frac{EP_{10}}{256}$

**Example:**  $f_{\text{E}} = 0.5 \text{ Hz}$

$f_{\text{CLOCK}} = 2 \text{ MHz}$

$\text{EP}_{10} = \frac{2 \times 10^6}{256(0.5)} = 15,625$

Substituting this result into equation (b):

$\text{CT}_{10} + \frac{FT_{10}}{256} = \frac{15,625}{256} = 61 + \frac{9}{256}$

$\text{CT}_{10} = 61_{10} = 00111101 \text{ (B7--B0)}$

#### 3.5.2 ENVELOPE SHAPE/CYCLE CONTROL (Register R15)

$FT_{10} = 9_{10} = 00001001 (B7-B0)$

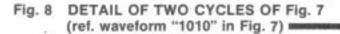

The Envelope Generator further counts down the envelope frequency by 16, producing a 16-state per cycle envelope pattern as defined by its 4-bit counter output, E3 E2 E1 E0. The particular shape and cycle pattern of any desired envelope is accomplished by controlling the count pattern (count up/count down) of the 4-bit counter and by defining a single-cycle or repeat-cycle pattern.

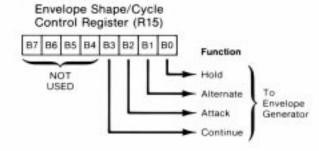

This envelope shape/cycle control is contained in the lower 4 bits (B3--B0) of register R15. Each of these 4 bits controls a function in the envelope generator, as illustrated in the following:

The definition of each function is as follows:

Hold when set to logic "1", limits the envelope to one cycle, holding the last count of the envelope counter (E3-E0=0000 or 1111, depending on whether the envelope counter was in a count-down or count-up mode, respectively).

Alternate when set to logic "1", the envelope counter reverses count direction (up-down) after each cycle.

NOTE: When both the Hold bit and the Alternate bit are ones, the envelope counter is reset to its initial count before holding.

# 3.5 Envelope Generator Control (cont.)

Attack

when set to logic "1", the envelope counter will count up (attack) from E3 E2 E1 E0=0000 to E3 E2 E1 E0=1111; when set to logic "0", the envelope counter will count down (decay) from 1111 to 0000.

Continue

when set to logic "1", the cycle pattern will be as defined by the Hold bit; when set to logic "0", the envelope generator will reset to 0000 after one cycle and hold at that count.

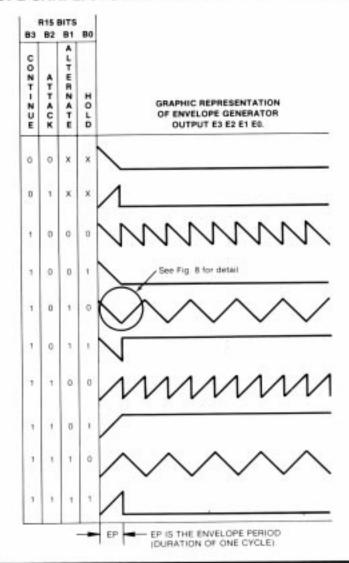

To further describe the above functions could be accomplished by numerous charts of the binary count sequence of E3 E2 E1 E0 for each combination of Hold, Alternate, Attack and Continue. However, since these outputs are used (when selected by the Amplitude Control registers) to amplitude modulate the output of the Mixers, a better understanding of their effect can be accomplished via a graphic representation of their value for each condition selected, as illustrated in Figs. 7 and 8.

Fig. 7 ENVELOPE SHAPE/CYCLE CONTROL =

## 3.6 I/O Port Data Store

(Registers R16, R17)

Registers R16 and R17 function as intermediate data storage registers between the PSG/CPU data bus (DA0--DA7) and the two I/O ports (IOA7--IOA0 and IOB7--IOB0). Both ports are available in the AY-3-8910; only I/O Port A is available in the AY-3-8912. Using registers R16 and R17 for the transfer of I/O data has no effect at all on sound generation.

To output data from the CPU bus to a peripheral device connected to I/O Port A would require only the following steps:

- 1. Latch address R7 (select Enable register)

- 2. Write data to PSG (setting B6 of R7 to "1")

- Latch address R16 (select IOA register)

- 4. Write data to PSG (data to be output on I/O Port A)

To input data from I/O Port A to the CPU bus would require the following:

- 1. Latch address R7 (select Enable register)

- 2. Write data to PSG (setting B6 to R7 to "0")

- Latch address R16 (select IOA register)

- Read data from PSG (data from I/O Port A)

Note that once loaded with data in the output mode, the data will remain on the I/O port(s) until changed either by loading different data, by applying a reset (grounding the Reset pin), or by switching to the input mode.

Note also that when in the input mode, the contents of registers R16 and/or R17 will follow the signals applied to the I/O port(s). However, transfer of this data to the CPU bus requires a "read" operation as described above.

## 3.7 D/A Converter Operation

Since the primary use of the PSG is to produce sound for the highly imperfect amplitude detection mechanism of the human ear, the D/A conversion is performed in logarithmic steps with a normalized voltage range of from 0 to 1 Volt. The specific amplitude control of each of the three D/A Converters is accomplished by the three sets of 4-bit outputs of the Amplitude Control block, while the Mixer outputs provide the base signal frequency (Noise and/or Tone).

Fig. 9 illustrates the D/A Converter output which would result if noise and tones were disabled and an envelope-controlled variable amplitude were selected.

Figs. 10 through 13 illustrate other typical output waveforms.

Fig. 9 D/A CONVERTER OUTPUT (ref. Fig. 6) =

Fig. 10 SINGLE TONE WITH ENVELOPE SHAPE/CYCLE PATTERN 1000 (R0=14<sub>8</sub>, R1=37<sub>8</sub>, R7=76<sub>8</sub>, R12=20<sub>8</sub>, R15=10<sub>8</sub>, all other registers=0)

Fig. 11 SINGLE TONE WITH ENVELOPE SHAPE/CYCLE PATTERN 1100 (R15=148, all other registers same as Fig. 10)